一种具有自适应优化电源抑制比的低静态电流无片外电容LDO

徐 叶,张培勇,李 豪,黄开天

(1.浙江大学超大规模集成电路研究所,浙江杭州 310027;2.南方电网科学研究院有限责任公司信息安全中心,广东广州 510663)

1 引言

稳压器作为电源管理的关键组件,提供了可调节的、稳定的和低噪声的电压[1],广泛应用于片上系统(System on Chip,SoC).线性低 压差稳压器(Low-DropOut regulator,LDO)是稳压器的一种,相比开关电容或开关稳压器来说,具有更好的抗电源噪声能力.根据主极点位置,LDO分为外部补偿和内部补偿两类.前者主极点位于LDO输出端,后者主极点位于LDO内部.内部补偿LDO,也可称为CL-LDO(Capacitor-Less LDO),由于输出端无须负载大电容,因而具有小面积、高集成度的优势.但是,CL-LDO面临着瞬态响应差、稳定性差及低电源抑制比(Power Supply Rejection,PSR)的问题[1,2].

CL-LDO 一般有以下2 种PSR 优化方案.第一种是预调电源电压[3~5].在功率管与电源之间插入一个NMOS 作为共栅(cascode)管,增大电源与LDO 输出之间的阻抗.但这种方式既提高了压差,又增加了面积.第二种是前馈电源噪声消除(FeedForward Ripple Canceller,FFRC)[6~9].在电源和功率管栅极之间提供一条具有适当增益的前馈通路,令功率管栅极电压跟随电源电压,使得输出噪声电流约等于0.该方法不但不会提高压差,而且结构相对简单,可行性强.但PSR 优化效果依赖前馈增益,增益最优值对压差和负载电流以及PVT 变化十分敏感,难以成为一个可靠的PSR 优化方案.

基于传统的FFRC,文献[10]提出一种电流模式的FFRC(Current-mode FFRC,CFFRC),不使用额外的电压加法电路,因此降低了功耗,减小了复杂度.但功率管栅极阻抗极小,其主极点位于LDO 输出端,不适用于CL-LDO.文献[11]提出一种负电容电路(Negative Capacitance Circuit,NCC),使得在功率管栅极因寄生电容耦合的电源噪声与电源噪声一致,从而消除LDO 输出端的噪声电流.但其负电容最优反馈增益依赖数字调节,灵活性不够,同时片上电容为10 pF,面积不够理想.

FFRC 前馈通路最优增益与NCC 负电容最优反馈增益会受功率管工作状态影响,针对该问题,有学者提出一些自适应增益机制.文献[12]提出一种面向CLLDO的一种可适应电源噪声消除方式(Adaptive Supply-Ripple Cancellation,ASRC).ASRC将电源噪声自适应地注入功率管衬底中,不需要像FFRC 那样添加额外的加法电路.但其自适应电路较为复杂,并且由于ASRC 中有个比例缩小的功率管拷贝管,静态电流与负载电流成正比.文献[13]同样利用比例缩小的功率管拷贝管,生成一个比例缩小的栅漏寄生电容(Cgd)补偿电流,经过电流放大器等比例放大后注入功率管栅极.由于电路中存在许多中高频极点,所以该补偿电流只在中低频段(<4 MHz)有效.另外,该方式忽略了功率管的漏体寄生电容与漏源电导,由后续的PSR 分析可知,当功率管处于线性区时,该参数对PSR 的优化起到了关键性作用.上述自适应增益方案均使用了比例缩小的功率管拷贝管,当负载大电流时,存在静态电流过大的问题.

针对上述PSR 优化方案存在的面积大、功耗高、结构复杂等问题,本文提出一种适用于CL-LDO 的PSR 自适应优化方案.该方案无需功率管拷贝管,具有低静态电流的优势;通过监测功率管工作状态,对前馈补偿电流进行动态调节,更具灵活性.本文基于此方案,采用0.11 μm CMOS工艺实现了一种高PSR的CL-LDO,具有面积小、功耗低、PSR自适应调节等优点.

2 PSR分析与优化

电源与LDO 输出之间有多条路径,使得电源噪声耦合到输出端,从而限制PSR.图1 为以PMOS 为功率管(Mpass)的LDO 电源-输出噪声耦合路径图,一共有3条主路径[13]:(1)误差放大器(Error Amplifier,EA);(2)功率管栅源寄生电容(Cgs);(3)功率管的漏体寄生电容(Cdb)与漏源电导(gds).前2 条路径的电源噪声先耦合到Mpass栅极,再被Mpass跨导(gm)放大并转化成噪声电流.为方便小信号分析,将寄生电容拆分为2个对地分电容和2 个压控电流源,并画出LDO 小信号等价模型,如图2所示.

图2 LDO小信号等价模型

暂不考虑虚线框中的PSR 优化模块(PSR Enhancer),得到PSR方程如下所示:

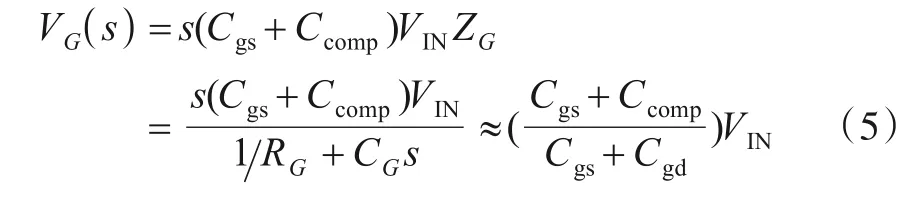

为优化PSR,电源噪声通过各路经耦合到LDO 输出端的噪声电流应尽量小.现考虑PSR 优化模块(图2虚线框),即在Mpass栅极添加一个与频率相关的补偿电流,即压控电流源为补偿电容.补偿后的电源-Mpass栅极噪声电压公式如下是局部反馈,其影响体现在环路增益中;考虑路径2,忽略路径1 对PSR 的影响[13];RG足够大,可忽略;CP相对Cgs和Cgd来说过小,可忽略[13]):

补偿后的路径2电源-输出噪声电流公式如下:

路径3 电源-输出噪声电流公式如下(该噪声电流存在一个零点,处于1 GHz 以上,中低频段为gds主导,故忽略sCdb):

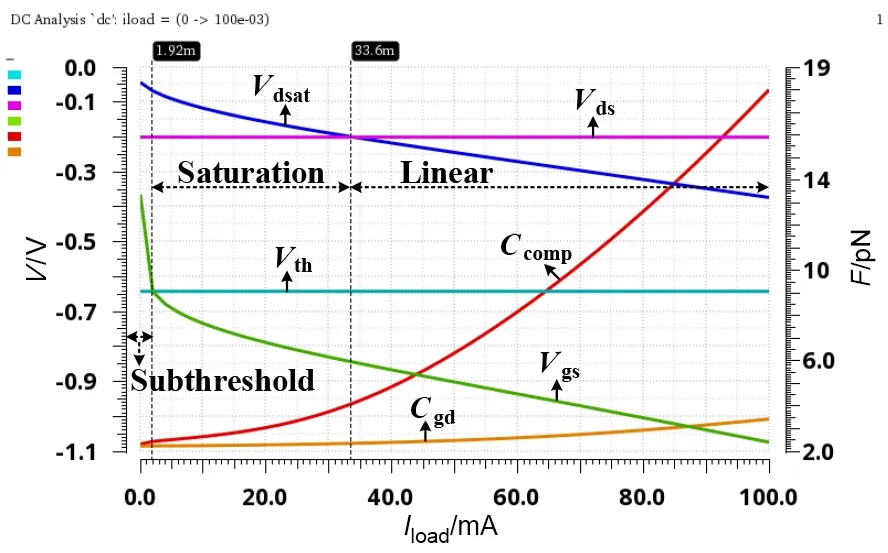

如令Ccomp满足(8)式,PSR 将进一步优化.图3 为Mpass的Cgd,Vdsat,Vds,Vgs与Ccomp随负载电流变化曲线图.当Mpass在亚阈值(Subthreshold)区和饱和(Saturation)区时,Ccomp变化不大;当Mpass进入线性(Linear)区后,Ccomp增长速率变快.图4 为Mpass在不同Vdrop下,Ccomp随负载电流变化曲线图.由图4 可知,Vdrop越大,Mpass越容易趋向于饱和,Ccomp变化越小.因此,Ccomp与Mpass工作状态有关.假如能够判断Mpass的工作状态,再对Ccomp进行动态调节,使其接近于理想值,就能进一步优化PSR.

图3 Mpass 的Cgd,Vdsat,Vds,Vgs 与Ccomp 随负载电流变化曲线图(Vdrop=200 mV,Vth=-640 mV)

图4 Mpass在不同Vdrop下,Ccomp随负载电流变化曲线图

3 结构与实现

LDO 主要由主模块(Core)、PSR 优化模块(PSR Enhancer)和瞬态响应优化模块构成.

3.1 主模块

图5 为LDO 主模块原理图,包括push-pull 放大器(Push-Pull Amplifier)、功率管以及基准源缓冲器(Reference Buffer).本设计采用push-pull 放大器作为LDO的反馈放大器.该结构具有静态电流小、压摆率高,以及稳定性高(输出阻抗小)的优点[14,15].但在文献[14]的结构中,存在最小负载电流限制和低环路增益的问题,后者限制了PSR.文献[16]在文献[14]的基础上,增加一对复制的差分共栅MOS 管,以提高放大器的跨导,从而增加LDO 的环路增益.本设计以文献[16]的结构为基础,做了一些修改,旨在提高环路增益.

图5 LDO主模块原理图

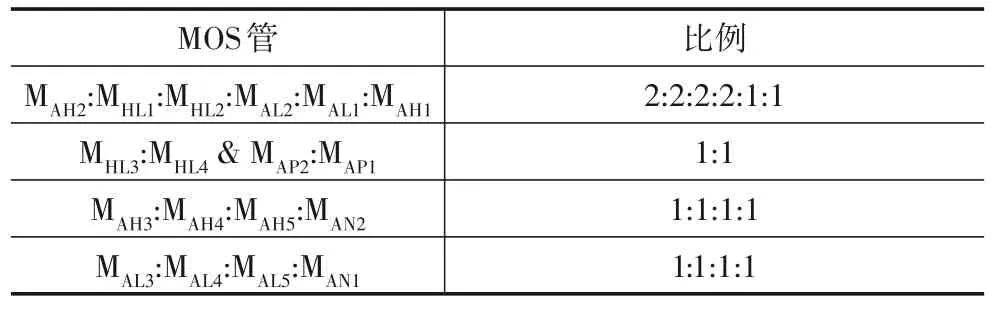

为驱动80 mA 负载电流,同时考虑到面积,且功率管一般允许大电流下工作在线性区,将Mpass的宽长比设置为9 600 μm/0.3 μm.综合上述分析,push-pull 放大器MOS管的比例如表1所示.

表1 push-pull放大器MOS管比例表

图6 为LDO 主模块开环交流响应.当负载电流为100 μA(最差情况)、1 mA、20 mA、40 mA和80 mA时,相位裕度分别为42°,72°,81°,85°,88°.

图6 LDO主模块开环交流响应图(Cload=100 pF)

3.2 PSR优化模块

如第2 节所述,Mpass栅极添加一个频率相关的补偿电流sCcompVIN,可优化LDO 中频PSR.为实现该补偿电流,有2点需要解决的问题.

(1)精确可靠的电流放大电路(Current Amplifier Circuit,CAC).从第2 节可知,在最坏情况下,Ccomp最优值大于10 pF.大电容不仅意味着大面积,而且会产生更低频的极点,衰减优化性能.因此,需要一个精确可靠的无低频极点的CAC,既能放大中低频电流,又不会引入过大的误差电流.文献[13]中CAC 由放大器与电阻组成,虽可精确控制放大倍数,但额外的电阻也增加了电路噪声和面积成本.

(2)自适应动态调节的电流增益.最优Ccomp与Mpass工作状态有关,所以其电流增益需要依据Mpass工作状态,并做出动态调节.在文献[13]中,PSR 的优化只考虑了Mpass的Cgd,所以采用等比例缩小的功率管拷贝管来生成动态可调的前馈补偿电流.但上下偏置电流的失配,会产生较大的直流偏移和交流失配,限制放大精度.这将引入额外的小信号噪声,且该噪声经过电流放大器放大之后,将严重影响LDO 直流工作点和PSR 优化效果.

3.2.1 电流放大电路

设Ccomp=kCvar,其中k为电流放大增益.Ccomp最大值为13 pF(负载电流80 mA).考虑面积、精度以及极点问题,设k值为50倍,Cvar可调,最大值为260 fF.

CAC 共分为2 级(Stage1 和Stage2),分别放大20 倍和2.5 倍,共放大50 倍.两级放大结构均采用差分对称[17,18]的结构.图7、图8 分别为电流放大电路Stage1和Stage2 原理图.Stage2 采用了对称的电流镜结构,以减小直流失配.

图7 电流放大电路Stage1原理图

图8 电流放大电路Stage2原理图

为在达到指定放大倍数的同时,不增加静态电流,Stage1 使用了电流转电压(Current-to-Voltage,I-V)转换器和电压转电流(Voltage-to-Current,V-I)转换器[18]来替代电流镜[17].电源噪声通过跨导增益增强电路(Transconductance Gain Enhancer,TGE)耦合到NX2点,再通过作为MBN6耦合到NX3点(MBP6和MBP7栅端).接着从N1点注入,经过工作在线性区的MBN6,转换成电压vN2(s)=ro,BN6(sCvarvin),ro,BN6为MBN6等效电阻.然后vN2(s)被作为共源极的MBP9放大转换成电流istg1(s)=gm,BP9ro,BN6(sCvarvin),gm,BP9为MBP9跨导.最终Stage1 电流的放大倍数k1=gm,BP9ro,BN6.

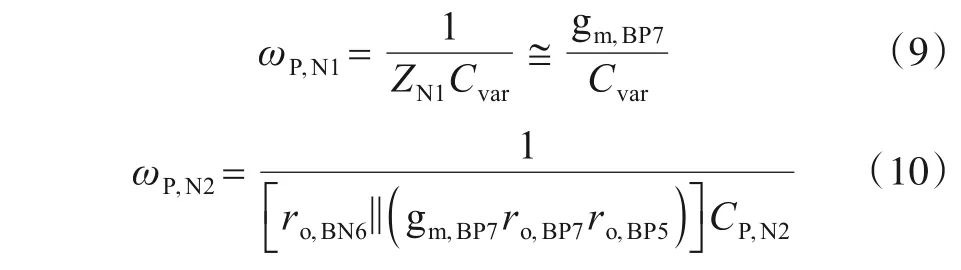

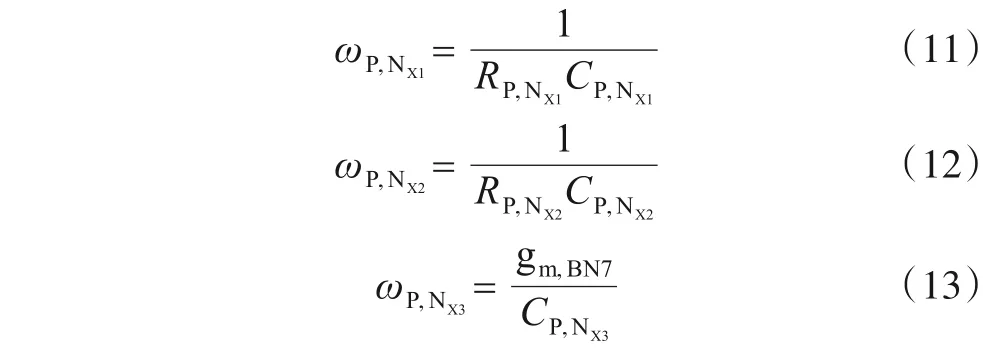

不考虑TGE,右侧电路N1和N2处有两个极点:

其中,ZN1为N1处的输入阻抗,gm,BP7为MBP7的跨导,ro,BP7和ro,BP5分别为MBP7和MBP5的等效电阻,CP,N2为N2处的寄生电容.为使得补偿电流在中频有效,ωP,N1和ωP,N2必须位于10 MHz 及以上频率处.令MBN6工作在线性区,减小ro,BN6,可使ωP,N2推至高频.对于ωP,N1来说,最简单的方式是提高偏置电流以提高gm,BP7,但会增加功耗[17].因此需要一个TGE,提高跨导,减小ZN1,将ωP,N1推向更高频.与文献[17]不同,本设计将Cvar放在与NX2对称的N1处,由于NX3与MBP7的栅极相连,所以TGE 效果是相同的.同时TGE 环路稳定性不受Cvar大小影响.图7 左侧虚线蓝框为所设计的TGE 电路.为避免产生低频极点,运算跨导放大器(Operational Transconductance Amplifier,OTA)采用以NMOS 作为输入对管,差分输入单端输出的一级运放.

在OTA和MBP6之间,插入一级SF作为缓冲级,目的是为了降低NX1处的电位,以满足MBP6的输入共模范围.从NX1,NX2到NX3形成一个环路,共有3 个极点如下所示:其中,CX1和RX1分别为NX1点的频率补偿电容和电阻.图9 为PSR 跨导增益增强电路的开环交流响应图.频率补偿前相位裕度为12°,频率补偿后相位裕度为76°.式(16)为跨导增益放大之后得到的zN1.其中,gOΤA为放大器跨导.在低频下,zN1缩小了倍.为在高频处保持低阻抗,RX1与CX1应尽可能小.

取Cvar=300 fF(最坏情况Ccomp=15 pF),对CAC 进行交流仿真.图10 为电流放大电路的交流仿真图.CAC在10 Hz到10 MHz下可以正常放大,放大倍数为49.在低频直流处有小的直流偏移误差,极高频处由于ZN1增大,CAC失效.

图10 电流放大电路交流仿真图(Cvar=300 fF)

3.2.2 PSR动态调节电路

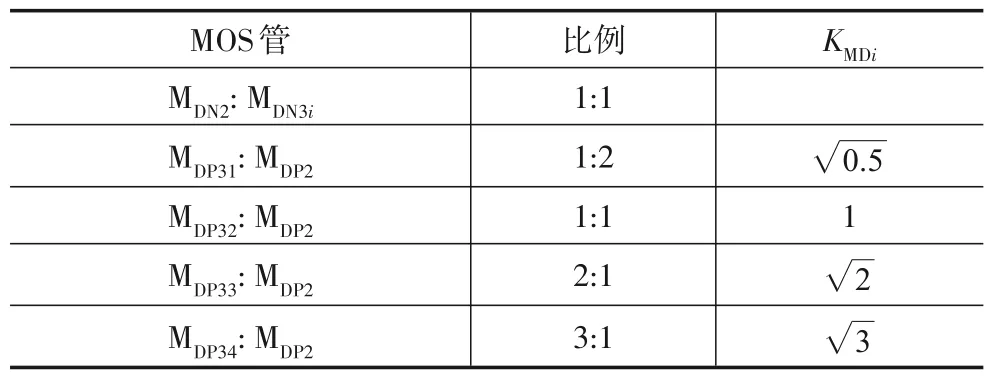

由图3 可知,Ccomp最优值在亚阈值与饱和区变化小,在线性区增长速率加快.设Mpass工作在线性区与饱和区边缘,临界点如下所示:

由式(17),易推得式(18)~(20):

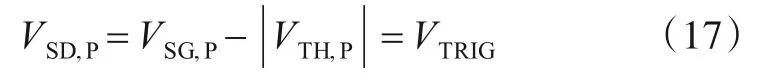

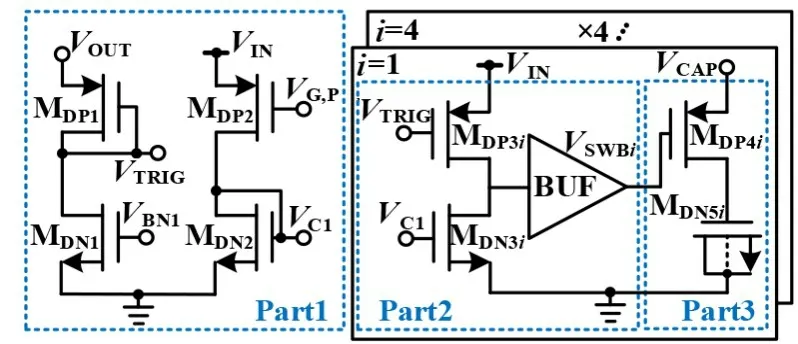

其中,VSD,P,VSG,P和|VΤH,P|分别代表Mpass的源漏电压、源栅电压和阈值电压绝对值;ΔVΤRIG,G表示VTRIG与VG,P之间的差值,差值越大,说明Mpass偏离饱和区越远.但在集成电路设计中,电压差比电流差更难获得.所以,本设计利用单级共源放大器,实现简单的电压转电流功能,降低设计复杂度.图11 为PSR 动态调节电路原理图.将Part2 和Part3 作为整体进行多组并联,可实现Mpass的多段工作区间.本设计中并联数为4,i表示并联序号.

图11 PSR动态调节电路原理图

(1)Part1:提取VTRIG

MDP1源端接LDO 的输出端VOUT,其沟道长度与Mpass相同,工作在线性区与饱和区临界点,令VGS,DP1≈VΤH,DP1≈VΤH,P.最 终MDP1输出电压为VOUΤ-|VΤH,DP1|≈VΤRIG.

(2)Part2:生成临界开关信号VSWBi

MDP2和MDP3i作为共源级,MDP2和MDP3i栅极输入分别为VG,P与VTRIG,流过MDP2与MDP3i的电流如下式所示:

表2 PSR动态调节电路部分MOS管比例表

图12 Ccomp,VG,P和f(KMDi)随负载电流变化曲线图(VIN=2 V,VOUT=1.8 V)

(3)Part3:Cvar可调电路

图11 中MDP4i为PMOS 开关,MDN5i为MOS 电容,4 组拷贝阵列共同构成Cvar,VCAP为CAC 的输入端.采用MOS 电容,一方面因为优化PSR 对Cvar精度要求不高,另一方面可节省面积.当Mpass进入新的状态区间时,VSWBi会转变高低电平,开启或关闭MDP4i,动态调节Cvar.经过计算及仿真,MDP5i寄生电容值如下表3 所示,其中MDN50为初始Cvar.

表3 MDP5i寄生电容值表

设Mpass进入第四区间(Phase4),即VSWB1,2,3=0,50Cvar=9 pF.实际设计的Ccomp比图12中的7.5 pF要大,因为考虑到要优化整个区间,所以接近于Phase 4 中间点的Ccomp值.

3.3 瞬态响应优化模块

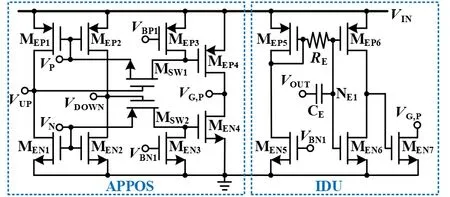

CL-LDO 采用push-pull 放大器结构,虽具有低功耗的优点,但瞬态响应依然较差.本模块结合辅助电路[19](Assistant Push-pull Output Stage,APPOS)和基于反相器的动态单元[20](Inverter-based Dynamic Unit,IDU),旨在提高响应速度,减小过冲或下冲电压.图13 为瞬态响应优化模块的原理图.其中VP,VN,VG,P与图5 主模块各输出端口对应.

图13 瞬态响应优化模块原理图

左侧为APPOS.一般情况下,VUP为低电平,VDOWN为高电平.以负载电流减小为例,LDO 输出电压VOUT上升,经过LDO 环路,VP下降,使得Mpass栅极电容充电电流增加.APPOS 检测到VP下降,拉高VUP,开启MSW1,使MEP4栅极与VP短接,增大Mpass栅极电容充电电流,提高Mpass栅极电压,减小其漏电流.待VOUT稳定后,MSW1再次关闭,不耗静态电流.

右侧为IDU.与文献[20]不同,仅用一级放大器,减小VOUT的下冲电压.耦合电容CE作为小信号高通通路,RE用来隔离MEP5与MEP6的栅极信号.IDU 通过CE将VOUT的下降信号耦合到NE1,接着经由MEP6与MEN6反向放大后输入到MEN7的栅极,从而动态增加Mpass栅极电容放电电流.

4 测试结果与分析

本文所提出的CL-LDO 采用0.11 μm 的CMOS 工艺设计与实现.CL-LDO 芯片封装照片如图14 所示.芯片总面积为0.026 mm2,不包括负载电容、PAD 及测试电路.CL-LDO 输出电压为1.8 V,输入电压范围为2~3.3 V.

图14 CL-LDO芯片封装照片

图15(a)和(b)分别为LDO 的PSR 和瞬态响应测试设置.对于PSR 测试,采用Bias Tee 注入电源噪声.输入正弦信号峰峰值为100 mV,频率范围为1 kHz~10 MHz,由信号发生器(型号33500B)产生,注入到Bias Tee 的AC 端;输入直流偏置为2 V,由电压源(型号PWS2185)提供.其中负载电流由NPN 电流镜提供;Cload为100 pF 负载电容.输入和输出信号皆由频谱仪(型号SSA 2032X)测量.对于瞬态响应测试,CS被添加到LDO 输入端,用于滤去输入信号的噪声.输入输出信号由示波器(MSO-X 3024A)测量.

图15 LDO测试设置

图16展示了在不同压差下静态电流随负载电流的变化曲线.在测试中,LDO的静态电流为输入端总电流减去负载电流.由图可见,当压差为200 mV 时,负载电流从0变化到80 mA,最大静态电流为55 μA.曲线上存在尖峰电流,这与PSR 优化电路中动态调节电路有关(见图12).尖峰意味着此时IMDP2=IMDP3i,两管均处于饱和态,消耗电流增加.

图16 CL-LDO在不同压差下静态电流随负载电流变化的曲线

图17 为CL-LDO 有 无PSR Enhancer 的PSR 测试对比图.由17(a)可知,在0.1~60 mA 的宽负载电流范围下,使用本文所提出的PSR 优化方案后,PSR 在8 kHz到1 MHz频率范围内均有所优化.在不同负载电流下,PSR 最大优化值为21~37 dB.图17(b)也验证了本设计在不同压差下保持同样的优化效果.CL-LDO瞬态响应如图18所示.图18(a)为负载瞬态响应.负载电流上升时间和下降时间均为500 ns,电流变化为0.1~80 mA;最大过冲与下冲电压分别为200 mV 与245 mV;过冲与下冲回复时间约为3 μs.图18(b)为线性瞬态响应,输入电压为2~3.3 V,上升和下降时间均为1 μs.最大过冲电压为263 mV,恢复时间为1.6 μs;最大下冲电压为240 mV,恢复时间为1.7 μs.

图17 CL-LDO有无PSR Enhancer的PSR测试对比图(Cload=100 pF)

图18 CL-LDO 瞬态响应(Cload=100 pF)图

表4 总结了近年来针对CL-LDO PSR 的优化论文.本文方案可实现中频段的PSR 动态优化.同时,在0.1~80 mA 的宽负载电流范围内,保持较低的静态电流,因此FOM值较优.

表4 CL-LDO主要性能比较表

5 总结

本文采用自适应前馈补偿电流技术,设计并实现了一种具有自适应优化PSR 的小静态电流CL-LDO.其中反馈放大器采用低功耗、高稳定性的push-pull 放大器,避免了复杂的频率补偿电路与片外大电容,减小了面积.此外,在PSR 优化模块中采用无大电阻的差分对称结构的电流放大电路,减小直流偏移误差和面积.而且,在PSR 动态调节模块中未使用传统动态优化的功率管拷贝管,而是通过判断功率管的工作状态对MOS补偿电容做出动态调节,进一步减小了静态电流.电路基于0.11 μm CMOS 工艺,芯片面积为0.026 mm2.流片测试结果表明,当负载电流从0.1 mA 变化到80 mA,最大静态电流为55 μA.PSR 在8 kHz~1 MHz 频率范围内均有所优化.在不同压差和负载电流下,PSR 最大优化值为21~37 dB.得益于瞬态响应优化模块,负载瞬态响应恢复时间为3 μs.最终FOM 值为0.21 m,与同类研究相比有一定优势.实测结果验证了其性能与可靠性,非常适用于低功耗SoC应用.