高吞吐率JPEG2000编码器VLSI设计

吴长坤,张 为,郝亚喆

(天津大学 微电子学院,天津 300072)

随着光电传感器技术的飞速发展,图像探测器获得的图像分辨率越来越高,原始图像由8位灰度图提升为如今的16位灰度图,图像信息虽然变得更加精细,但是每幅图像的数据量也急剧增加[1]。海量的图像数据给存储系统带来巨大压力,同时有限的传输带宽使得数据实时回传变得更加困难。图像压缩是一种有效减少数据量以便更快处理数据的技术[2],因此对图像做实时高质量压缩处理可以有效解决上述问题。

图像压缩的方法有很多,但总体上可以分为有损压缩和无损压缩两种[3]。无损压缩要求图像还原后信息不能有任何的丢失,但往往图像压缩比较小;有损压缩在满足实际应用场景要求的前提下允许图像有一定程度的信息丢失,因此压缩比较高。对于旨在减少数据量的应用来说,高质量的有损压缩无疑是更好的选择。

针对图像的有损压缩,国内外众多学者进行了大量研究。文献[4-5]在现场可编程门阵列板卡上完成了JEPG算法的硬件实现,文献[4]使用标准测试图在26倍的压缩比下得出的峰值信噪比仅为28.89 dB,图像压缩质量较差。文献[6-7]都基于现场可编程门阵列实现了JPEG XR压缩算法,但是吞吐率较低,远远不能满足海量数据的实时压缩处理。ADV212是一款专门用于图像压缩的单芯片JPEG2000编解码器[8],该芯片支持有损压缩和无损压缩,有损压缩吞吐率最高为65 MB/s,但不易于扩展,难以满足特定的功能需求。为了提高图像压缩吞吐率,文献[9]基于JPEG2000算法,提出了一种在GPU上运行的端到端高吞吐率图像压缩编码器架构,但是该架构体积大功耗高,通常安装在嵌入式设备中,应用场景较为局限。文献[10-11]在现场可编程门阵列上实现了JPEG2000算法的高吞吐率设计,其中文献[10]吞吐率提升到了120 MB/s。通过查阅和对比国内外相关文献,目前对JPEG2000算法的研究大都是对其各组成模块进行优化,例如文献[12-15]针对离散小波变换(Discrete Wavelet Transform,DWT)进行了优化,提高了模块的处理速度、减少了内部存储器的使用。文献[16-19]针对位平面编码(Bit Plane Coding,BPC)以及MQ算术编码进行了优化,虽然模块的处理效率得到了改善,但是整体编码速度还有待提高。

为满足海量数据的压缩处理需求,参考现有架构,笔者设计了一种可以兼容处理8位到16位灰度图的高吞吐率图像压缩编码器,编码器采用并-串-并架构进行设计,可并行处理两个8位灰度图像。针对16位灰度图像,将图像分割成两幅8位灰度图并行处理,解决了16位灰度图像的压缩问题;针对大于8位小于16位的灰度图像,编码器对数据高位做补零操作,将像素宽度拓宽到16位处理。同时架构采用优先编码器控制并行模块工作,有效减少了并行处理等待时间,大大提升了硬件处理效率。笔者所设计压缩编码器在Xilinx XC7K480T芯片上进行验证,数据源采用1 024×1 024×16 bit大小的标准测试图,最终测得编码器吞吐率最高可达266.87 MB/s。

1 JPEG2000压缩算法简介

JPEG2000是一种基于小波变换的静止图像压缩标准,于2001年正式发布。JPEG2000既支持有损压缩又支持无损压缩,与传统的JPEG压缩算法相比,压缩性能提高20%以上,且在压缩比很大的情况下,仍然有很好的压缩效果。JPEG2000编码器硬件架构如图1所示,大致分为图像预处理、离散小波变换、量化、最佳截断嵌入码块编码 (Embedded Block Coding with Optimized Truncation,EBCOT)等几部分[20]。

图像预处理包含图像分块、直流电平位移以及分量变换3部分,其中最重要的就是图像分块。在JPEG算法中,图像需要被分割成8×8大小的切片来处理;JPEG2000算法虽然没有规定是否分块,但是为了降低内存消耗以及方便后续编码处理,一般也会把图像分割成若干个小的矩形块,各个矩阵块之间相互独立,这也是本次架构设计的关键。此外由于矩阵块之间存在边界效应,会直接影响图像的重构质量,因此对图像进行合理分块处理意义重大。直流电平位移的作用是去除信号中的直流分量,同时把无符号数据变换成有符号数据,用于后续处理;分量变换是将传统的RGB色域转换到其他的色彩空间,对于灰度图来说,这一步可以省略。

离散小波变换是将图像的有效信息集中到低频子带,子带一般具有统计特性,在进行编码时会有更高的编码效率,更加利于后续的EBCOT处理;量化是将离散小波变换处理后的小波系数进行处理,把系数控制在较高的范围之内,有助于提高整体压缩质量;EBCOT是编码器中最主要的部分,分为Tier1编码和Tier2编码。Tier1编码又分为位平面编码和算术编码,Tier1编码的作用是将量化后的子带信息划分成独立的编码块,之后对每个编码块进行独立的嵌入式编码扫描,再将扫描的结果继续做基于上下文的算术编码,然后得到嵌入式码流;Tier2编码根据设计压缩比,先对码流进行截断,然后做打包处理,最终得到符合JPEG2000压缩标准的码流数据。

2 编码器整体架构优化设计

传统压缩编码器各模块之间是串行工作模式,前后级有严格的使能控制逻辑。在处理典型图像时,EBCOT模块通常是整个编码器中消耗时间最长的模块,消耗时间大约占整体编码消耗时间的80%以上[9],同时在EBCOT模块工作过程中,其他模块均处于等待状态,大大降低了编码器的工作效率。在处理高分辨率、高帧率图像时,如果是简单对整体架构做并行操作来提升编码速度,效率只会进一步降低。通过对典型16位灰度图像的分析,笔者提出了一种兼容处理8位~16位灰度图像的压缩编码器硬件架构,如图2所示。

处理16位灰度图时,预处理完成后把图像分成高8位和低8位两幅图像独立并行处理,根据EBCOT模块处理时间与DWT模块处理时间的差异,高低位处理均采用DWT串行、EBCOT并行的架构进行处理。由于高低位数据包含的数据信息不同,因此高低位处理时EBCOT模块的并行度也不同,高位并行度为m,低位并行度为n。一般情况下m要比n小得多,具体数值由DWT处理效率以及图像矩形块的平均复杂度决定。

合理控制多路并行模块的工作顺序,可以有效提高整体架构的工作效率。当并行度较小时,采用多路选择器控制效率较高;当并行度较大时,多路选择器设计会变得比较复杂,而采用顺序执行方式虽然会降低复杂度,但也会增加未知的等待时间,从而降低编码效率。综合上述分析,当并行度较高时,采用优先编码器对并行模块进行控制。表1是以并行度为10为例的优先编码器真值表。图3为优先编码器结构图。表1中1~10代表10路并行模块。当该路模块空闲时,对应数字为1。本次设计的优先编码器以编号小的编码器优先,即当有多路EBCOT模块空闲时,编号小的模块优先工作。由于图像是按照矩形块的形式处理,因此编码结束后需要对码流按顺序重新组织,组织完成后按高位和低位的顺序依次输出,完成整个压缩过程。同时为进一步加快编码器处理效率,高位处理和低位处理的EBCOT模块可以相互调用,当图像的低位/高位处理完成后,空闲的低位/高位EBCOT模块可以继续对高位/低位图像进行编码处理,输出后的码流缓存到高位/低位处理的存储器中即可。

表1 优先编码器真值表(并行度为10)

3 结果对比与分析

3.1 硬件资源消耗

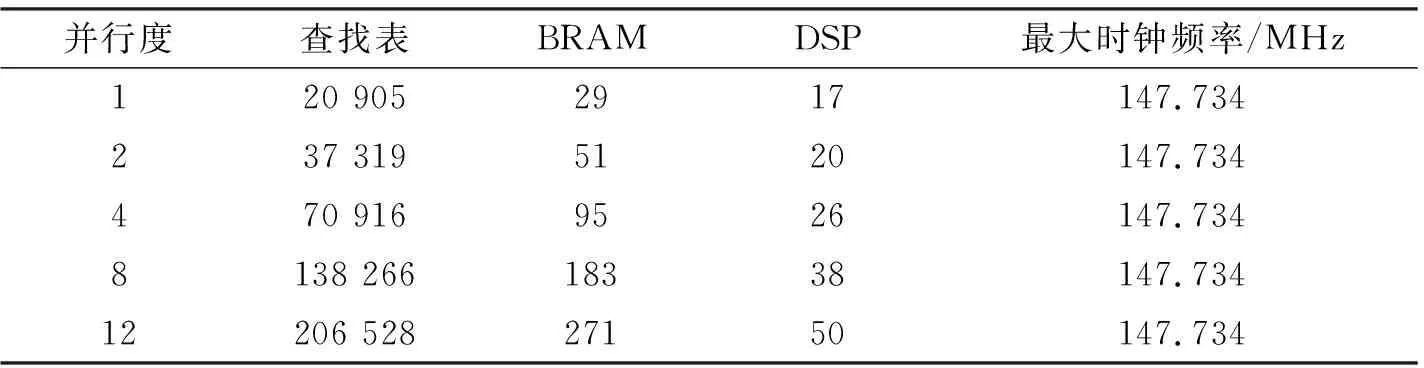

压缩编码器最终在Xilinx XC7K480T芯片上进行设计,表2给出了不同并行度下编码器硬件资源消耗。

表2 不同并行度编码器硬件资源消耗

3.2 性能对比分析

为了测试压缩编码器性能,选取了4帧典型样例图来进行测试,样例图如图4所示。

测试图像大小均为1 024×1 024×16 bit,图中显示的是对16位原始灰度图像做量化处理后的8位灰度图像。通过对典型样例图进行处理得出,当m=11时,高位图像达到最快处理速度;当n=12时,低位图像达到最快处理速度。对于高位图像来说,当并行度超过4时,一路EBCOT模块硬件开销增加的比例,远高于架构处理速度提升的比例。综合分析得出当m=4、n=11时,16位灰度图像的压缩性能与资源消耗最优。

表3给出了在压缩比为5∶1和50∶1情况下,编码器压缩高位图像以及低位图像所消耗的时钟周期数,根据图像大小以及工作时钟频率,计算出编码器的吞吐率。从表中可以看出,同一幅图像在不同压缩比下的吞吐率基本相同。

表3 典型样例图压缩性能(8 bit图像)

压缩完成后使用jasper软件将得到的图像码流数据进行图像重构,最后利用MATLAB软件计算原始图像与重构后图像的峰值信噪比(PSNR)。峰值信噪比的计算公式如下:

(1)

(2)

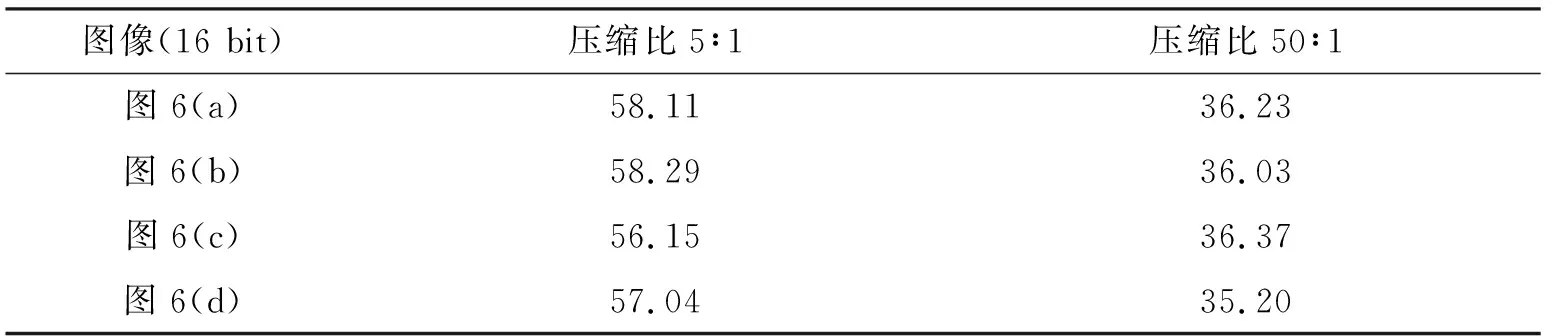

其中,EMSE代表原始图像与重构后图像之间的均方误差,m和n分别代表图像的长和宽,I(i,j)和K(i,j)分别代表重构后图像和原始图像。IMAX代表图像中像素点的最大值,对于8位灰度图来说,最大值为255。通过表3中结果可以看出,在5∶1的压缩比条件下,典型样例图的高位子图峰值信噪比在66 dB以上,低位子图峰值信噪比在41 dB以上;在50∶1的压缩比条件下,典型样例图的高位子图峰值信噪比在47 dB以上,低位子图峰值信噪比在32 dB以上。为进一步验证压缩质量,将重构后的高低位图像重新整合成16位灰度图像,计算与原始16位灰度图像的峰值信噪比。对于16位灰度图来说,式(2)中的IMAX最大值为65 535,计算结果如表4所示。通过表中结果可以看出,在5∶1的压缩比条件下,16位典型样例图的峰值信噪比在56 dB以上;在50∶1的压缩比条件下,16位典型样例图的峰值信噪比在35 dB以上。

表4 典型样例图高低位整合后PSNR值(16 bit图像)dB

为了更直观地对比原始图像与重构后图像的像素差异,使用MATLAB软件将两幅图像各点像素差值进行分析。表5结果表明,在5∶1压缩比条件下,4幅典型样例图高位子图平均99.22%的像素与原图像数值一致,所有像素数值差异不超过5;低位子图平均64.13%的像素与原图像数值一致,97.77%的像素数值差异不超过5。在50∶1压缩比条件下,高位子图平均97.70%的像素与原图像数值一致,99.18%的像素数值差异不超过5;低位子图平均53.86%的像素与原图像数值一致,74.31%的像素数值差异不超过5。

表5 原始图像与重构后图像对应像素差值%

JPEG、JPEG XR以及JPEG2000是目前常用的几种压缩算法,表6给出了基于上述3种压缩算法设计的编码器与笔者所设计编码器的性能对比。

表6 多种压缩编码器性能对比

文献[6]和文献[21]对这3种压缩算法的压缩质量进行了研究。结果表明,对同一图像做压缩时,JPEG XR算法与JPEG2000算法的压缩质量大致相同,均好于JPEG压缩算法。基于Xilinx XC7K480T芯片设计的编码器与文献[5]相比,相似时钟频率下,吞吐率提高了72%以上;与文献[6]相比,最大时钟频率提高了47%以上,吞吐率提高了4倍;与文献[10]相比,笔者设计的编码器并行度为12的架构LUT使用减少了4%,BRAM使用减少约27%,吞吐率提高了40%以上;与文献[11]相比,最大时钟频率提高2.7倍的情况下,吞吐率提高了10.4倍以上。

为避免不同工艺、不同器件对架构效率产生影响,采用文献[15]中的EPI(Energy Per Image)参数比较编码器的硬件效率。EEPI表示处理一幅图像所需要的能耗,计算公式为

EEPI=PPowerTCT,

(3)

其中,PPower代表编码器整体功耗,TCT代表一幅图像的处理时间,EEPI数值越小代表架构性能越好。表6给出了处理一幅1 024×1 024图像各架构的EEPI值,以8位灰度图像为例,与文献[5]相比,EEPI提升了14%以上;文献[11]所提架构EEPI数值与压缩比有关,与其均值相比,性能提高65%以上。

4 结束语

基于JPEG2000算法,笔者提出了一种兼容处理8位~16位灰度图像的高吞吐率压缩编码器,通过各模块间的并-串-并连接设计,使用优先编码器对并行模块进行控制,最终实现了图像的高倍率、高质量快速压缩,有效缓解了海量数据对于传输带宽和数据存储的压力;同时编码器支持多种分辨率图像处理,可根据实际需求灵活调整并行模块并行度。对比已有压缩编码器,吞吐率至少提高了40%以上,有着重要的实用价值。

——编码器