Dither技术在16位奈奎斯特模数转换器中的应用

胡 毅, 李振国, 侯佳力, 冯景彬, 肖澳庆, 国千崧, 胡伟波

(1. 北京智芯微电子科技有限公司 北京 100192; 2. 南开大学, 天津 300071)

0 引 言

Dither技术最早被应用于机械结构中,其在电子信息领域的应用始于数字图像显示技术。1951年,Goodall首次将dither技术应用于视频码脉冲调制中,显著降低了轮廓效应。随后,Robert在Goodell的基础上开展了进一步研究,最早提出了可以应用在模数转换器(Analog to Digital Converter,ADC)的加减型dither技术[1]。它将一个模拟dither噪声引入ADC的输入端,量化完成后在输出端减去相同大小的模拟噪声。如此,这个模拟噪声影响了整个ADC的工作过程,但是,没有影响ADC的量化结果。在dither噪声幅度接近量化步长且服从白噪声分布时,输入端加入的dither噪声与输入信号在统计上相互独立,可以最大限度地降低量化过程中的能量损失[2]。从20世纪90年代开始,应用于ADC的dither技术被广泛研究,多个芯片设计验证了 dither技术可显著改善ADC的量化噪声、差分非线性(Differential Nonlinearity, DNL)、积分非线性(Integral Nonlinearity,INL)等性能[3]。

进入21世纪,芯片的集成度和速率越来越高,随之而来的是高性能ADC对于无杂散动态范围(Spurious Free Dynamic Range,SFDR)更高的要求。Dither技术可以消除ADC量化误差中的谐波等各种非理想因素造成的非线性误差,从概率统计角度减小ADC量化过程中的总体误差,因而近年来被广泛应用[4-10]。

1 传统小幅度的dither技术

传统小幅度dither技术是直接在ADC输入信号中引入dither噪声。为了不影响ADC正常工作状态,在有dither噪声输入情况下,输入信号幅度往往会缩小一点,这样会导致ADC实际有效的动态范围变小[3]。这种传统小幅度的dither技术常用于流水线型ADC。流水线型ADC是由多个低分辨率的子模数转换器(Sub-ADC)组成,在进行量化时几个Sub-ADC同步工作,可以在每个Sub-ADC加入dither,同时对每一位的输出数字码起作用。因此,这种dither技术对于流水线型ADC效果较好,能够显著改善谐波特性。

然而,SAR ADC为串行工作方式,依次从最高位到最低位产生数字码。在对每一位进行量化时,比较器输入电压都是前一位量化完成之后的剩余电压。与高位数字码对应的电压权重相比,加入dither信号幅度相对很小,dither信号导致高位数字码变化的可能性较低[6]。只有在量化特定的电压时,才会对输出结果有影响。基于类似分析,与低位数字码对应的电压权重相比,加入dither信号幅度相对很大,dither信号导致低位数字码变化的可能性较大。经MATLAB仿真验证,在10 000次量化10位精度信号中,传统小幅度dither使得第1~7位输出发生变化的电压点数如表1所示。

表1 传统小幅度dither对于ADC输出的影响

从表1可以看出,传统的小幅度dither技术对于SAR ADC的高位输出影响较小,对SAR ADC的低位输出影响较大。但是,高位输出数字码对应电容失配较大,对谐波分量的贡献也较大;低位数字码对应电容失配较小,对谐波分量贡献也较小。因此,可以认为传统小幅度dither技术对于SAR ADC的SFDR提升作用非常有限。利用MATLAB程序对一个10位精度ADC进行仿真,电容单元失配的1个标准差Sigma为0.5%。如图1所示,与不加dither的情况相比,加入dither对ADC的SFDR影响很小,只提高了0.37 dB。

2 SAR ADC中的改进型dither技术

本文对传统小幅度dither进行了改进,让dither作用在大电容上面,使得大电容失配误差与输入信号无关,从而原有大电容失配所产生的谐波被打散。文献[10]虽然也随机化了大电容,但是,其目的只是为了打乱参考电压能耗与输入信号的关系,以起到保密作用。为了适应这种改进型dither技术在SAR ADC中应用,SAR ADC中电容阵列结构及其控制方法都需要改进。

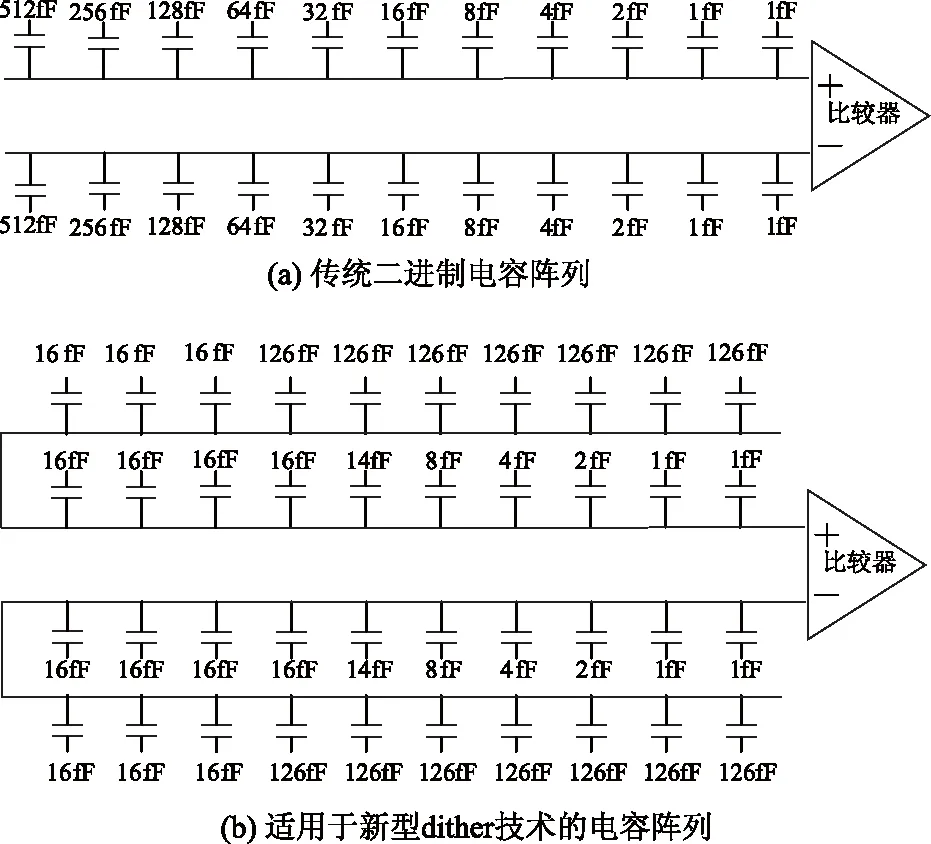

2.1 改进型dither技术ADC的电容阵列

如图2所示,ADC含有一个双端差分输入,带一位冗余的11位电容阵列DAC。传统电容阵列包含二进制的电容单元,其具体组成为512 fF、256 fF、128 fF、64 fF、32 fF、16 fF、8 fF、4 fF、2 fF、1 fF、1 fF。在适用于新型dither技术的电容阵列中,原有DAC中的第1~3位电容(512 fF、256 fF、128 fF)相加后拆分为7个等大的电容单元(7×126 fF),原有电容阵列第4~6位电容(64 fF、32 fF、16 fF)相加后也拆分为7个等大的电容单元(7×16 fF);此外,为了防止高有效位(Most Significant Bit, MSB)电容失配较大,导致后续量化无法将失配抵消,进而导致量化结果错误,将最大电容单元设定为126 fF,而非128 fF,7个2 fF组成一个冗余电容14 fF。即SAR ADC的单侧电容阵列为:126 fF、126 fF、126 fF、126 fF、126 fF、126 fF、126 fF、16 fF、16 fF、16 fF、16 fF、16 fF、16 fF、16 fF、14 fF、8 fF、4 fF、2 fF、1 fF、1 fF。其具体结构如图2(b)所示。为了方便描述,将两组电容重新编号。单位电容为126 fF的7个相同电容分别编号为:126.1、126.2、126.3、126.4、126.5、126.6、126.7。单位电容为16f的7个相同电容分别编号为:16.1、16.2、16.3、16.4、16.5、16.6、16.7。

图2 电容阵列示意图

2.2 改进型dither技术ADC的工作流程

改进型dither技术的工作流程可以分为三个部分:采样信号、打乱单元阵列、大电容重组和量化信号。其中,采样和量化过程与传统模数转换器一致。基于dither技术随机化单元阵列和利用随机化单元阵列重组大电容是该ADC的特有步骤,其发生在采样信号之后和量化信号之前,可以集成在MSB位产生过程中,既不会占用额外的时钟周期,又不会延长信号的量化周期和降低采样频率。

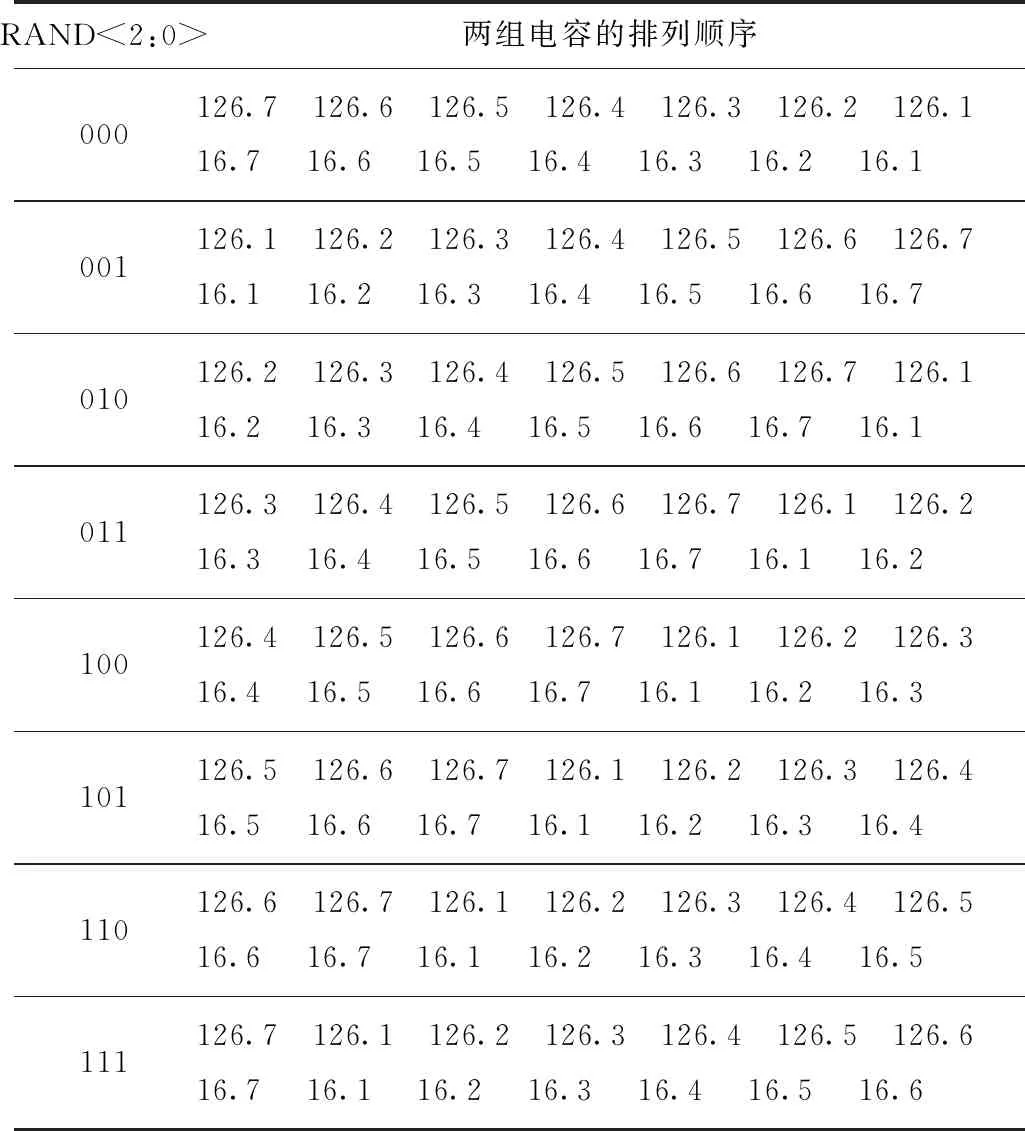

在随机化单元阵列中,二进制的伪随机数发生器会产生三位二进制的随机数,RAND_NUM<2:0>。其对应着7种不同电容排列情况。一般地,1组7个电容存在128种的随机排列情况,但是,为了平衡随机化效果和控制电路硬件成本,设计选了7种情况。如表2所示,三位随机数和单位电容阵列的排列情况固定,但是,三位随机数发生次序是随机,由伪随机数发生器产生。

表2 电容控制码与电容排列的关系

在每次量化一个新信号时,随机数发生器产生一个三位二进制数,确定某一组电容排列方式。在量化之前,7个单位电容单元依次组成三个大小不同的三个电容。也就是说,7个大小为126 fF单位电容中的第1~4个电容连通,受相同控制信号控制,组成大小为504 fF的最大电容,对应着MSB的产生。第5~6个电容连通,受相同控制信号控制,组成大小为252 fF的第二最大电容,对应中第二位MSB的产生。第7个单位电容,单独成为第三最大电容,对应第三位MSB的产生。同理,7个大小为16 fF单位电容也会以类似方式组成3个大小不同电容,依次产生第4~6位。

由于制造工艺误差和版图排布等因素,各个电容大小都不相同,与理想电容值相比都存在误差。这些误差包括系统性误差和随机性误差。系统性误差受特定因素影响,按照某种形式分布;随机性误差服从正态分布。在量化过程中,无论系统性还是随机性误差都会导致量化结果误差,从而影响模数转换器精度。在传统SAR ADC中,电容排布固定,输入信号与误差也会存在固定对应关系,这将导致模数转换器输出结果产生谐波。在带有改进型dither技术的模数转换器中,由于电容阵列的排列顺序是随机的,其电容失配也是随机的,量化电压也存在随机性,量化中产生的误差被随机化,频谱中的谐波被打散,使得ADC的SFDR得到了提升。

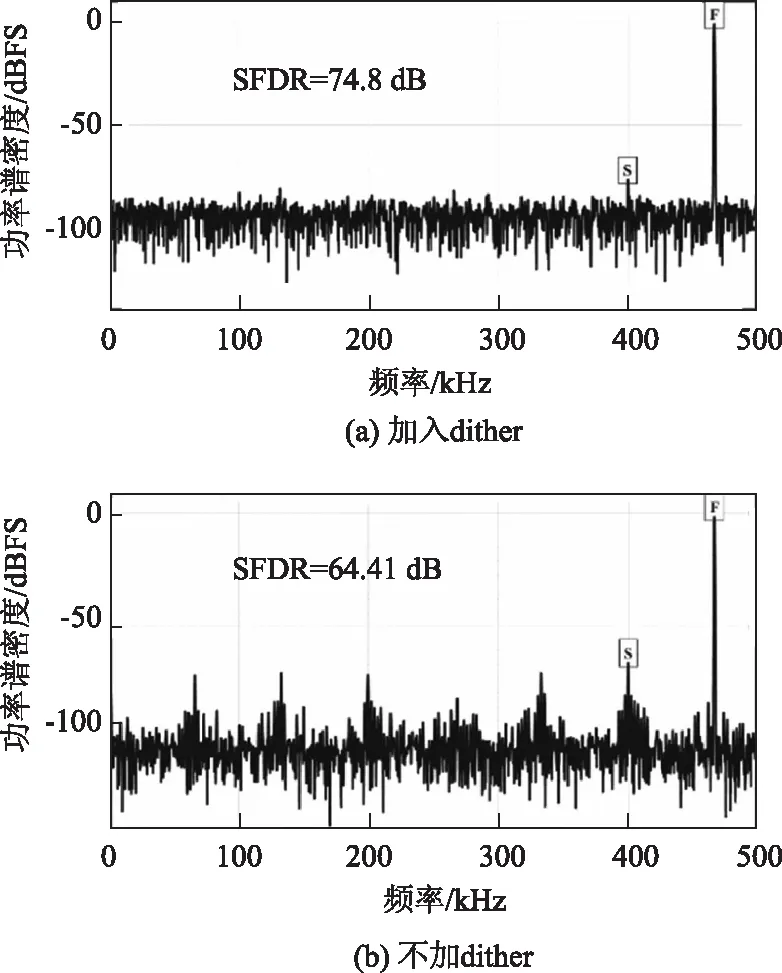

2.3 Dither技术的仿真效果

与图1类似,利用MATLAB程序对一个10位精度ADC进行仿真,电容单元失配的1个Sigma为0.5%。仿真结果如图3所示,频谱中较大的谐波基本被打散,尽管频谱的背景噪声增大,但ADC的SFDR从64.41 dB提升到了74.48 dB,提高了10.07 dB。该结果充分说明了改进型dither技术的有效性,其将大电容排列随机化,从而随机化了大电容失配所带来的误差。

图3 SFDR对比结果

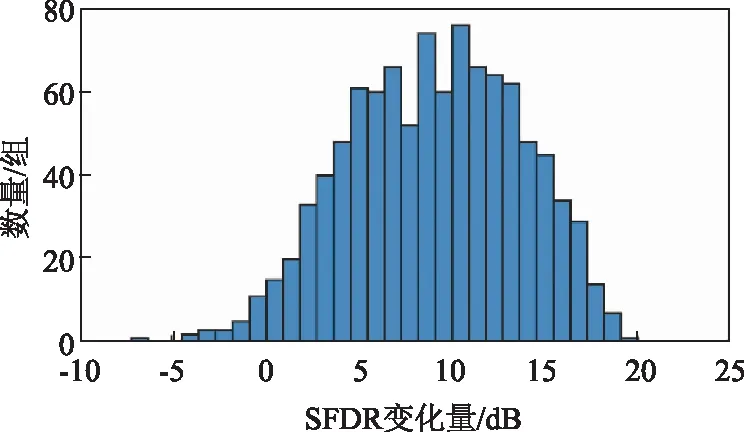

为充分说明改进型dither技术在降低谐波误差方面的作用,利用MATLAB进行1 000次仿真,对比上述仿真中SFDR变化量。其中,电容单元C0失配服从正态分布,标准差为0.5%,仿真结果如图4所示,ADC的SFDR总体上得到了提升,平均提升了9.12 dB;同时,ADC的SINAD平均下降了0.66 dB,相当于增加了7.9%的噪声。这说明dither技术将谐波打散成为噪声,且只引入少量额外噪声。

图4 SFDR变化量的频数分布直方图

为了归纳SFDR下降的各种情况及其内在原因,本文统计了SFDR绝对值与SFDR变化量的相互关系,如图5所示,SFDR的提升与SFDR绝对值呈负相关。当ADC的SFDR达到75 dB左右时,开始出现SFDR变化量为负值的情况。产生该现象的原因在于:当随机产生的电容匹配足够好时,ADC谐波较小,其SFDR被噪声所限制,dither技术对SFDR性能提升基本没有效果,甚至会导致SFDR下降。但是,这种情况只有在理论上存在,在实际电路中,制造工艺、版图绘制等因素中的随机误差和系统误差使得电容单元C0存在失配。

图5 SFDR变化量与SFDR对应的散点图

2.4 ADC其他模块设计

改进型小幅度dither技术主要包括随机序列发生模块、控制信号发生模块,电容选通模块。其中,随机序列发生模块通过线性反馈移位寄存器(Linear Feedback Shift Register,LFSR)产生,可以产生216-1位的伪随机序列,该伪随机数序列周期较长,序列重复一次需要很长时间。如果其所产生谐波在信号频带范围之外,可以近似看作随机数序列。

改进型小幅度dither技术中应用的PN序列通过LFSR产生,与另一种产生方法线性同余法相比,利用LFSR产生PN序列时,没有乘法和求余数的运算,运算量较少,运算速度得到大幅提高。

产生PN序列的线性反馈移位寄存器的结构如图6所示,其由移位寄存器与反馈通路构成。其中,移位寄存器由16个D触发器构成,反馈通路由3个异或门组成,对D触发器的输出进行异或运算,并作为第一组D触发器的输入。线性反馈移位寄存器的特征多项式满足产生最长伪随机序列的条件,产生的伪随机序列周期长度为216-1。

图6 产生伪随机序列的LFSR

需要指出,如果D触发器的初始状态全为0,则后续的输出结果也将全为0,在实际设计中为了避免这种情况,应当设置D触发器的初始状态不全为0。

3 改进型dither在16位ADC实现

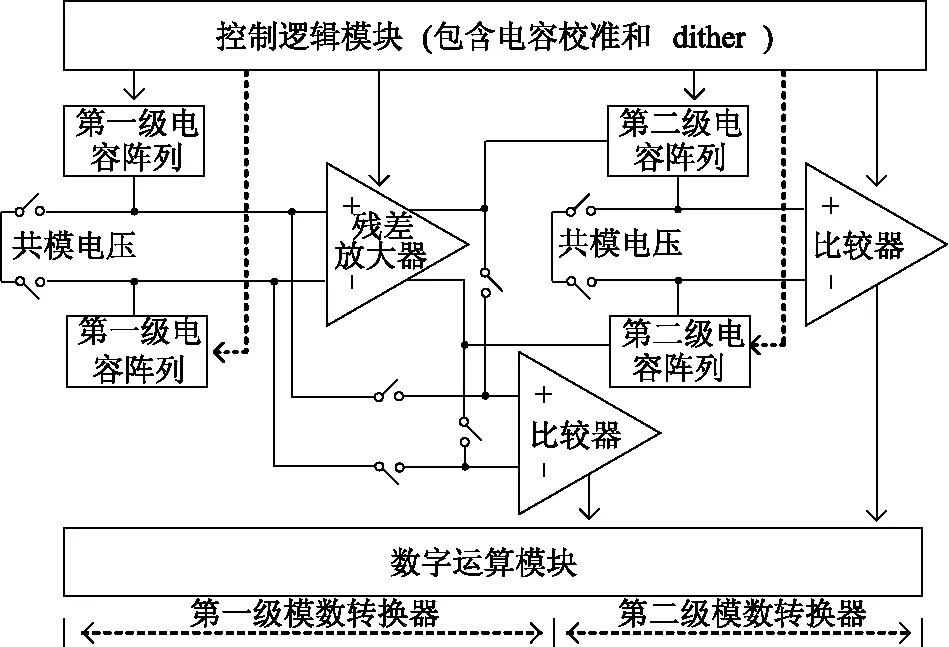

该改进型dither技术被成功应用在一个二级的16位ADC中,其结构如图7所示。其中,每级ADC均为逐次逼近型模数转换器,两级ADC之间使用放大器相连。应用环境没有很高采样频率的要求,这个ADC没有使用流水线技术加速。

图7 带有改进型dither技术的16位ADC结构图

该ADC由第一级ADC,第二级ADC,比较器,精确放大倍数的剩余电压放大器,控制逻辑单元(包含校准和dither等功能)和数字运算单元等组成。其中该改进型dither技术主要应用在第一级ADC的DAC中。具体来说,将第一级 DAC的前14个电容分成2组,每组分成7份。第一组每一份电容由254个单位电容组成;第二组7份dither电容均由32个单位电容组成。ADC控制系统检测到dither 使能信号为高电平时,根据16位伪随机数发生器的判定结果,将同一组7份相同电容再分成3簇,包含份数分别为4,2,1,在之后的逐次逼近逻辑中,它们的下极板依此产生动作。采样开关结束采样,比较器比较完成后将比较结果输送到数字处理单元和逻辑控制单元。逻辑控制单元,根据比较器结果控制对应的电容阵列下极板,让两侧电容上极板相互逼近,然后接着进行下一次比较,循环反复实现逐次逼近逻辑。

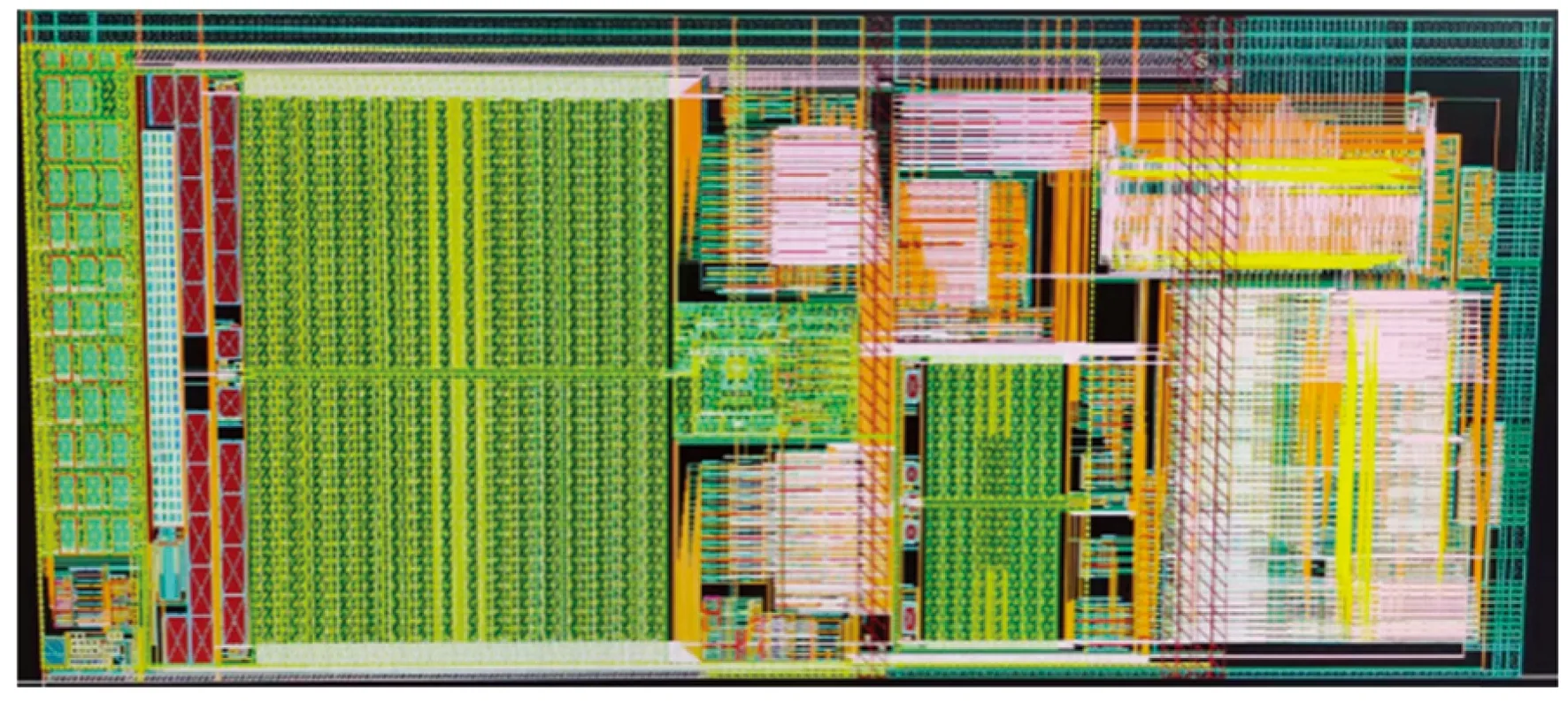

Dither 功能的加入,能有效地提高ADC系统的 SFDR。该功能通过打乱输入信号和电容阵列的直接关系,丰富电容选择路径,将重复出现的电容偏差打散,达到降低谐波信号的目的。实际测试中,电容失配控制在千分之五时,开启dither功能可以使得ADC的SFDR提升10 dB,SNR下降0.1 dB以内。该ADC基于55 nm的CMOS工艺,其版图如图8所示,测试结果如图9所示,使用1.2 V/3.3 V的电源电压。当采样速率在1.25 MSPS,输入信号为107 kHz 的条件下,ADC消耗了3.1 mA电流,得到了94 dB的SINAD。

图8 带有改进型dither技术的16位ADC 的版图

图9 带有改进型dither技术的16位ADC 的SINAD

4 结 语

本文提出了一种应用在SAR ADC的改进型dither技术。通过等量拆解和随机重新组合电容阵列中几个最大电容,直接随机化几个最大电容的失配,从而将ADC输出谐波打散变成噪声。在增加极少噪声的前提下,有效降低了谐波,提升了SFDR。与传统dither技术相比,这种改进型直接作用于大的失配源,大幅度的改变输入信号量化路径。在采样之后和量化开始之前,加入dither技术,且接入步骤能与MSB量化过程融合在一个时钟周期,不会占用额外量化周期和延长量化时间。