高端芯片技术特点及测评难点分析★

王小强,李斌,余永涛,王斌,翁章钊

(1.华南理工大学,广东 广州 510641;2.工业和信息化部电子第五研究所,广东 广州 511370)

0 引言

芯片是电子产品的“心脏”,是信息社会的核心基石,是国家的“工业粮食”。芯片被广泛地应用于通信设备、电脑、消费电子、汽车电子、医疗仪器和机器人,以及工业控制等各种电子产品和系统中,是高端制造业的基石。从2015年起,我国芯片产品进口额超过石油,成为中国第一大进口商品。2020年,我国芯片的进口额攀升至近3 800亿美元,约占国内进口总额的18%。集成电路产业是现代经济社会发展的基础性、战略性和先导性产业,其中采用先进制程及封装工艺、性能高和功能复杂的核心关键芯片,如高性能中央处理器(CPU)芯片、高性能现场可编程门阵列(FPGA)芯片和新一代高性能通信系统级芯片(5G SOC)等高端芯片是集成电路产品的重中之重,代表着一个国家高科技发展水平和未来发展潜力,作为信息产业的核心部件承担着金融、国防、电力和教育等重点行业的数据采集和信息处理任务。

近年来,随着美国加强对以集成电路为代表的中国高科技产业的打压, “高端芯片”成为国内新闻报道和政策文件等媒介的高频词汇。但是, “高端芯片”有何特点,及其测评有哪些难点,行业对此研究分析得较少。因此,本文通过对行业报道较多的CPU、FPGA和5G SoC等典型的高端芯片产品进行分析,总结高端芯片的技术特点,并分析其共性测评技术难点,以期为国内高端芯片的研发、生产和应用等环节的测试评价提供技术支撑。

1 传统集成电路类别概述

随着半导体集成电路设计、工艺技术的飞速发展,集成电路规模日益增大,按集成度来分,半导体集成电路可分为:小规模集成电路(10~100个元件)、中规模集成电路(100~1 000个元件)、大规模集成电路(1 000~100 000个元件)、超大规模集成电路(10万~1 000万个元件)、特大规模集成电路(1 000万~10亿个元件)和巨大规模集成电路(10亿个元件以上)[1]。

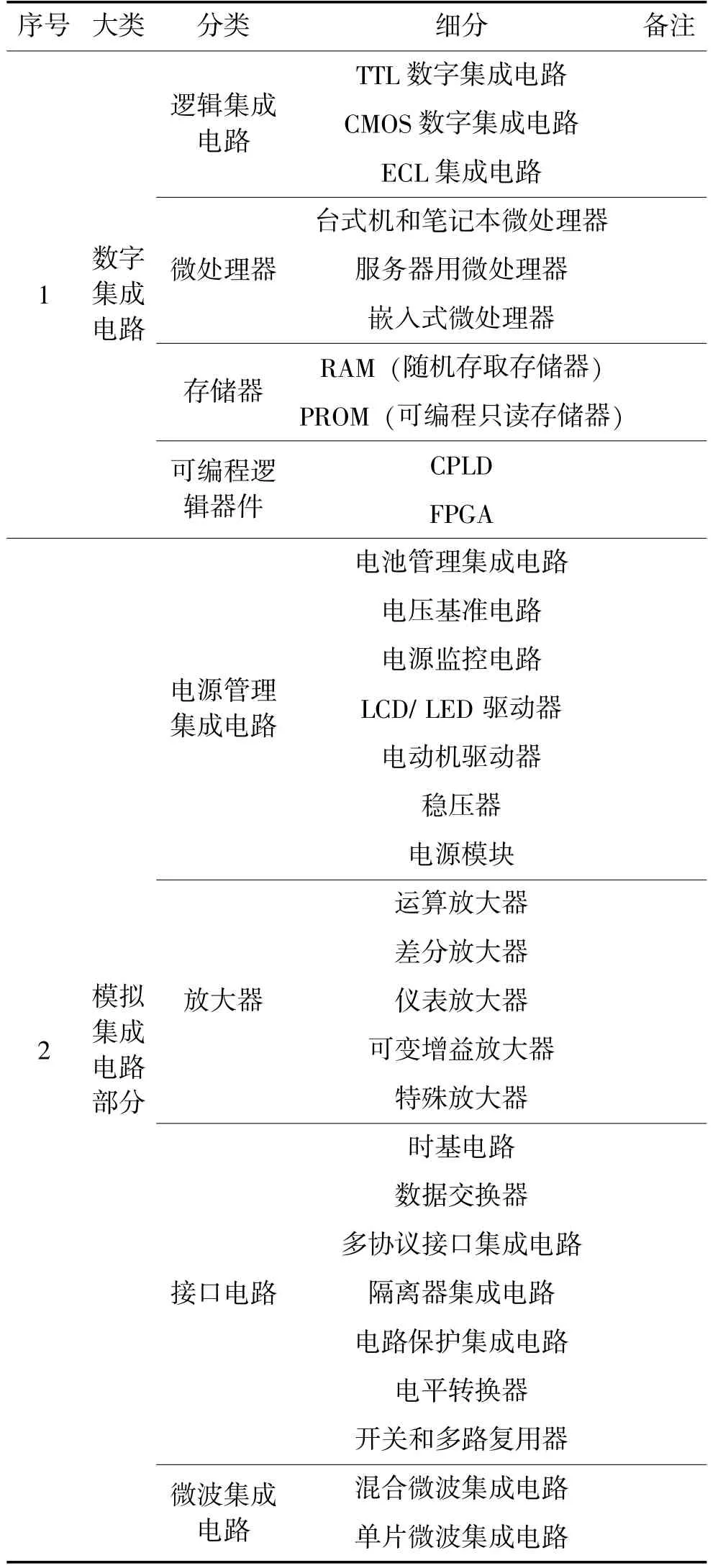

按照处理信号的类型,集成电路分为数字集成电路、模拟集成电路和混合信号集成电路等。其中,数字集成电路分为逻辑集成电路、微处理器、存储器和可编程逻辑器件4个大类;模拟集成电路分为电源管理集成电路、放大器、接口集成电路和微波集成电路4个大类。每个大类又分为若干小类和细类,如表1所示[2]。

表1 集成电路分类(按功能分)

2 高端芯片技术特点分析

不同于传统基于集成度、处理信号类别的分类,高端芯片代表的是高技术应用领域,如新一代移动通信、人工智能和大数据等新兴技术及其应用所需要的核心关键芯片。半导体工艺的进步使得芯片集成度得到进一步的提升,台积电(TSMC)的30.48 cm(12英寸)5 nm工艺已于2019年进行了量产,下一代先进工艺水平也在稳步地推进。根据华为官网报道,麒麟980采用7 nm工艺,单颗芯片集成69亿颗晶体管[3]。

本文选取体现高新技术发展水平的CPU、FPGA和5G SoC等典型的高端芯片产品,依据网络公开的产品关键指标数据进行技术特点分析。

2.1 CPU

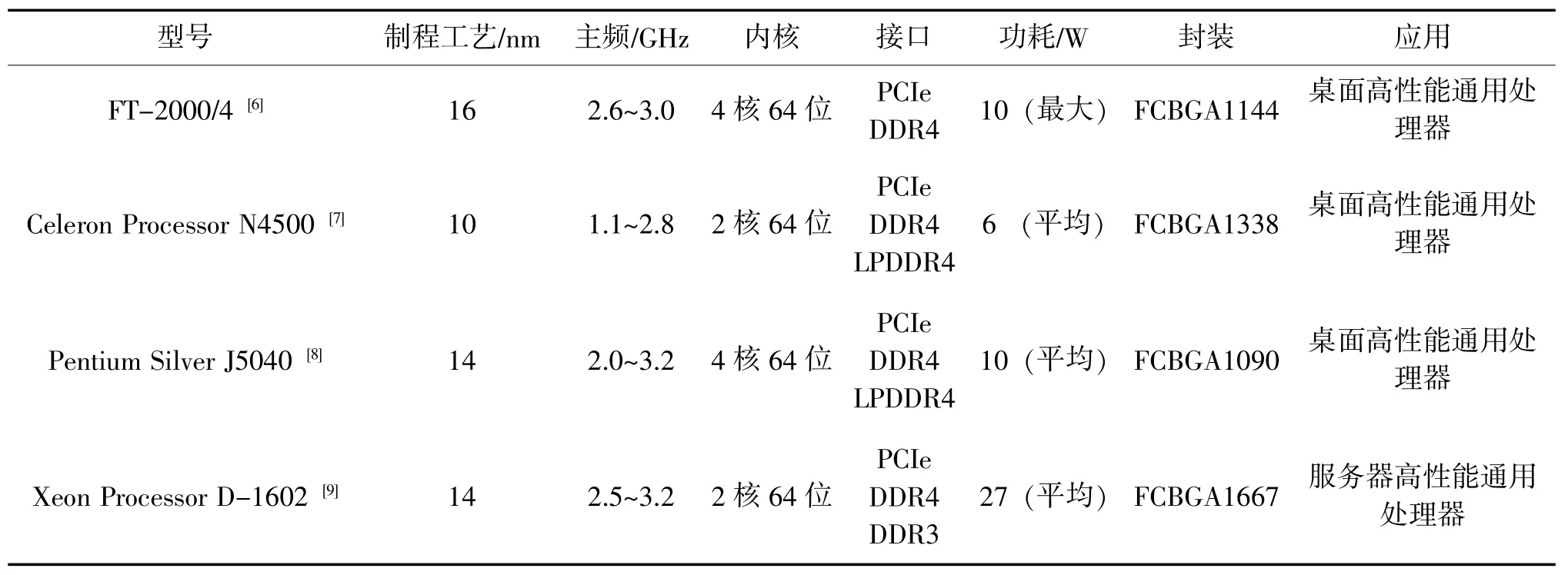

CPU是桌面式计算机、数据服务器等计算机系统的运算和控制核心,是信息处理、程序运行的最终执行单元。典型的CPU产品如图1所示,选取网络公开数据进行整理,得到的国内外典型CPU产品的基本规格及应用结果如表2所示。

表2 国内外典型CPU产品的基本规格及应用

图1 典型的CPU产品图例[4-5]

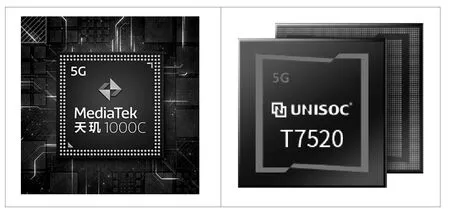

2.2 FPGA

FPGA产品由于其可配置、设计开发周期短等特点,在5G通信、数据中心、消费电子、汽车电子、工业控制和医疗设备等领域具有广泛的应用前景。典型的FPGA产品如图2所示,选取网络公开数据进行整理,得到的典型FPGA产品的基本规格及应用情况。

图2 典型的FPGA产品图例[10-11]

2.3 5G SoC

除了CPU和FPGA等通用高端芯片技术不断地更新换代,随着5G运营环境的不断成熟,基于5G应用的系统级芯片5G SoC(5G System-on-Chip)成为了高端智能手机的标配,典型的5G SoC产品如图3所示。

图3 典型的5G SoC产品图例[14-15]

表3 典型的FPGA产品基本规格及应用

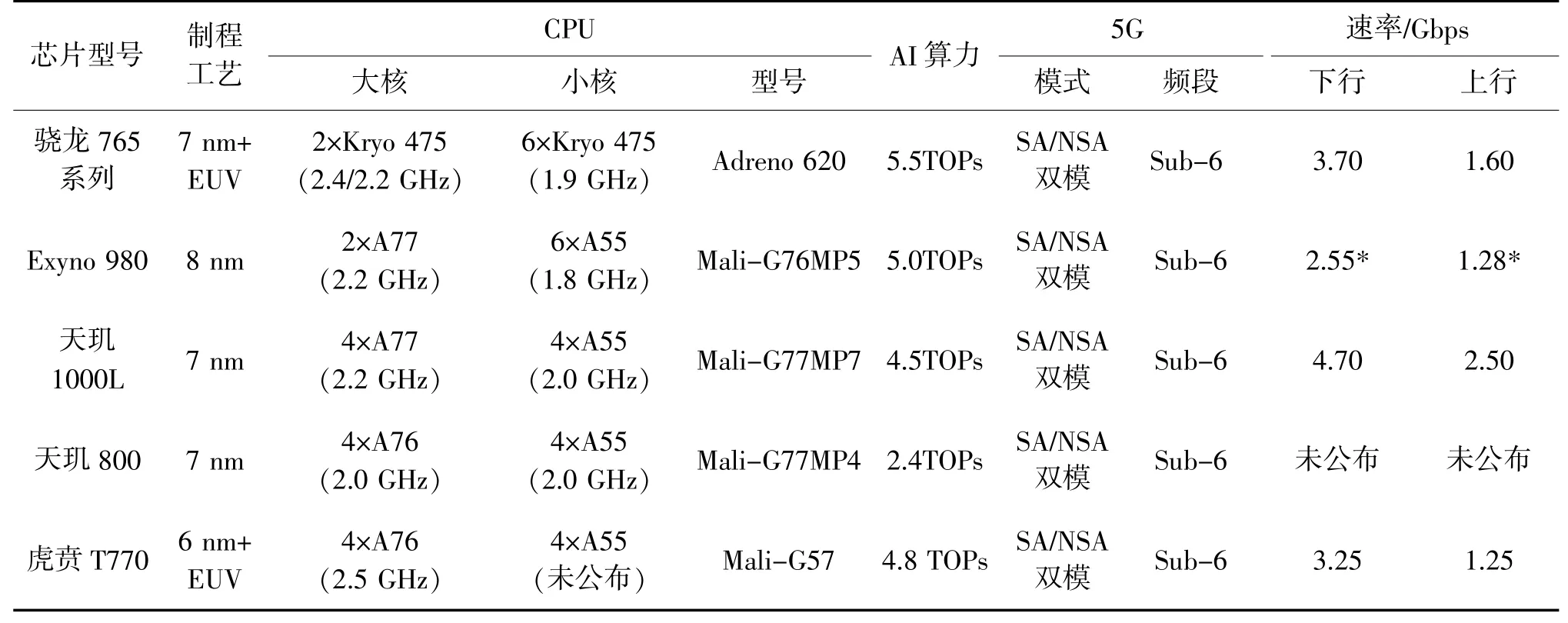

目前市场主流5G SoC芯片的基本规格如表4所示。这些5G SoC芯片采用了先进制造工艺,在保证功耗前提下,其核心关键性能完全满足当前国内外的5G运营环境。

表4 典型的5G SoC基本规格对比[16]

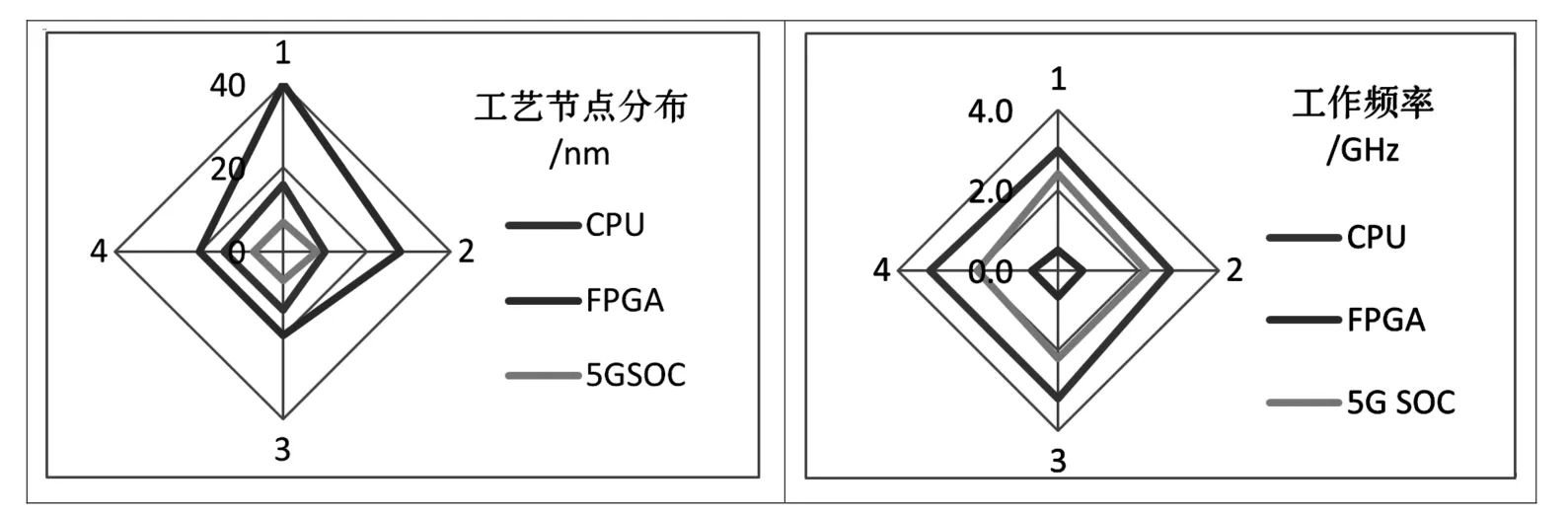

选取CPU、FPGA和5G SoC各4款为目前主流产品的工艺节点、主频等数据进行分析,从图4中可以看到,5G SoC产品采用最先进工艺,普遍采用7 nm制程;CPU紧随其后普遍采用14/10 nm制程;FPGA工艺分布较大,考虑到成本等综合因素,典型的产品主要集中在28/20 nm。

图4 数据雷达图分析

CPU、5G SoC典型产品的主频都在2~3 GHz,FPGA为采用BRAM速度参考比较。3类产品的引脚数都达到了1 000 Pin以上,采用了先进的高密度封装技术。

综合以上数据进行分析,发现高端芯片具有以下特点:

1)工艺制程先进(28、14、7/5 nm以下);

2)工作频率高(主频在2 GHz以上,采用SERDES、PCIE等高速接口);

3)封装工艺先进(WLP/3D/SiP);

4)功能复杂(内核数多,拥有更全面的功能及优异的综合性能等)。

相对于其他集成电路,高端芯片一般具有多功能、强算力、高速、高密度存储和高效的信息处理能力等特点,服务于高端应用市场,在电路系统中扮演最核心的功能角色,一般表现出高集成度、高工作频率和先进封装形式等外化特征。其中,最关键的特点是工艺制程先进。特别是对于数字电路而言,先进制程可以实现更高的集成度,是单片多IP核及实现复杂功能的基础,更小的特征尺寸可以实现更高的工作频率,更高的集成度对封装工艺提出了更高的要求。

3 测评难点分析

高端芯片测评是芯片产业链的关键技术环节,贯穿于设计、制造、封装和应用等全寿命周期,是芯片产品质量保证的关键,也是芯片产业的核心技术和重点保障。随着先进纳米工艺制造技术和集成电路系统朝着高速、高频和高精度等高性能方向发展,高端芯片的先进工艺制程进入10 nm以内,集成规模超过几十亿甚至数百亿,内部结构越来越复杂,功能模块越来越多,其测试项目越来越多、测试难度越来越大,特别是高速信号测试、多层级的综合性能验证、先进封装的可靠性评价,已成为高端芯片行业发展的重要挑战,受到日益增多的关注和研究。

3.1 高速信号传输质量的测试评价

高端芯片性能的提升、高端芯片主频的提升及其内嵌的高速总线给测试带来了新的挑战,主要表现为对信号完整性的要求更为严格。从上述产品指标中可以看到,高端芯片的工作频率越来越高;同时,为了实现和外围的数据交换,大多配有SERDES、DDR等高速传输接口。以目前应用较多的DDR4为例,相对于DDR3,DDR4采用更低的电压和更高带宽,供电电压从1.5 V降到1.2 V,信号速率可达3 200 Mbps。FPGA芯片的SERDES接口可达12.5 Gbps,甚至可以达到32.75 Gbps。在高频率和低电压的条件下对DDR和SERDES信号进行测试,信号完整性的好坏至关重要。

随着传输速率的提高,高速信号链路上的串扰、反射、时钟抖动、接地反弹和电源噪声等效应将愈发严重,测试质量难以保证,如速率为3 200 Mbps的DDR4信号的单一比特位宽仅为312.50 ps。针对高速信号测试难题,需要开展高速信号传输链路建模仿真、高速信号测试板设计、ATE及系统级高速信号测试技术等技术攻关,保障高速信号传输质量及开展高速信号接口协议测试验证、全速条件下的功能性能评估等研究工作。

典型的高速信号测试验证示例如图5所示。

图5 高速信号测试验证示意图

3.2 多层级的综合功能性能测评

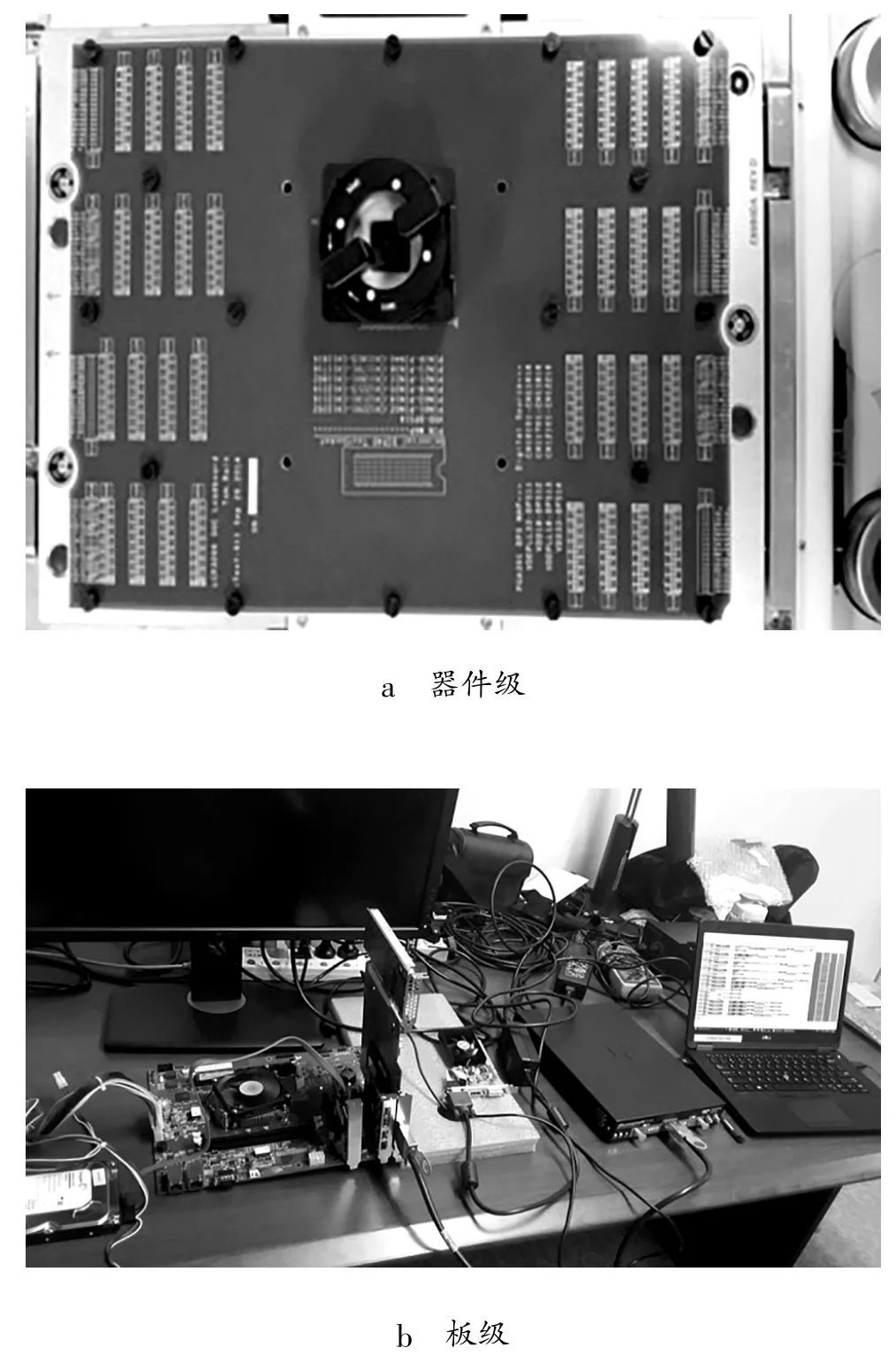

由于高端芯片的芯片集成度更高,传统的FT测试无法对其实现全面的考核,同时芯片的功能更加复杂,需要针对芯片进行多层次的测试验证,才能对其应用可靠性进行全面验证。目前国内高端芯片针对器件级、板级和系统级的验证往往不够全面,缺乏针对基于软硬件协同设计研制的高端芯片的检测手段及方法。

在器件级层面,随着特征尺寸的缩小,高端芯片电迁移(EM)、超薄栅氧化层击穿(TDDB)、热载流子效应(HCI)和负偏置温度不稳定性(NBTI)效应越来越显著,进而影响芯片的可靠性。在板级层面,高端芯片需要与外围元器件共同实现主要功能;同时,由于ATE系统资源的限制,复杂功能的验证无法通过ATE系统得到全面验证,板级测试条件下如何区分外围元器件的影响也至关重要。在系统级层面,高端芯片需要操作系统层面运行各类应用程序及软件,其基于系统级应用的测评更能反映真实应用条件下的各种性能指标。

针对多层级的综合测评难点,重点需要开展基于器件级的电应力及温度应力下的功能性能测评、验证,保障其质量可靠性。在板级,基于最小原型系统,开展极限应力条件下的功能验证,如温度应力、电压频率拉偏等,保障其板级应用可靠性。在系统级,研究基于典型应用场景的高端芯片综合性能测试技术。器件级、板级、系统级的测评图例如图6所示。

图6 器件级、板级、系统级测评图例

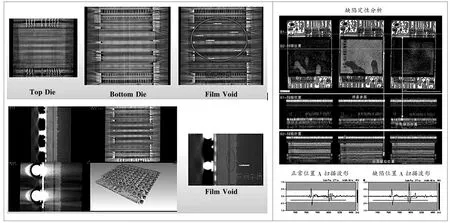

3.3 先进封装质量可靠性评价

随着先进制程工艺与封装工艺的不断提升,高端芯片正逐步地向高密度、低功耗和小型化方向发展。先进封装中涉及如超薄晶圆处理、芯片堆叠、芯片倒装和硅通孔等技术,使得芯片集成度越来越高。另一方面,新封装技术的复杂性使得产品在芯片减薄、芯片贴装和倒装焊等过程中,存在一系列与工艺相关的失效,如芯片开裂、分层、键合线开路或短路等。另外,高端芯片复杂的封装结构和较小尺寸的缺陷特征,对可靠性检测评价手段提出了更高的要求,常规的显微形貌分析技术、声学扫描显微镜检查技术和2D X-ray显微透射技术等已无法满足评价需求,需要引入多模式声扫检查技术、CT透射技术、磁显微缺陷定位技术、同步热发射分析技术和超高精密解剖制样等技术以进一步地实现微纳尺寸的缺陷识别与定位,如图7所示。

图7 三维封装样品3D-Xray/声学扫描检查缺陷检查示意图

4 结束语

本文针对CPU、FPGA、5G SoC等高端芯片产品的公开数据信息进行整理分析,总结了高端芯片所具有的工艺制程先进、性能指标高、封装结构复杂和可靠性要求高等共性特点。通过结合工程经验,分析了高端芯片面临高速信号传输质量测评、多层级综合功能性能测评和先进封装质量可靠性评价等技术挑战及对策,可以为国内高端芯片的研发、生产和应用等环节的测试评价提供重要的技术支撑。