用AD9912实现的多功能低相噪信号发生器

陈少雄 林盛鑫 陈冰儿

(东莞理工学院 电子工程与智能化学院,广东东莞 523808)

信号源设备是电子技术领域一种常用的仪器,在雷达、通信、电子测控等领域有着广泛的应用。随着各行业对信号源性能要求的不断提高,需要达到的频率范围越来越广,并需要有良好的精度和稳定度,传统的信号源已经无法满足当前电子技术领域研究的需求,针对以上需求,频率合成技术逐步形成[2]。

现有大多数的信号发生器是采用直接数字合成(Direct Digital Synthesizer,DDS)技术,支持产生正弦波频率仅有几百千赫。利用DDS芯片AD9912产生频率范围为1 Hz~400 MHz信号源,支持点频和扫频模式,最小频率分辨率可达到1 Hz,最小时间间隔为1 ms,系统支持调幅、调频,分辨率调节。DDS技术是第三代频率合成技术,具有很多频率分辨率高、相位噪声低、科技小、重量轻等优点[3]。

1 直接频率合成技术

1.1 DDS技术的基本原理及结构

如图1所示,DDS主要是由是相位累加器、波形存储器、数模转换器、低通滤波器组成。由奈奎斯特采样定律可知,从正弦信号的相位出发,经过抽样、量化、编码等计算过程,得到一个离散的正弦函数表,存到波形存储器ROM中。DDS内部均为以系统参考时钟为基准同步工作,相位累加器根据频率控制字在系统时钟的作用下,进行线性相位取样,每次取样的值会送入波形存储器ROM中进行寻址,得到该处相位对应的正弦波的赋值,每个正弦波赋值连接起来得到一个模拟的阶梯波,最后将阶梯波送入低通滤波器得到所需频率的正弦波[4]。

图1 DDS的结构框图

1.2 DDS的数学原理

理想正弦波信号S(t)可表示为

S(t)=Asin(2πf0t+φ) ,

(1)

式(1)说明理想正弦信号源的频谱在幅度和初始相位不变的情况下是一条关于f0的谱线。为简化分析,令A=1,φ=0,即

S(t)=sin(2πf0t)=sinθ(t),

(2)

对式(2)的信号进行采样,采样周期为Tc,即离散的波形序列为

S(n)=sin(2πf0n),

(3)

由式(3)可知,连续两次采样之间相位增量为

(4)

(5)

相应的模拟信号为

(6)

(7)

由式(7)分析可知,通过改变频率控制字FTW就可以改变输出频率,DDS输出的分辨率为

(8)

1.3 DDS技术的特点

直接频率合成技术相比于直接频率合成技术和间接频率合成技术有一定的优势。

1.3.1 分辨率较高

由式(8)可知,最小分辨率与相位累加器的位数N和系统时钟有关。可以选择相位累加器位数较高的DDS芯片来实现生成具有较高频率分辨率,而生成波形的相位通常与DDS芯片中的相位累加器的位数有关[6]。ADI公司的AD9912芯片内置48位的相位累加器,一个14位的相位寄存器,在系统的参考时钟为1 GHz的前提下,该DDS的分辨率为

其相位分辨率为

可以看出,DDS的最小频率分辨率可以达到uHz级别,最小相位分辨率也很高,这是间接频率合成技术和直接模拟频率合成技术所无法达到的。

1.3.2 输出频率范围宽

DDS的输出频点数量与N有关,而当FTW=0时,fout=0 Hz;

1.3.3 频率切换速度快

如图1所示,在DDS系统中FTW的传递速度只与系统采样频率fc和DDS系统的长度有关,与频率分辨率无关,如果低通滤波器的频率响应控制在合理范围内,DDS的切换速度可以达到微秒级别。

2 硬件设计

2.1 AD9912模块设计

如图2所示,时钟输入端采用低频率25 MHz晶体震荡器作为输入基准信号,使用AD9912内部锁相环电路,需通过编程控制寄存器0x0020和0x0022,设置反馈分频器的分频模数,得到DDS进行线性相位取样的系统时钟。

图2 AD9912模块电路设计

内部时钟锁相环电路集成分频器、鉴相器、压控振荡器[8],故需设计外接的环路滤波器,而外部环路滤波器的设计会影响锁相环的带宽,压控振荡器的名义增益是800 MHz/V,环路带宽大约在1.6 MHz,电荷泵电流设在250 μA,设计环路滤波器由C55、C56、R5构成。

由于AD9912的输出为差分信号,选用ADT1-1WT作为巴伦电路,进行双端平衡到非平衡信号的转换。

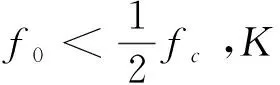

2.2 低通滤波器设计

DDS输出的杂散主要来自DAC非理想特性、分辨率较低等原因,需设计低通滤波器对其进行滤除[9]。滤波器的类型主要分为有源和无源滤波器,有源滤波器中通常有运算放大器等有源器件,由于运算放大器的存在,会使得滤波的频带宽度受到限制,不符合设计的要求。无源滤波器只含有电容、电感、电阻三种元器件,不需要电源供电即可工作,且在高频工作时频带较宽[10]。

通过对几种类型的低通滤波器比较可知,巴特沃思滤波器的过渡带较为平缓,切比雪夫滤波器的瞬态特性较差,而对于给定的通带纹波要求和阶数要求,椭圆滤波器的过渡带很窄,并且下降迅速。具体的电路设计如图3所示,设计一个7阶的椭圆滤波器,截止频率为440 MHz,通带纹<0.1 dB,带外最小衰减为60 dB。

图3 七阶椭圆低通滤波器

3 软件设计

3.1 OLED屏幕驱动

SSD1306点阵屏的分辨率为128*64,每页含有128 byte,共有8页。BS0、BS1、BS2用于选择通信协议,设计驱动OLED屏幕使用的是SPI协议,因此BS0=BS1=BS2=0。

OLED屏幕主要实现在上电时屏幕显示初始化信息,“Singal”“Generator”“Freq:1 Hz~450 MHz”“AD9912-1GHz-V1”。延时后将当前页面刷新,将初始频率、终止频率、扫频时间间隔、扫频步长、幅值信息等显示到新的页面,根据按键控制的信息对数据进行响应的操作。

3.2 AD9912驱动

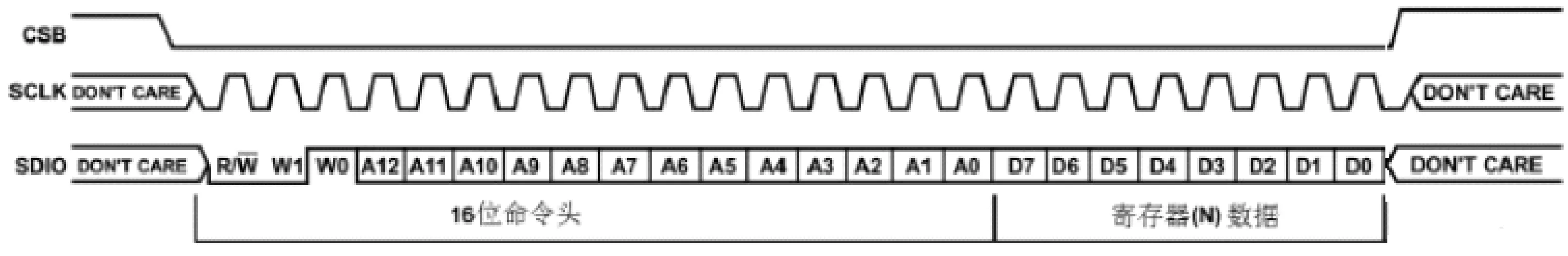

AD9912采用串行控制端口灵活的SPI协议,可配置为一个双向的I/O引脚或两个单向的I/O引脚,所有的串口操作都依赖于DAC系统时钟的存在。系统中采用3线制SPI模式,SCLK为串行移位时钟,SDIO作为数据双向输入输出引脚,CSB为片选信号。

设计中单片机采用内部RC振荡器作为系统时钟,写操作时序如图4所示R/表明该指令是读或写,数据[W1:W0]指明传输数据的长度,R单片机将CS拉低使能AD9912,在时钟上升沿来时发送数据,从最高位起,依次向下传输,直到最低为LSB发送完成。

图4 AD9912写1字节数据

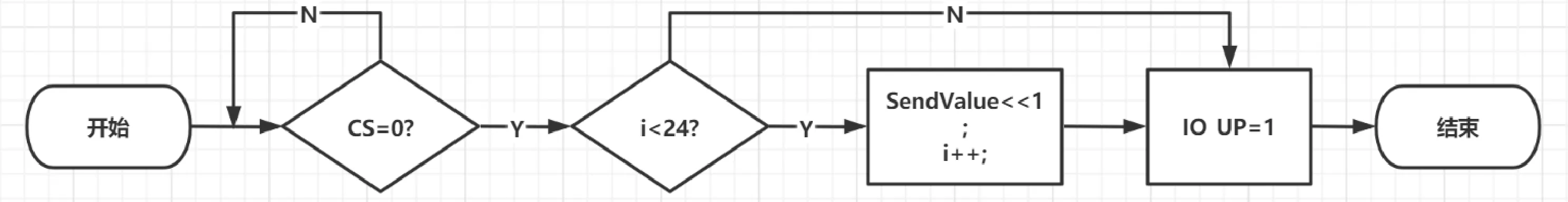

如图5所示,在每个数据传输周期,单片机首先拉低片选信号,将CS置低,待发送的数据为SendValue,其位数为24。待检测到读写位为1时,在每次数据在时钟上升沿写入,将数据的第i位发送到端口缓存器,同时左移1位,i加1,当检测到i不小于24时,表示当前寄存器的值全部写入AD9912,此时数据保存在串行端口缓存器,当更新时钟IO_UPDATA到来时,将端口缓存器的置输入到寄存器中。

图5 写操作数据周期程序流程图

4 实验数据及分析

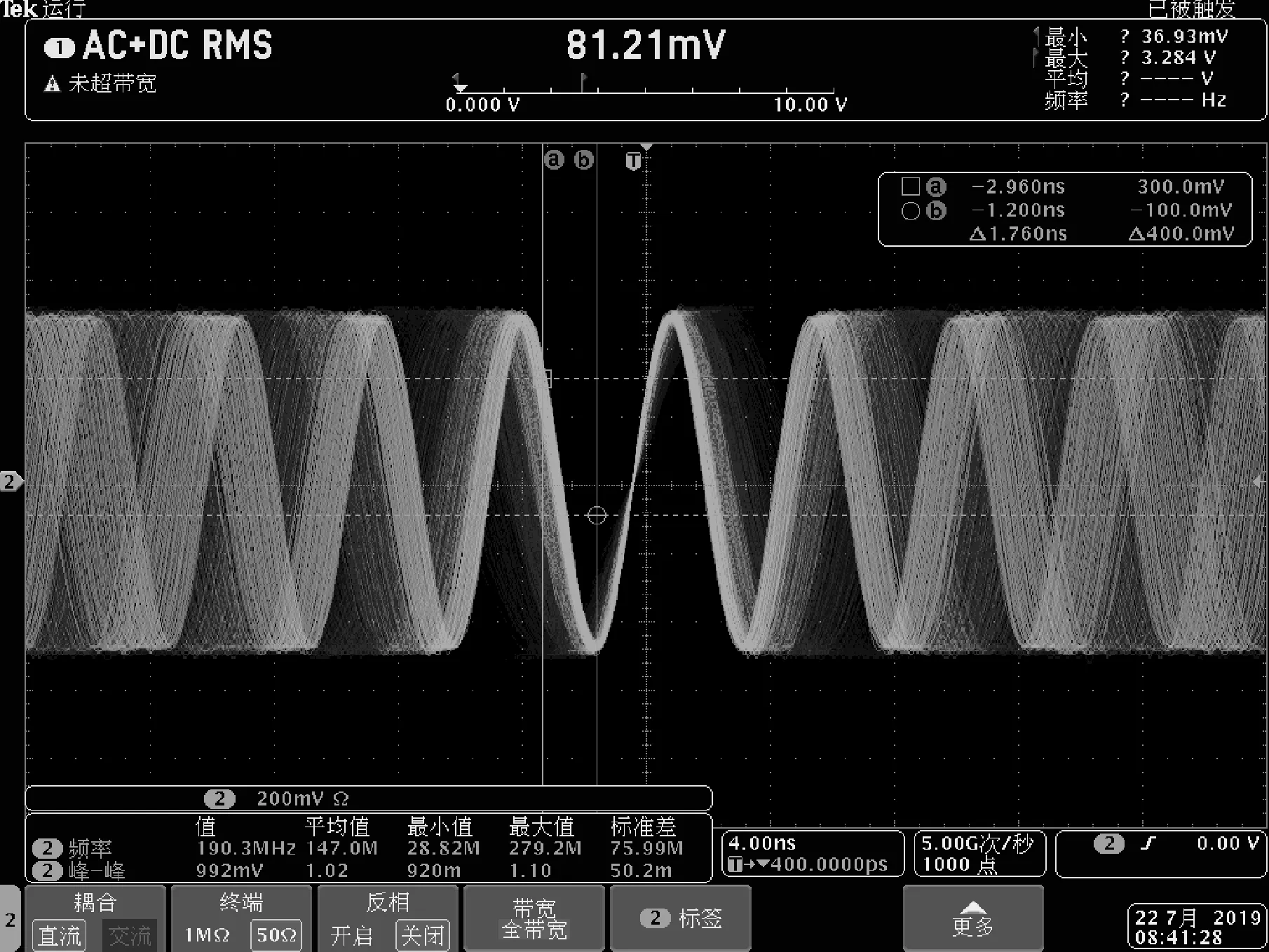

AD9912模块的输出焊接了SMA接口,需用测试仪器示波器、频谱仪及万用表。样机输出端的SMA接口与示波器的通道1通过同轴电缆相连,用万用表检查5 V、3 V、1.8 V处的电压是否正常。图6为测试波形。

图6 扫频输出

相位噪声是将信号对时序的变化在频率域显示出来,是描述信号源好坏的重要指标之一。如果一个信号没有相位噪声,那么该信号的功率都集中在f=f0处。相位噪声一般是指在某一个给定的偏移频率处的dBc/Hz。一般都是将信号源的输出与频谱分析仪相连。测试使用的是RIGOL的频谱分析仪,使用频谱仪的GTSA模式,使用Trace功能,将分辨率带宽RBW(Resolution Bandwith)设置为100 kHz,在样机的点频模式下对信号的噪声进行测量。

频谱仪上所测量数值是在等效带宽内的功率电平,需将该数据根据频谱仪所设定的RBW转化为1Hz的单位功率带宽,计算过程为

则根据相位噪声的计算公式可得

(9)

由图7、图8计算可得,当200 MHz,频偏为100 kHz时,相位噪声为L(100 kHz) = -10.14-50=-60.14(dBc/Hz);当100 MHz,频偏为1 MHz时,相位噪声为L(1 MHz)=-43.02-50 =-93.02(dBc/Hz)。

图7 100 MHz频偏1 MHz

图8 200 MHz频偏100 kHz

5 结语

利用集成的DDS芯片,设计一个多功能低相噪的信号源,实现点频及扫频的功能,调幅、调节分辨率和扫频时间间隔,实现1Hz~400MHz宽范围的信号输出,利用STC单片机作为微处理器进行控制与数据交互,实现人机交互界面。结合DDS技术与单片机技术实现DDS多功能信号源,控制方便、便于观察,产生的正弦波信号波形光滑、相位噪声低,可通过进一步提高频率和幅度,加入调相功能,应用于相关设备中。