一体化1553B 总线通信仿真平台设计与实现

张弟,江志东,高伟伟,彭海军

(海军航空大学青岛校区,山东 青岛 266041)

MIL-STD-1553B 总线是一种时分制多路复用数据总线[1],采用指令/响应型的通信协议及双冗余总线结构[2]。协议是20 世纪70 年代由美国空军提出[3],总线网络拓扑中控制权归总线控制器(BC)所独有[4],远程终端(RT)通过识别终端地址来响应BC 命令,使得数据实时有序传输。由于它的高可靠性、实时性和强抗干扰性[5-6],已经在航空航天等军事领域有着广泛的应用[6]。

在1553B 总线的教学中,总线上消息的格式、通信原理以及消息的调度对于学员来说较为抽象,1553B 总线学习缺乏感性认识的问题日渐突出,学生需要总线消息格式的可视化展示、通信时序的定量分析、总线通信的网络构建等。

现有的实验设备,在进行验证性实验时,需要学员在实验前将实验例程烧写到设备中,对没有任何单片机开发经验的学员而言,操作比较复杂,而且仿真器工作状态不稳定,导致实验效率低,故障率高;在进行二次开发时,由于代码的可读性低,学员编程实现的难度大。该设计采用一体化程序架构,将软件固化在Flash 中,通过串口助手直接设置平台的终端类型以及需要进行的实验类别,操作简单且不需要反复烧写程序,可以提高操作的效率,并且程序的可读性和实验的可操作性增强,可以更好地服务1553B 总线教学。

1 系统整体设计

仿真平台能够实现对1553B 总线协议从编码实验、原理实验到综合实验等验证性实验的支持,还可以为用户进行二次开发提供软硬件支持。

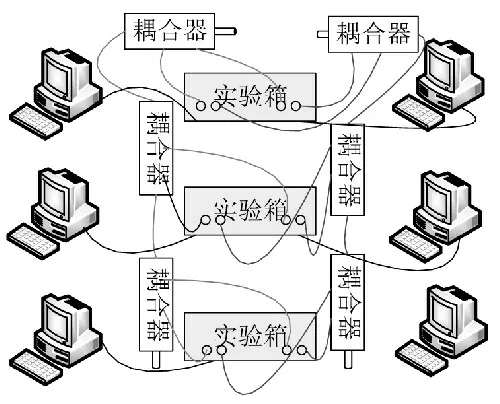

仿真平台设计了两块对称的MBI 板,每块MBI板上都包括主控模块、串口通信模块、1553B 收发电路,如图1所示。1553B 总线有3 种工作模式:总线控制器(BC)、远程终端(RT)、总线监视器(BM),每块MBI 板都具备这3 种工作模式。

图1 仿真平台硬件设计方案

平台软件固化在Flash 中,相关的数据存储在DPRAM 中。用户能够通过串口设定平台的终端类型、实验类型等;平台能够独立实现点对点的消息格式实验和通信原理实验,也可以完成多个平台组网进行综合性实验;该设计将硬件驱动进行封装,将数据块链表中数据进行具体定义,软件可读性增强,留有相应的软件接口,通过改变软件接口中的参数,就可以调整网络内消息的调度,如图2 所示。

图2 1553B仿真平台组网

2 系统硬件设计

1553B 总线仿真平台的设计旨在辅助1553B 总线通信原理教学,因此,平台的硬件设计要具备实时性和可靠性,并要具备丰富的测试资源,以便学员进行不同测试点的检测和验证。

2.1 主控模块

主控模块采用HKS1553BCRT,该芯片采用SoC架构,是一款通用化、低功耗的通信处理芯片[7],将“处理器芯片+多个存储器芯片+1553B 协议处理芯片+定时器”以单芯片的形式提供给用户使用[8]。目前HKS1553BCRT 已经广泛应用于1553B 总线通信模块和仿真平台的设计[9-11]。

平台采用供电电压为+5 V,电源电路将外部电源引入的5 V 电压进行电压转换分别得到3.3 V、2.5 V、1.8 V 和1.2 V 电压,为各个模块供电;两片HKS1553 BCRT 芯片的主机接口全部连接至FPGA 处理器的IO 管脚,将PCI 总线接口转化为USB 接口[12]。同时USB 驱动芯片FT232H 也与FPGA 处理器相连接,FPGA 能够通过读写FT232H 端口的缓队列进行数据交换,USB 接口能够通过USB 传输线与PC 机进行通信。PC 机上有上位机软件,通过USB 接口实现与实验箱交互。

为了增加开发实验的丰富性,实验箱设计时将HKS1553BCRT 芯片的GPIO 接口进行了扩展,设计了8 路LED 灯、4 路离散量模拟输入接口、一个蜂鸣器和8 段数码管等;平台上两片HKS1553BCRT 芯片各配置一片32 Mbit 的Flash 存储器用来固化程序和MBI 总线操作实验。

2.2 1553B总线收发电路

1553B 总线收发电路采用双冗余设计,如图3 所示。电路基于HI-1573 芯片搭建总线的通信接口模块,HI-1573 是低功耗双向CMOS 芯片满足1553B 收发要求,其功能是实现+3.3 V 差分电平与1553B 总线电平的匹配转换[13]。数据的收发还需经过变压器和耦合器,变压器采用M21038/27-26。该设计的两个LED 灯指示HKS1553BCRT 芯片被配置成BC 或RT 模式,指示灯通过GPIO 6 端口和GPIO 7 端口进行驱动,可以让用户直接看到芯片配置的状态。

图3 1553B总线收发器电路

2.3 串口通信电路

串口通信电路一路为RS232;另一路为RS422 和RS485,这两路通过软件控制使能端选择进行422 通信或485 通信,用于实现平台与上位机之间的交互。

3 系统软件设计

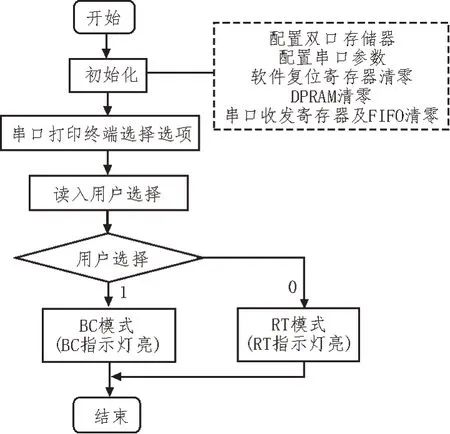

平台采用一体化的软件架构,能够实现MBI 板的初始化、地址重映射、与上位机交互,总线控制器(BC)和远程终端(RT)等功能。该设计将BC 功能和RT 功能集成在一个软件框架内,学员可以通过PC机与平台进行交互,选择MBI 板运行的终端类型进行实验。主函数流程如图4 所示。

图4 主函数流程图

系统上电,先完成初始化,初始化包括双端口存储器配置、串口参数配置、软件复位寄存器清零、DPRAM 清零以及串口收发寄存和FIFO 清零;随后通过串口向上位机发送终端类型选择选项的消息,并通过串口读取用户选择字符,用户输入字符1 选择BC 模式,用户输入字符0 选择RT 模式,进而进入相应终端软件的运行。

3.1 总线控制器(BC)软件实现

总线控制器负责传输信息和管理总线信息传输[14]。用户通过上位机选择平台作为BC 使用时,运行BC 软件,作为总线的控制中心,实现实验类型选择、10 种实验的完成以及软件复位等功能。

3.1.1 消息链表的建立

为了满足1553B 标准中BC 功能的实现,需要在内部寄存器和外部存储器中建立BC 的命令块结构。BC 的命令字都有一个命令块与之对应,命令块位于外部存储器DPRAM 中,由头指针、控制字、两个命令字、数据列表指针、两个状态字和一个尾指针8个字构成,如图5 所示。

图5 BC命令块结构

两个命令字第一个是接收命令字,第二个是发送命令字。数据指针指向命令块消息的数据在存储器中的起始位置。每个消息的相应数据必须连续存放。状态字1,包含RT 响应的状态字。状态字2 包含RT-RT 传送中接收RT 的状态字。对于不是RTRT 传送的消息,该位置不起作用。尾指针包含下一个命令块的开始地址。

命令块从DPRAM 偏移地址为0x80 的存储单元开始存放,前一命令块的尾指针指向下一命令块的头指针,形成命令块链表。

3.1.2 软件实现

BC 软件结构如图6 所示。首先通过串口打印实验类型选项,通过串口读取用户选择的字符,根据用户选择,运行相应实验的函数,运行结束,通过串口打印函数运行的反馈信息。

图6 BC软件架构

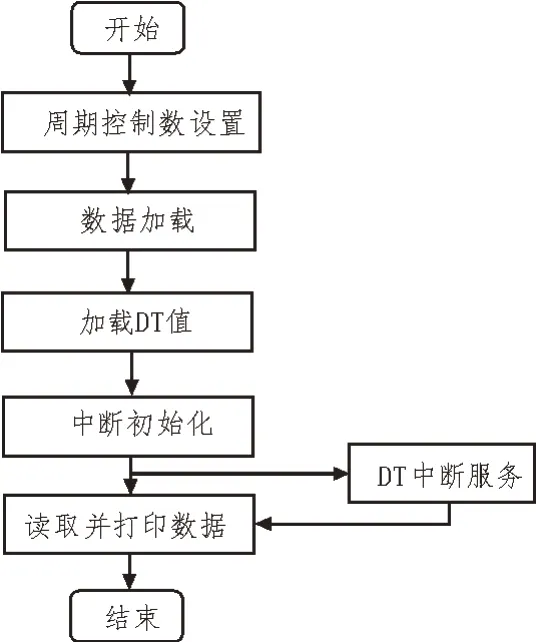

发送命令块时,BC 将命令块的起始地址在DT中断中写入寄存器rBlkAddrReg,自动读取命令列表,自动发送到总线上。时间间隔计时器DT 是HKS1553BCRT 芯片的毫秒级定时器,计数长度为8位。ARM7TDMI 处理器可通过rLOADDT 寄存器对DT 进行加载,当给DT 加载非零值时,DT 开始递减,递减到零,DT 分别向ARM7TDMI 和子系统主机发送一个中断信号,并自动加载上一次的加载值,重新开始计数;当给DT 加载零时,DT 停止计数,不产生中断。1553B 通信综合实验的大小周期调度都通过计时器控制。比如综合实验rLOADDT 寄存器值设为0x32,则DT 中断周期50 ms,再通过周期计数的设计,实现100 ms 的任务周期控制,100 ms 内,所有消息被发送一次,按照固定周期收发数据。

以综合实验为例,其程序流程如图7 所示。首先设置不同消息的周期控制数,通过数据加载函数完成不同消息的命令块中控制字及数据字的加载;完成数据加载后,加载DT 值并进行中断初始化;通过DT 中断服务程序,实现BC 命令块的发送;最后从RT-BC 数据缓冲区(DPRAM 中)读取并打印收到的消息数据。

图7 综合实验程序流程

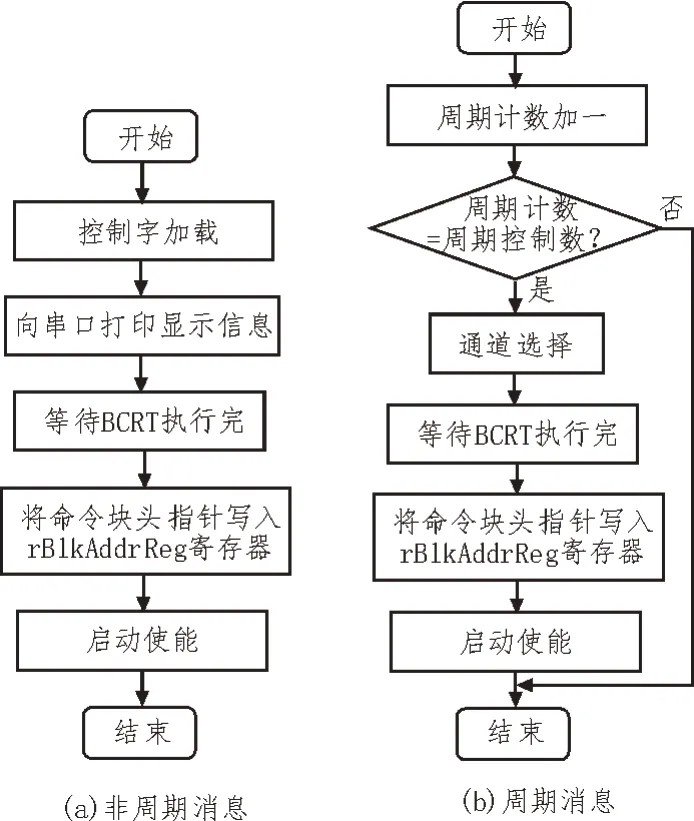

DT 中断服务程序可以分为非周期性消息处理和周期性消息发送两部分,处理流程如图8(a)、(b)所示。周期性消息的收发是按固定周期进行的,不同的消息设置了不同的周期控制数,每进入一次DT 中断,每种消息的周期计数值加一,当周期计数值与周期控制值相等时,选择通道,将命令块头指针写入rBlk AddrReg寄存器,启动使能,自动完成命令块的发送。

图8 DT中断服务程序流程图

BC 软件在接收数据时,通过bc_revedata()函数访问RT 到BC 的数据缓冲区,将数据存入变量,然后进行解析和显示即可。

3.2 RT软件实现

3.2.1 RT描述块

RT 接收块和发送块是基于描述块的相关参数进行配置,每个描述块包括4 个字:控制字、消息状态表指针、数据表指针和一个留待扩充的字,如图9所示。

图9 RT描述块

每个子地址有一个接收描述块和发送描述块,因此RT 配置了31 个接收块和发送块。描述块位于DPRAM 中,按照子地址的顺序依次排列。通过描述块中的索引功能,可以缓冲收发消息。

3.2.2 软件实现

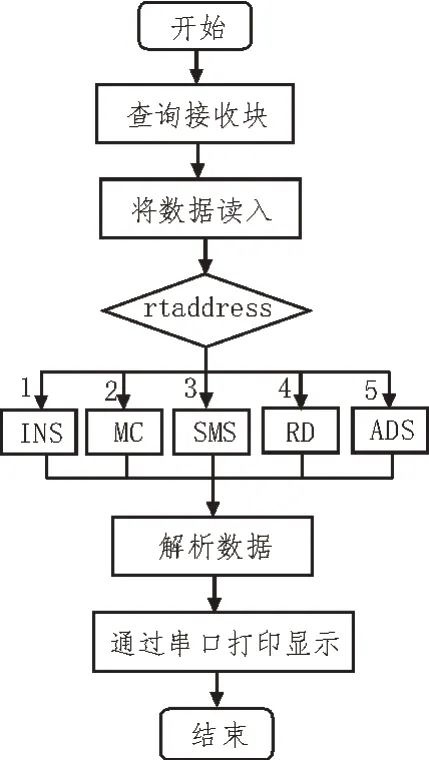

当平台作为RT 时,BC 的命令块到了,状态机会自动发送相应的状态字,RT 只需要读取和解析数据。RT 接收数据流程如图10 所示。

图10 RT接收数据流程

1553B 协议处理芯片会自动将收到的数据存入对应子地址的数据缓冲区,当RT软件读取数据时,查询接收块,通过readdrv(busn,ln,len,*message)函数访问数据缓冲区*(mbiad+recd+i*4+2)=datap,将缓冲区的数据读入变量,然后进行进一步的解析和显示。

RT 发送数据时,首先关闭MBI 的命令响应,执行setfuncdrv(busn,func)函数将MBI 板设置为RT 状态,并选择通道;向串口打印RT 地址设置消息,并通过串口回读用户设置;通过mbi_init_drv()函数加载输出输入表设置RT 地址,设置成功,执行initdrv()函数,将数据写入DPRAM 中;将发送描述块的地址写入rBlkAddrReg 寄存器,并启动发送,最后加载DT值,如图11 所示。

图11 RT发送数据流程

4 实验及数据分析

设计的平台实现并能够满足多层级教学的验证性实验、设计性实验和综合性实验,包括编码实验、数据传输实验、广播消息实验、方式消息实验和综合实验。

数据传输实验包括BC 传输到RT、RT 传输到BC、RT 传输到RT 和消息时间特性实验,通过串口助手进行人机交互并利用示波器检测总线上的波形,将3 套实验箱进行级联,结合部分消息定义,可模拟典型航空电子系统中子任务的消息调度。

以RT-RT 数据传输实验为例,将平台通过串口助手交互,一端设置为BC 工作模式,其余设置为RT工作模式[15],测得波形如图12 所示。

图12 RT-RT数据传输实验波形

1553B总线字长20位,数据有效位16位[16-18]。BC先向RT1 和RT2 分别发送命令字0x0827 和0x1447,命令字解析如下:

RT1 收到接收命令后,状态机自动回复BC 一个状态字;RT2 收到发送命令字,向RT1 发送7 个数据字;RT1 通过读接收缓冲区接收数据,数据接收完,状态机向BC 发送状态字,通信过程结束。通过波形可以看出这一过程字的交换,加深学生对1553B 总线通信过程的认识。

5 结论

文中设计采用一体化的软件架构,实现了3 个层次10种实验类型的功能,并且留有二次开发的软件接口,使得实验的稳定性、操作的友好性大幅度提高。