卡诺图在同步时序电路设计中的应用

许秀英,鄢仁辉

卡诺图在同步时序电路设计中的应用

许秀英1,鄢仁辉2

(1. 福州大学 物理与信息工程学院,福建 福州 350108;2. 福建师范大学 协和学院,福建 福州 350117)

卡诺图是数字电路中不可或缺的工具,广泛运用于函数化简和电路设计中.将卡诺图应用在同步时序电路设计方面,分别讨论在利用D功能、JK功能和T功能触发器进行电路设计及电路自启动分析中卡诺图的应用技巧.结果表明,巧妙使用卡诺图能大大降低同步时序电路设计的工作量及设计难度,并有助于得到最简单的设计结果.

数字电路;卡诺图;同步时序电路设计

卡诺图是数字电路中不可或缺的工具,是由贝尔实验室的电信工程师卡诺(Karnaugh)在1953年首先提出的[1].它不仅是逻辑函数化简的一种工具,更在对偶式的获取[2]、逻辑的运算和变换[3]、组合电路中竞争冒险的判断和消除[4]以及同步电路自启动的设计中[5-8]扮演着极重要的角色.学会灵活使用卡诺图,可以大大简化数字电路分析和设计的过程.本文就卡诺图在同步时序电路设计方面的应用展开探讨,着重阐述卡诺图在使用不同功能触发器进行电路设计中的灵活应变,以及在电路自启动判断和设计中的应用技巧.

1 同步时序电路的设计

利用触发器和门电路实现同步时序电路的设计过程一般步骤为[9]310:

(1)逻辑抽象,确定输入输出以及状态,得到状态图或状态表;

(2)状态化简,若有2个状态,在所有的输入下都是同输入同输出同次态,则这2个状态称为等价状态,二者可以合并为一个,减少一个状态,得到最简状态图或状态表;

(3)确定触发器的个数,进行状态分配;

(4)得到次态卡诺图,求出电路的状态方程、驱动方程和输出方程;

(5)根据方程式画出逻辑图;

(6)检查设计的电路能否自启动.

步骤(1)中的逻辑抽象是整个时序电路设计中最难的部分,这一步可通过多练习多观察并进行适当总结来攻克.步骤(4)的方程获取是整个设计中计算量最大的部分,步骤(6)计算量次之,若能巧妙使用卡诺图则能有效降低这2步的计算量.

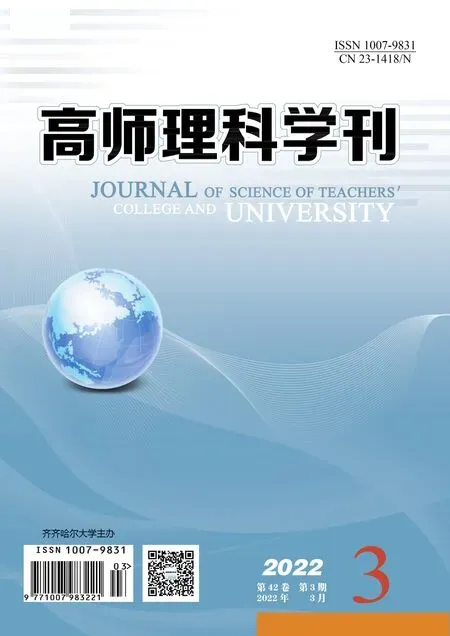

图1 13进制电路的次态/输出()卡诺图

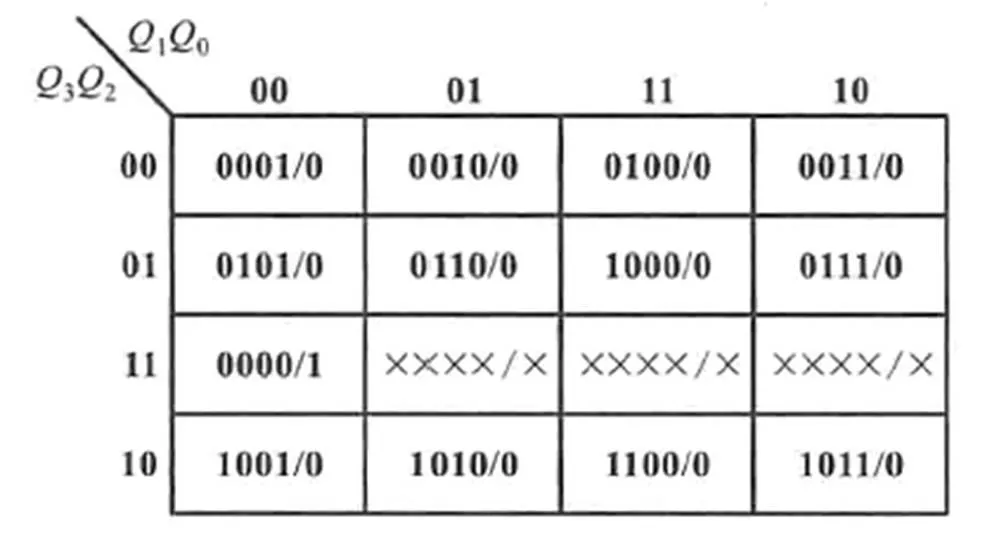

图2 卡诺图的分解

2 利用卡诺图快速得到驱动方程

2.1 D触发器

2.2 JK触发器

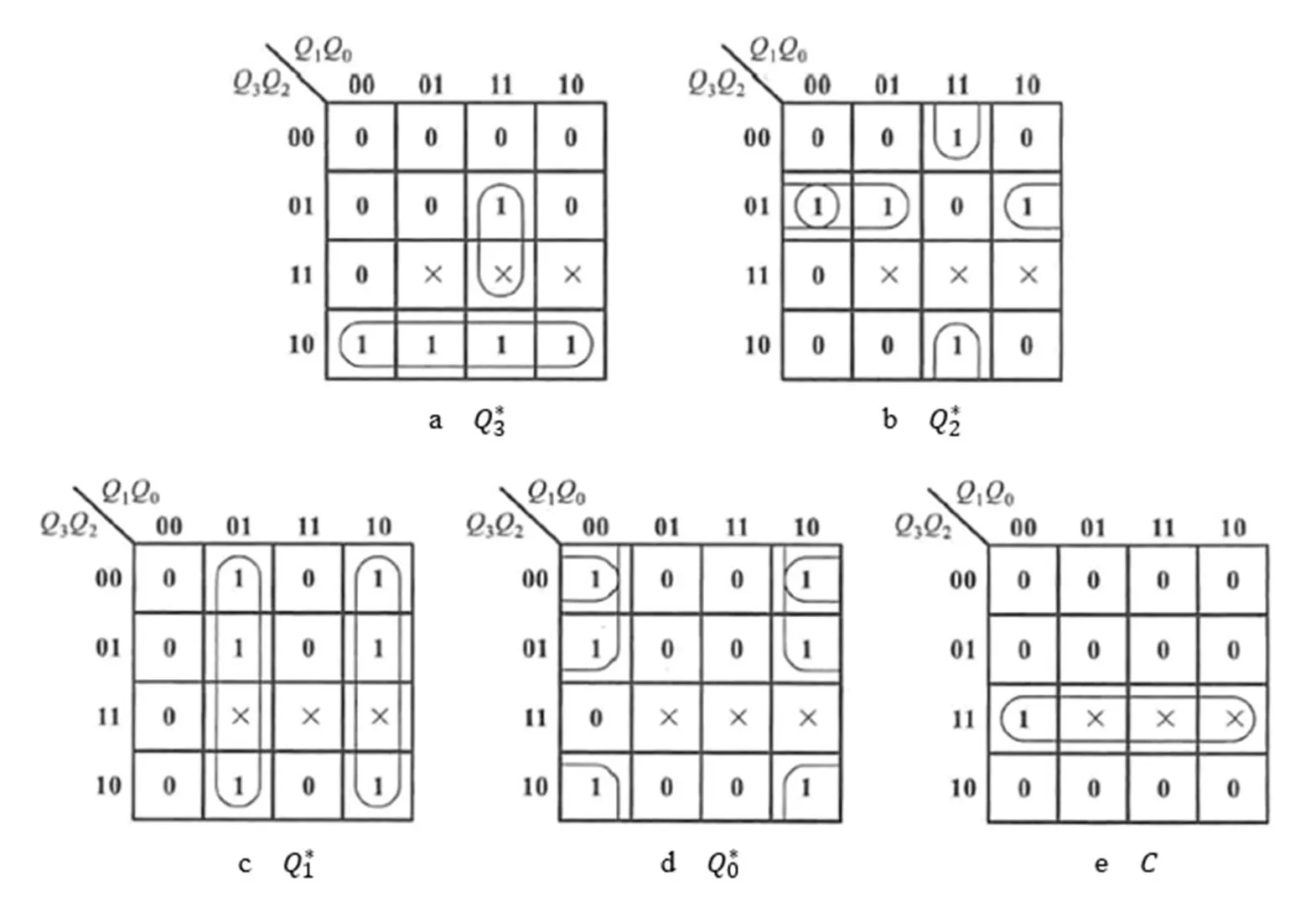

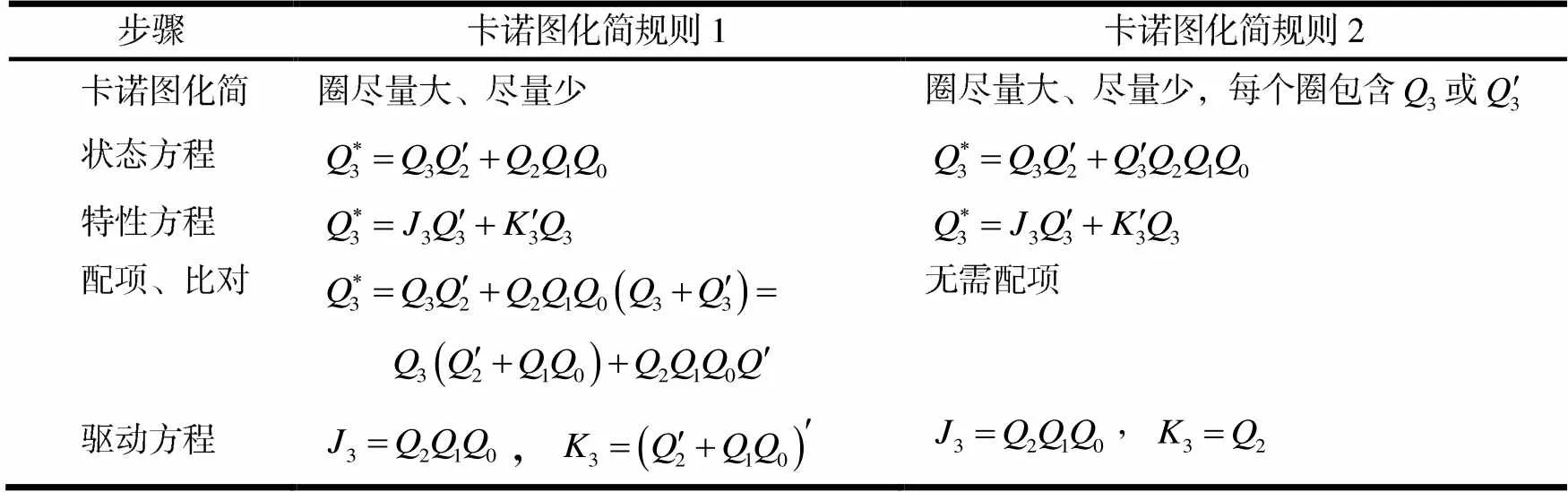

图3 2种不同的化简规则

表1 采用2种卡诺图化简规则得出驱动方程的比较

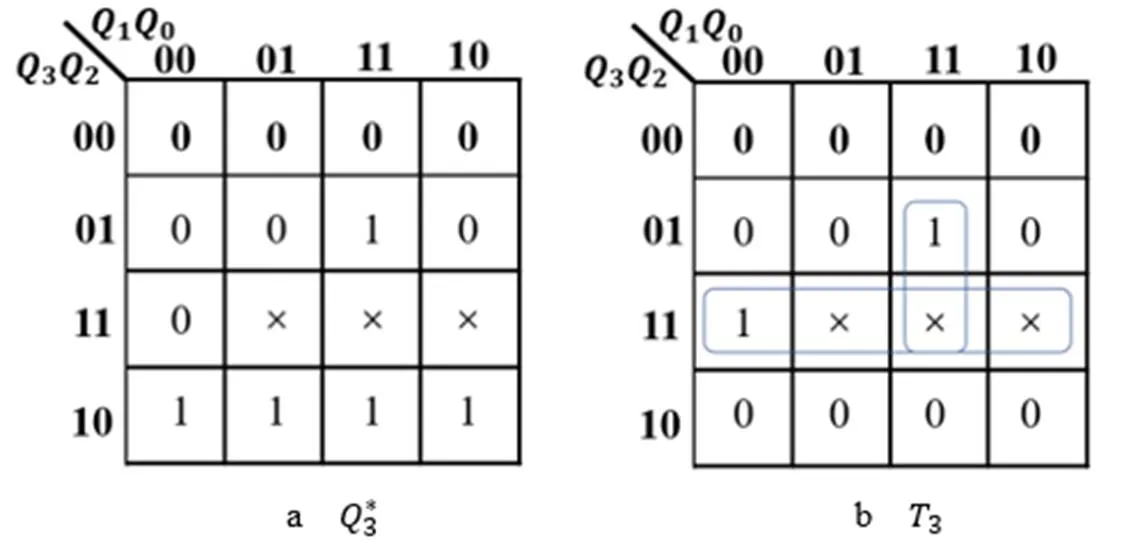

2.3 T触发器

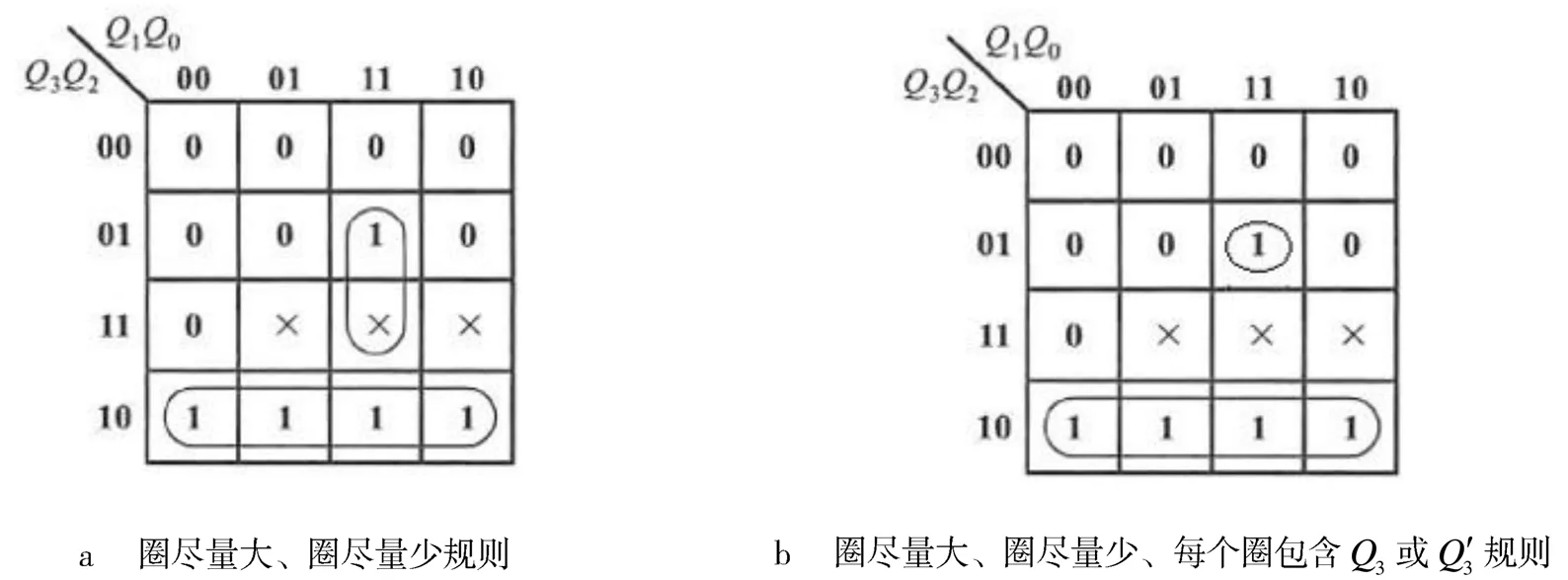

图4 和的卡诺图

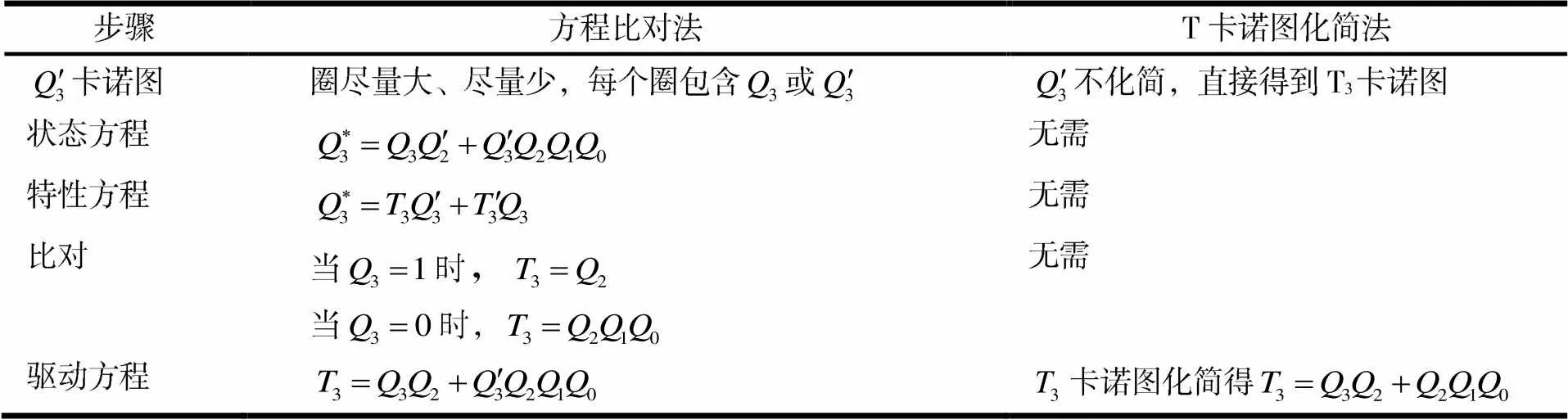

方程比对法和T卡诺图化简法的具体步骤见表2.从表2可以看出,方程比对法步骤繁多,且最后得到的驱动方程不是最简的,而T卡诺图化简法能一步到位得到最简的驱动方程.

表2 采用方程比对法和T卡诺图化简法得到驱动方程的比较

3 利用卡诺图快速判断电路的自启动问题

检查所设计电路能否自启动的一般方法是将无效状态代入状态方程依次计算次态值,以此判断能否自启动[9]314.显而易见,这种方法对于具有较多无效状态的电路其计算量是极其巨大的.本设计只有3个无效状态,就需要逐个将无效状态取值分别代入4个状态方程进行12次的运算,才能完成电路自启动问题的判断.并且这种方法只能在设计结束时才能检查自启动,一旦发现不能自启动,很可能需要进行二次设计,造成返工,费时费力.

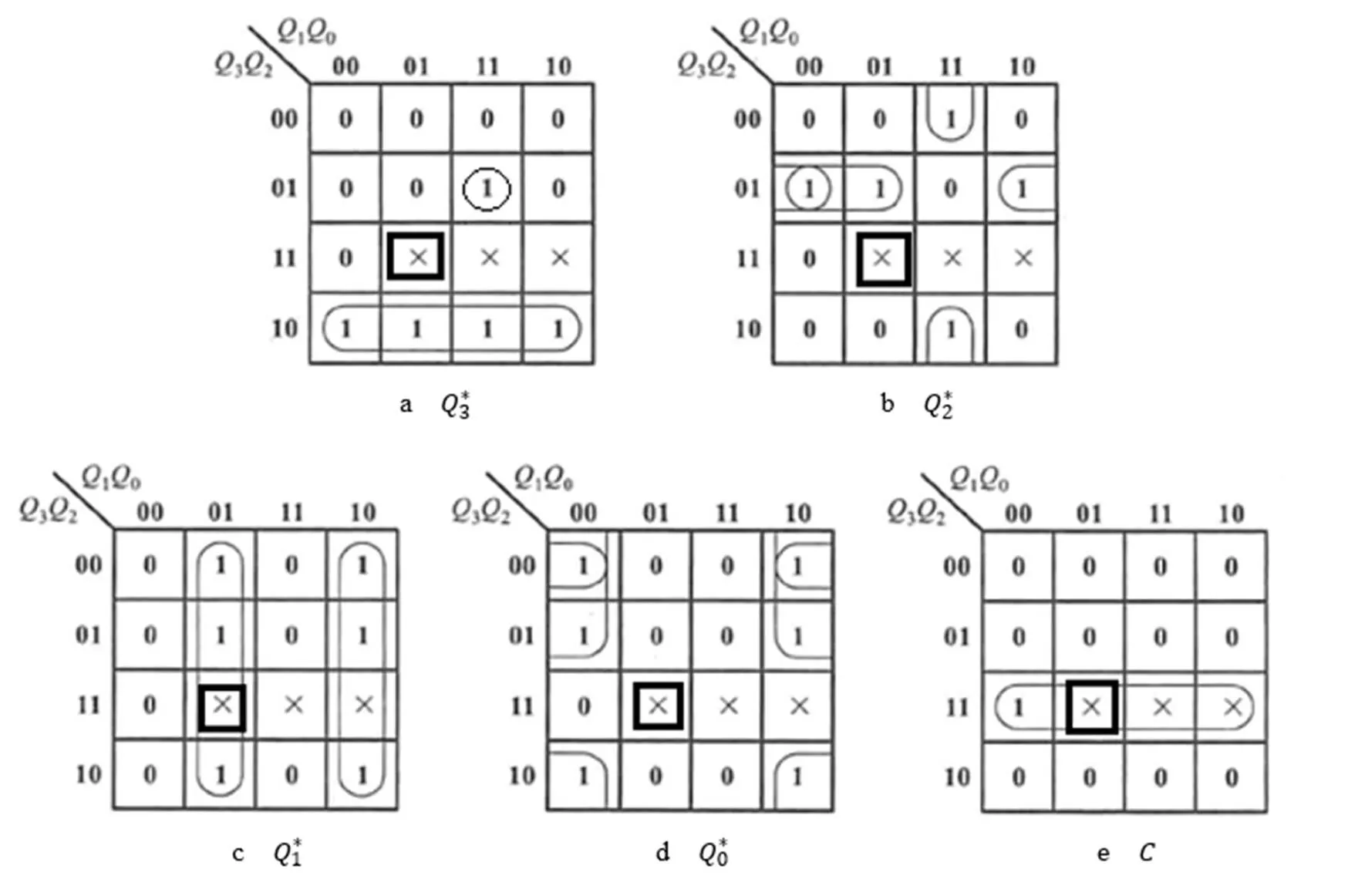

最简单的方法就是在卡诺图化简时直接观察,以卡诺图中的无关项是否被圈中为根据判断次态.在本设计中,以无效状态1101为例,对应位置见图5中的“矩形黑框”,这些“×”被圈住的就是“1”,未被圈住的就是“0”,很容易判断出无效状态1101的次态是0010,输出是1.同理,可以得到无效状态1110的次态是0000,输出是1;无效状态1110的次态是0010,输出是1.电路可以自启动.利用卡诺图判断自启动问题,只要明白规则,依靠观察加记录就能看出每个无效状态的次态,进而判断自启动.无需计算,省时省力,高效快速,并且在设计之初就能观察到自启动情况,若是不能自启动,完全可以及时调整设计以达到自启动的目的,从而避免了二次设计的返工问题.

图5 卡诺图观察法判断13进制电路的自启动情况

4 结语

在使用JK触发器或T触发器的同步时序电路设计中,巧妙地使用卡诺图就有可能显著降低设计的计算量,同时还有助于最终得到最简的电路设计图.在使用各种类型触发器(包括D,JK,T触发器)的同步时序电路设计中,灵活使用卡诺图,能提早进行电路自启动情况的检查和设计,大大降低同步时序电路的设计难度和计算量.

[1] Karnaugh,Maurice.The Map Method for Synthesis of Combinational Logic Circuits[J].Transactions of the American Institute of Electrical Engineers(Ⅱ),1953,72(5):593-599.

[2] 姜书艳,张优,卢有亮,等.浅谈在卡诺图中实现对偶律的方法[J].教育教学论坛,2019(12):219-220.

[3] 罗雯.卡诺图在数字电子技术中的应用[J].中国高新技术企业(中旬刊),2015(4):64-65.

[4] 张春梅.数字电路中卡诺图的更多应用研究[J].天津职业院校联合学报,2018,20(4):115-119.

[5] 腾香.基于次态卡诺图的移位寄存器型计数器的自启动设计[J].浙江大学学报(理学版),2011,38(4):419-423.

[6] 李金灿.卡诺图在数字电子技术课程中的应用[J].赤峰学院学报(自然科学版),2017,33(16):212-214.

[7] 夏银水,叶锡恩.扭环形控制器的新设计[J].宁波大学学报(理工版),2000(4):419-423.

[8] 宋灵贵,徐月华,陈偕雄.能自启动的移位型计数器的新设计[J].浙江大学学报(理学版),2000,27(6): 612-616.

[9] 阎石,王红.数字电子技术基础[M].6版.北京:高等教育出版社,2018.

Application of Karnaugh map in synchronous sequential circuit design

XU Xiuying1,YAN Renhui2

(1. School of Physics and Information Engineering,Fuzhou University,Fuzhou 350108,China;2. School of Concord,Fujian Normal University,Fuzhou 350117,China)

Karnaugh map is an indispensable tool in digital circuits,which is widely used in function simplification and circuit design.Discussed the application of Karnaugh map in synchronous sequential circuit design,focused on the design using JK/T flip-flop and the judging of self-starting.It is turned out that Karnaugh map can not only greatly reduce the workload of synchronous sequential circuit design but also help to achieve the simplest circuit design.

digital circuits;Karnaugh map;synchronous sequential circuit design

1007-9831(2022)03-0077-05

TN79+1∶G642.0

A

10.3969/j.issn.1007-9831.2022.03.016

2021-11-09

2020年福州大学课程思政项目;福建省教育厅科学研究项目(JT180051);福建师范大学协和学院教育教学改革研究项目(JG20190105)

许秀英(1980-),女,福建福州人,讲师,硕士,从事惯性导航研究.E-mail:xuxiuying@fzu.edu.cn

鄢仁辉(1981-),男,福建福州人,讲师,硕士,从事嵌入式系统研究.E-mail:yrhuixxan@qq.com