浅谈时序逻辑电路的成长记忆

(江苏省张家港市第二职业高级中学,江苏苏州市,15000)万 莉

在对口单招《电子技术基础》科目的数字电路部分的教学过程中,在小结学习效果时不难发现,在不少学生的认知里的组合逻辑电路与时序逻辑电路这两个知识模块的关系是相互独立的,并未融合在一个知识串联的体系里。或者说这两个模块的内容与现实生活的距离较远,不能共情,难以透彻理解。在这两个章节的基础知识讲授完成后,对两个章节内容前后知识做一个带比喻性质的知识梳理,用形象化的描述将抽象转为具象,以帮助学生更好的建立数字电路的知识框架。

1 起源--基本逻辑门

数字电路的基本逻辑门是与门、或门、非门。是数字电路里的泥和土,是构建数字电路摩天大楼的原始材料。

基本门之间相互组合,便构成了组合门。其中与门和非门组成了与非门;或门和非门组成了或非门。它们是组合逻辑电路的主角。是构建数字电路摩天大楼的砖和瓦。

组合逻辑电路的特点是没有记忆功能,当前的输出状态直接由当前的输入状态所决定,输入状态消失,则输出会立即消失。

2 搭建--基本RS触发器

由两个与门相互连接,可构成基本RS触发器,它的出现表示已从数字电路的组合逻辑电路离开,慢慢走近时序逻辑电路。基本RS触发器可以简单且直接的完成置0、置1、保持的逻辑功能。

基本RS触发器的特点是无需等待触发脉冲,直接置0或置1,可以说是简单、粗暴的完成运算功能。输入项、的下标号D已表明“直接开工”的特殊身份。

基本RS触发器可由与非门构成,也可由或非门构成。

3 雏形—钟控同步RS触发器

数字逻辑电路的特点是具有记忆功能,当前的输出状态与输入状态有关,还与电路的原状态有关。

钟控同步RS触发器触发器可由与非门构成,也可由或非门构成。

4 完善—主从RS触发器

在四个与非门构成的钟控同步RS触发器的基础上增加一组结构相似的模块,即8个与非门组成2个团队,交替工作,这个触发器称为主从RS触发器,将其中4个与非门的模块称为主触发器,另外4个与非门的模块称为从触发器。采用这种结构可以将钟控同步RS触发器的电平触发方式升级成边沿触发方式,触发时间大大的缩短,有效的克服了空翻现象,于是主从RS触发器具有实用价值。主从RS触发器同样可由与非门构成,也可由或非门构成,其逻辑功能具有置0、置1、保持、不定(不允许),除触发方式不同外,其特性与钟控同步RS触发器完全一致。

为了限制逻辑功能里的“不定(不允许)”的出现,在运算时要加入约束项:R×S=0,即置0和置1不能同时进行。

5 巅峰—JK触发器

图1 JK触发器

如图1所示,将主从RS触发器输出端拉回到输入端,这样的连接便组成了JK触发器。在触发方式有上升沿触发和下降沿触发,其逻辑功能具有置0、置1、保持、翻转。RS触发器的逻辑功能里有不定(不允许),正常运算时只能使用75%的逻辑功能,而JK触发器没有约束项,用翻转功能替代了RS触发器中不定(不允许)在逻辑功能中的位置,逻辑功能配项得到100%的利用,它是功能更强大的触发器。

6 分家—T、D触发器

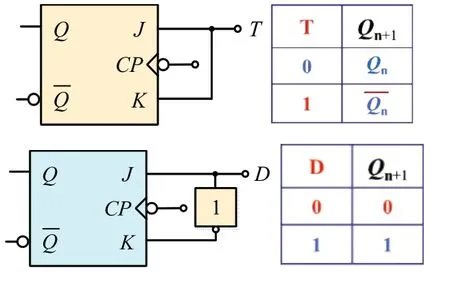

如图所示,JK触发器也要分家,功能全面的JK触发器将它的四个逻辑功能公平的分给了一对龙凤胎T和D触发器。将JK触发器的两个输入端连接在一起,即J=K,便构成了T触发器,它得到了JK触发器逻辑功能里的保持和翻转;将输入端K连上一个非门再与输入端J相连接,即,便构成了D触发器,得到了JK触发器逻辑功能里的置0和置1。

图2 TD触发器

综上所述,可将以上触发器划分成RS家族和JK家族,在学习RS家族的触发器时,重点是关注触发脉冲的不同、与非门和或非门组成结构的差异(真值表、结构图);JK家族的触发器时,重点是JK、T、D相互之间的转换,以及直接置零端和直接置1端的综合应用。