高性能毫米波CSRR-SIW带通滤波器研制

周 聪,董洪成,王禁城,苏国东,2,王 翔,刘 军

(1.杭州电子科技大学浙江省大规模集成电路设计重点实验室,浙江 杭州 310018;2.毫米波国家重点实验室,江苏 南京 210096)

0 引 言

随着后摩尔时代的到来,雷达、商用通信设备、电子战武器等通信系统的小型化、高可靠性、高集成度迎来全新挑战。微波滤波器在微波通信系统领域充当着极其重要的角色,直接影响通信系统的整体性能。为了研制毫米波频段应用的高性能滤波器,一般将金属腔体设计方法、印刷电路板(Printed Circuit Board,PCB)工艺、低温共烧陶瓷(Low Temperature Co-fired Ceramic,LTCC)技术、集成无源器件(Integrated Passive Device,IPD)技术等引入毫米波滤波器的设计中[1]。相较于其他几类技术,IPD技术可以将无源器件及其设计的电路做到更小型化、易集成和高性能。因此,采用IPD技术设计毫米波滤波器是实现高性能微波通讯系统的重要研究方向。文献[2]基于硅衬底的IPD工艺设计了一款3.0~10.6 GHz可调谐陷波滤波器,通过双间隙可调电容器实现了陷波频率调谐。文献[3]采用耦合电感器的方式,通过IPD工艺加工了3款中心频率为28 GHz的带通滤波器,频带宽度可达9.6 GHz。在GaAs衬底的IPD工艺上,文献[4]设计了一款带1/8波长耦合传输线和Marchand巴伦的带通滤波器,并在终端加载电容器,解决了传统巴伦无法控制奇偶模阻抗值的问题,减轻了大耦合系数产生的负面影响;文献[5]设计了一款宽阻带低通滤波器,在15~30 GHz的阻带内拥有30 dB的衰减量。研究人员尝试采用IPD技术在基片集成波导(Substrate Integrated Waveguide,SIW)上蚀刻不同形状的并联互补开口谐振环(Complementary Split-Ring Resonator,CSRR),研制了30 GHz以下的带通滤波器。但是,在毫米波频段实现高性能带通滤波器,依旧存在传输损耗较高、覆盖频带较窄、尺寸过大等问题。所以,本文从SIW高通滤波特性和CSRR基本原理出发,采用硅基IPD技术,研制了一款工作于毫米波频段加载并联互补开口谐振环的基片集成波导(CSRR-SIW)带通滤波器。

1 CSRR-SIW带通滤波器的研制

SIW带通滤波器的设计中,SIW的高通滤波特性、SIW与矩形波导的等效关系、CSRR工作原理等是分析滤波器特性、实现最优化设计的基础。在分析SIW带通滤波器的实现原理和CSRR技术的基础上,本文采用IPD工艺,通过改变CSRR物理结构参数来分析CSRR对带通滤波器性能的影响,研制了一款工作于毫米波频段的CSRR-SIW带通滤波器。

1.1 SIW高通滤波特性

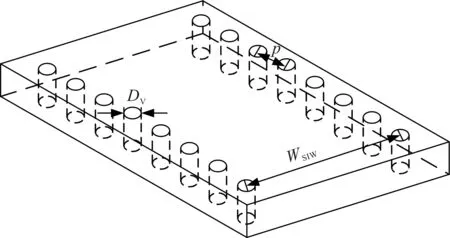

SIW结构通过2列均匀排布的金属过孔来打通多层金属面和金属材料之间的介质,将电磁波限制在介质基片金属面以及均匀排布的2列金属过孔之间,从而达到与矩形波导类似的高通滤波传输效果。SIW的基本结构如图1所示,SIW的2列金属过孔的宽度为WSIW,金属过孔的直径为Dv,相邻2个金属过孔的距离为p。电磁波在SIW上传播时的插入损耗和回波损耗主要由Dv和p决定,SIW尺寸的设计原则一般要求Dv<0.2λg,Dv/WSIW<0.2,Dv/p≥0.5,其中λg为矩形波导波长[6]。

图1 基片集成波导基本结构

SIW与矩形波导具有相似的传输效果,将SIW等效为矩形波导用于分析SIW的传输特性是普遍采用的设计方法。设矩形波导的宽度为WRWG,SIW与等效矩形波导的等效关系为[7]:

(1)

式中,

(2)

(3)

(4)

通过设计确定的WSIW,WRWG,Dv,p和相对介电常数εr,并定义电磁波在真空中传播速度为vc,SIW中传输TE10模的截止频率fcTE10为:

(5)

由式(5)可见,设计越高的截止频率,需要提供越小的WRWG,这正好与毫米波频段带通滤波器设计小型化相契合。SIW的高通滤波特性能够提供良好的低频带外抑制,但仅仅通过SIW不足以设计带通滤波器。文献[8]指出,在表面刻蚀开口谐振环及其变形结构的SIW会产生消逝模效应,即在截止频率下,引入电容性单元,形成谐振,从而在波导截止频率外产生通带。所以,本文通过在SIW上加载开口谐振环的变形结构CSRR研制了一款低插入损耗和良好带外抑制效果的带通滤波器,并采用共面波导互联结构进一步降低匹配损耗。

1.2 CSRR-SIW带通滤波器的参数设计及仿真

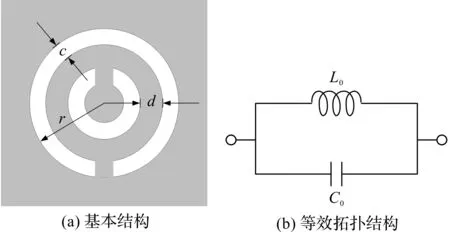

开口谐振环技术(Split-Ring Resonator,SRR)最早应用于左手材料结构单元,由2个方形开口金属环开口相对嵌套而成[9]。通过在金属平面刻蚀SRR结构形状,得到互补开口谐振环CSRR[10],实现类似左手材料中介电常数和磁导率同时为负值的效果。Zhuang等[11]第一次将CSRR技术应用到SIW带通滤波器设计中,实现了良好的带外抑制效果。本文研制的加载CSRR的SIW带通滤波器上蚀刻的圆型CSRR基本结构如图2(a)所示,刻蚀线宽c、外环刻蚀半径r和环间距d决定了CSRR环内的谐振效果[10]。圆型CSRR金属与金属之间产生感应电容C0,镶嵌于内外环之间的金属则产生感应电感L0,其等效拓扑结构如图2(b)所示。谐振回路的谐振频率为:

(6)

图2 圆形CSRR的基本结构及等效拓扑结构

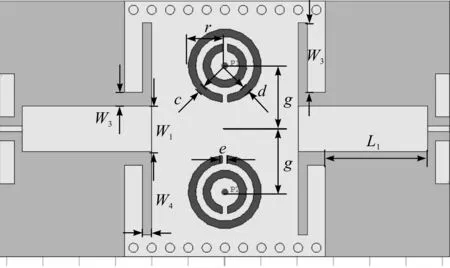

本文研制的CSRR-SIW带通滤波器结构采用共面波导过渡到微带、微带转波导的互联方式,并在SIW高通滤波器上刻蚀2个开口相对的圆型CSRR,实现了较好的带外抑制效果。相较于凹型过渡结构,共面波导过渡结构拥有更大的灵活性。相较于锥型过度结构,共面波导过渡结构在实现宽传输频带和低插入损耗的同时,使得带通滤波器更加紧凑。为了实现SIW的高通效应,根据SIW的一般设计规则与矩形波导等效方法将SIW的结构参数WSIW设置为1 300 μm,Dv设置为50 μm,p设置为100 μm。采用三维全波电磁场仿真软件建立的CSRR-SIW带通滤波器结构如图3所示,其中W1,W2,W3,W4,L1为共面波导结构的物理尺寸,c,d,r为图2(a)中圆形CSRR结构的尺寸参数,e为CSRR开口处的宽度,g为2个CSRR中心的距离。

图3 CSRR-SIW带通滤波器结构示意图

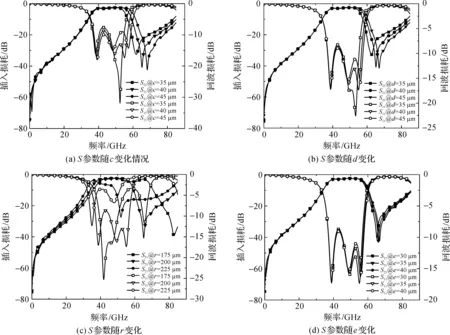

为了获得高性能带通滤波器,研究CSRR对SIW带通滤波器的影响。将本文设计的CSRR-SIW带通滤波器放入三维全波电磁场仿真软件进行仿真,带通滤波器性能随CSRR物理尺寸变化情况如图4所示。从图4(a)和(b)可以看出,调整CSRR的刻蚀线宽c和环间距d会使并联谐振电容值变化,改变谐振频率点,最终影响CSRR-SIW带通滤波器的带宽和通带的截止频率。从图4(c)可以看出,减小外环刻蚀半径r可以使传输零点往高频移动,从而增强带外抑制的效果,选择过大的r值使得零点处于带宽内;从图4(d)可以看出,增大开口e可以降低并联谐振电感,使得零点向高频处产生微小移动,相较于调整c和d,调整e对带通滤波器影响不明显。

图4 CSRR-SIW带通滤波器性能随CSRR物理尺寸变化情况

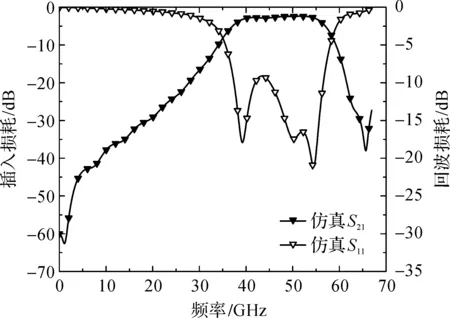

结合CSSR的物理参数对SIW带通滤波器的影响分析和SIW带通滤波器小型化高性能设计的要求,本文通过设计优化得到CSRR-SIW带通滤波器的尺寸参数如下:对称CSRR的刻蚀线宽c=40 μm,环间距d=40 μm,外环蚀刻半径r=200 μm,CSRR中心至SIW中心线位置距离g=345 μm,共面波导线宽W1=250 μm,共面波导线长L1=600 μm,图3中共面波导物理尺寸参数W2,W3和W4分别为75 μm,455 μm和50 μm。采用三维全波电磁场仿真软件仿真得到CSRR-SIW带通滤波器的插入损耗与回波损耗仿真结果如图5所示。

图5 CSRR-SIW带通滤波器的插入损耗与回波损耗仿真结果

从图5可以看出,通带内最低插入损耗为-2.38 dB,3dB带宽通带覆盖范围为36.8~57.2 GHz,中心频率47 GHz的插入损耗为-2.54 dB,3dB带宽达20.4 GHz,回波损耗在37.2~56.8 GHz频带范围内小于-9 dB,在谐振频率65.5 GHz的衰减达到-37.4 dB。

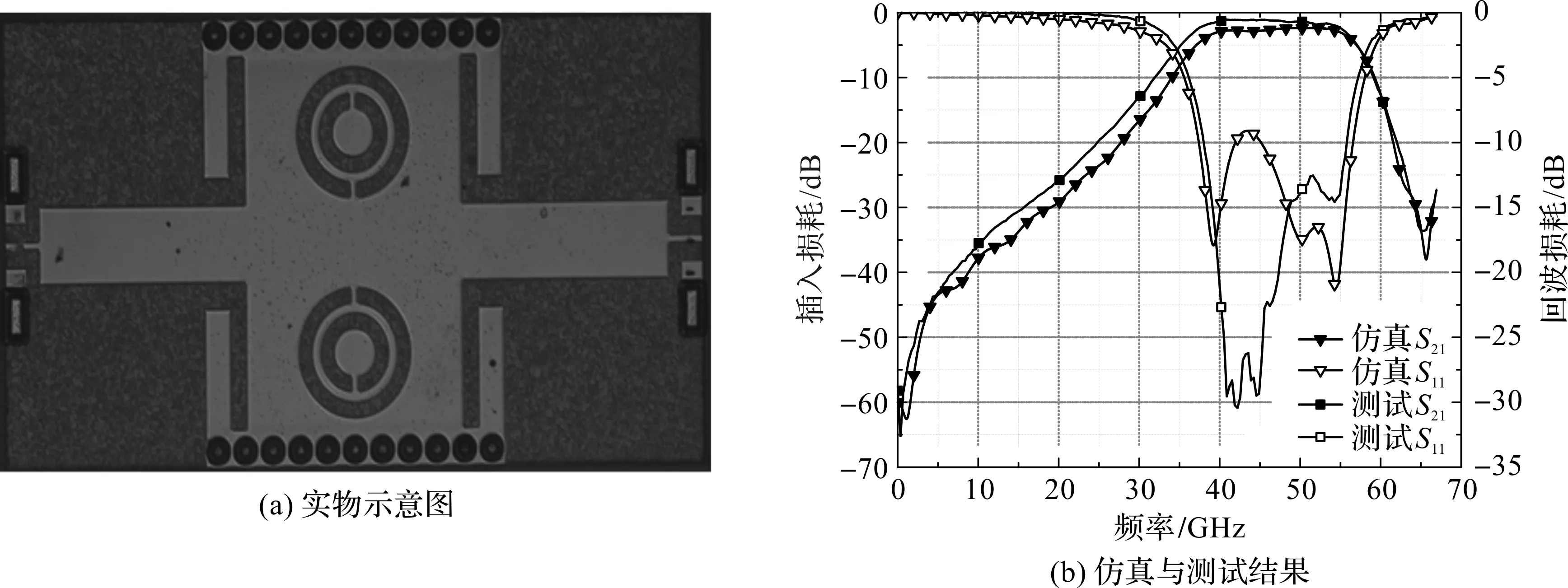

2 CSRR-SIW带通滤波器的加工与测试

采用硅基IPD工艺对本文研制的CSRR-SIW带通滤波器进行加工。图6(a)为滤波器实物的示意图。滤波器的宽度为1400 μm,长度为2540 μm,厚度为540 μm。采用Keysight的矢量网络分析仪对带通滤波器进行评估测试,并将测试数据与三维全波电磁场仿真软件的仿真结果进行对比,结果如图6(b)所示。

图6 加工电路效果与测试环境

从图6(b)可以看出,在通带40.9 GHz处,最低插入损耗达到-1.07 dB,3dB带宽通带覆盖35.9~56.6 GHz,在中心频率46.2 GHz处的插入损耗为-1.20 dB,3dB带宽达20.7 GHz,回波损耗在38.1~55.7 GHz频带范围内小于-10 dB,在谐振频率65.5 GHz的衰减达到-33.6 dB。由于SIW的物理尺寸在实际加工中存在误差,同时受仿真精度的影响,SIW的高通谐振频率向低频移动了0.9 GHz,改变了SIW的特性阻抗,使得匹配情况发生变化,最终影响到回波损耗。

对相关毫米波带通滤波器的性能进行综合分析,结果如表1所示。

表1 相关毫米波带通滤波器的设计性能

从表1可以看出,本文设计的CSRR-SIW带通滤波器带宽优于文献[12-15],高频带外抑制性能优于[12]和文献[14],在插入损耗方面优于文献[12-15],所以本文研制的毫米波带通滤波器具有一定的同行竞争力。

3 结束语

文中研制了一款35.8~56.6 GHz 低插入损耗的CSRR-SIW带通滤波器。从矩形波导与SIW带通滤波器的基础理论入手,通过分析SIW的高通特性及CSRR物理参数对带通滤波器性能的影响确定了带通滤波器的物理模型,并选用适合微系统集成的硅基IPD制造工艺进行加工,研制出宽频带、低插入损耗、强带外抑制的CSRR-SIW带通滤波器,为设计高性能、小型化、易集成的毫米波带通滤波器提供借鉴方案。后续计划继续研究不同类型CSRR结构加载方式,在确保低插入损耗的同时进一步提高带通滤波器的中心频率和带外抑制效果。