N2O 处理对背沟刻蚀金属氧化物薄膜晶体管性能的影响*

徐华 刘京栋 蔡炜 李民 徐苗 陶洪† 邹建华 彭俊彪

1) (广州新视界光电科技有限公司,广州 510530)

2) (华南理工大学,发光材料与器件国家重点实验室,广州 510641)

3) (季华实验室,佛山 528000)

通过采用稀土元素镨掺杂铟锡锌氧化物半导体作为薄膜晶体管沟道层,成功实现了基于铝酸的湿法背沟道刻蚀薄膜晶体管的制备.研究了N2O 等离子体处理对薄膜晶体管背沟道界面的影响,对其处理功率和时间对器件性能的影响做了具体研究.结果表明,在一定的功率和时间处理下能获得良好的器件性能,所制备的器件具有良好的正向偏压热稳定性和光照条件下负向偏压热稳定性.高分辨透射电镜结果显示,该非晶结构的金属氧化物半导体材料可以有效抵抗铝酸的刻蚀,未发现明显的成分偏析现象.进一步的X 射线光电能谱测试表明,N2O 等离子体处理能在界面处形成一个富氧、低载流子浓度的界面层.其一方面可以有效抵抗器件在沉积氧化硅钝化层时等离子体对背沟道的损伤;另一方面作为氢的钝化体,抑制了低能级施主态氢的产生,为低成本、高效的薄膜晶体管性能优化方式提供了重要参考.

1 引言

金属氧化物半导体 (metal oxide semiconductors,MOS)薄膜晶体管 (thin film transistors,TFT) 因具有较高的迁移率、较好的均匀性、大的电流开关比、可见光透明等优点[1-3],在显示领域具有广泛的应用潜力,高性能、可靠的金属氧化物薄膜晶体管已成为国内外科研院所和产业界的重点研究方向.

在MOS 材料的研究中[4-8],最具代表性的当属氧化铟镓锌 (indium-gallium-zinc-oxide,IGZO),其在薄膜晶体管中的应用已有量产实绩,可以满足部分应用场景的需求.但是,随着显示技术的发展,IGZO 对作为驱动背板核心元件的薄膜晶体管提出了更高的标准.如高迁移率、高稳定性,特别是光照条件下的稳定性等有了更严苛的要求.其次,在金属氧化物TFT 结构的探索中[9-11],比较具有应用前景的是背沟道刻蚀 (back channel etch,BCE)结构和顶栅自对准 (top-gate self-aligned,TGS)两种结构.其中,TGS 结构最大的优点是在寄生电容方面比较突出,但是在导体化和短沟道器件的实现方面存在较大的挑战,稳定性有待进一步提高;而BCE 结构因和当前大规模量产的硅基工艺兼容、可实现低成本制备而备受关注.但是,考虑到MOS对酸、碱、水、氧等特别敏感的问题和低电阻布线的要求[12,13],目前产业界主要基于铜酸工艺制备背沟道刻蚀的金属氧化物薄膜晶体管.而铜酸主要的有效成分是双氧水,存在有效期短、对金属膜层结构敏感,甚至有爆炸的风险.基于铝基的叠层结构金属膜层在应用中非常成熟,需要强调的是,该结构的薄膜需要用磷酸基的强酸刻蚀液进行图形化,在背沟道刻蚀的金属氧化物薄膜晶体管应用中较难实现良好特性.通常,需要对制备工艺进行特殊处理.而N2O 等离子体处理是一种高效的氧源补充方式,和氧气相比,N2O 具有更低的离化氧形成焓 (N2O:1.73 eV,O2:4.13 eV)[14],可以在相对较低的功率下离化,这样可以避免高强度的等离子体轰击对氧化物半导体的影响.N2O 等离子体处理在金属氧化物薄膜晶体管的制备中已有尝试[14-16],但在湿法背沟道刻蚀的金属氧化物薄膜晶体管研究中还鲜有报道.

本文采用稀土镨掺杂的氧化铟锡锌半导体(praseodymium-indium-tin-zinc-oxide,PITZO)作为薄膜晶体管器件的沟道层,制备基于铝酸的背沟道刻蚀金属氧化物薄膜晶体管.通过引入N2O 等离子体处理薄膜晶体管的背沟道界面的方式,对其处理功率和时间对器件性能的影响做了具体研究.借助高分辨透射电镜,研究该金属氧化物半导体材料晶型结构和器件形貌.进一步通过X 射线光电能谱测试,研究了N2O 等离子体处理对薄膜影响的机理.

2 背沟道刻蚀金属氧化物薄膜晶体管器件制备与性能

2.1 PITZO-TFT 器件制备

如图1(a)所示,本文所用器件均采用BCE 型结构.首先,采用直流磁控溅射的方式在玻璃衬底上溅射一层200 nm 厚的金属钼 (Mo)栅极薄膜,利用湿法刻蚀对栅极薄膜进行图形化.通过等离子体增强型化学沉积 (plasma enhanced chemical vapor deposition,PECVD) 技术制备双层堆叠的栅绝缘层,和栅极金属Mo 层接触的下层为250 nm 厚的氮化硅薄膜,上层为50 nm 厚的二氧化硅薄膜,并利用干法刻蚀进行图形化.然后,通过磁控溅射的方式分别制作一层30 nm 厚的PITZO (Pr/In/Sn/Zn=0.2/2/0.5/1 mol) 薄膜作为薄膜晶体管器件的有源层,并利用草酸进行图形化.随后,采用直流磁控溅射方式制备一层200 nm 厚的Mo 金属作为源漏电极层;采用铝酸刻蚀液,以湿法刻蚀方式进行源漏电极的图形化.接着,利用PECVD腔室分别对器件进行不同条件的N2O 处理.具体地,保持处理时间为30 s 不变,设置N2O 的功率分别为0,50,150 W,对应的器件分别标记为Device A,Device B,Device C;以及保持N2O 的功率为150 W 不变,设置处理时间分别为10 和60 s,对应的器件分别标记为Device D,Device E.在N2O等离子体处理后不破真空,利用PECVD 制作一层300 nm 厚的二氧化硅薄膜作为钝化层,并采用干法刻蚀进行薄膜图形化.最后,所有器件在350 ℃的空气氛围中退火60 min.制备的器件显微镜图如图1(b)所示,各膜层轮廓清晰可见.

图1 PITZO-TFT (a)结构示意图;(b) 器件显微镜照片Fig.1.(a) Structure diagram and (b) microscope photo of the PITZO-TFT.

2.2 PITZO-TFT 器件性能

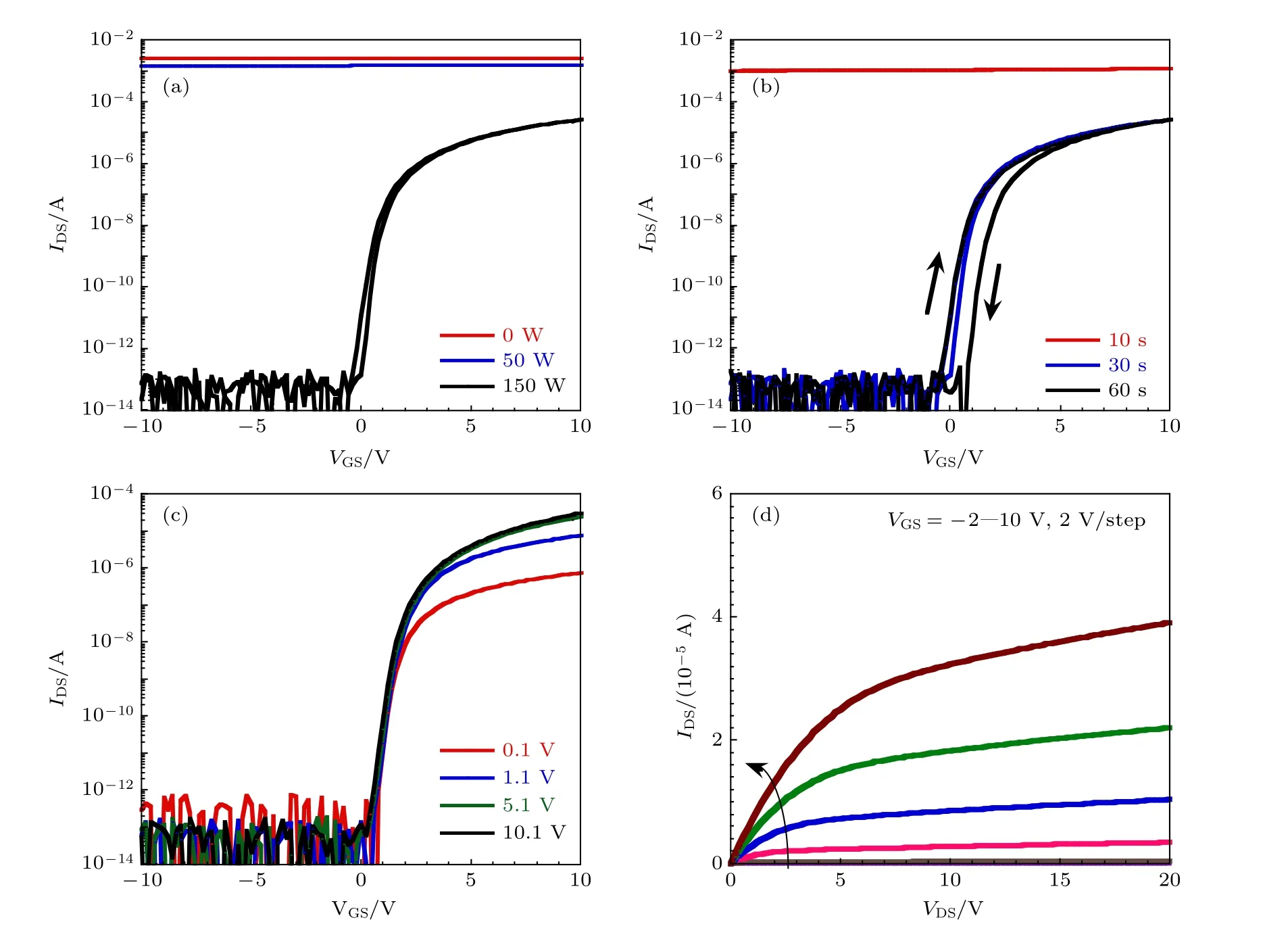

首先,固定N2O 等离子体处理时间为30 s,不同功率处理下的器件转移曲线如图2(a)所示.很显然,无N2O 等离子体处理 (0 W)和低功率 (50 W)处理条件下的器件都处于“导通”状态,二者均无开关特性;增加N2O 等离子处理功率至150 W 后,器件 (Device C)表现出了良好的开关特性.本文中器件沟道宽长比 (W/L)均为20/10 μm,转移曲线中固定源漏电压 (VDS)为10.1 V,器件阈值电压 (Vth)定义为转移曲线中源漏电流 (IDS)为1 nA时对应的栅极电压 (VGS).通过相关参数提取可得(如表1 所列),器件Device C 对应的阈值电压Vth为0.7 V,器件饱和迁移率 (μsat)为22.4 cm2·V—1·s—1,亚阈值摆幅 (SS) 为0.17 V/decade,电流开关比(Ion/Ioff) 约为108.进一步地,在保持N2O 等离子体处理功率为150 W 的基础上,设置处理时间分别为10,30 和60 s.如图2(b)所示,当处理时间为10 s 时,器件Device D 处理“导通”状态;随着处理时间增至30 s,也即Device C,器件表现出了良好的开关特性,无明显的磁滞效应;当进一步增加时间至60 s 后,器件Device E 依然表现出了开关特性,但是“磁滞”效应明显增强.和Device C 比较而言,Device E 的Vth稍有负向偏移(0.4 V),器件μsat稍有降低 (约20.6 cm2·V—1·s—1),亚阈值摆幅退化为0.22 V/decade,Ion/Ioff保持约为108.其次,为进一步评估优化器件Device C 的电学特性,图1(c)给出不同源漏电压 (VDS=0.1,1.1,5.1,10.1 V)下的转移特性曲线,可以看出,器件未表现出“漏诱导势垒变低”的现象.另外,器件Device C 的输出特性曲线如图1(d)所示,无电流拥挤现象,说明源漏电极和沟道层接触良好,而且器件表现出了良好的饱和特性,这为器件的实际应用提供了坚实的基础.

图2 (a)不同功率和 (b) 不同时间的N2O 处理对器件转移特性的影响;Device C (c) 不同源漏电压下的转移特性曲线和 (d) 输出特性曲线Fig.2.Influence of different (a) power and (b) time treatment of N2O on the transfer characteristics of the device;(c) transfer characteristic curve under different source and drain voltages and (d) output characteristic curve of Device C.

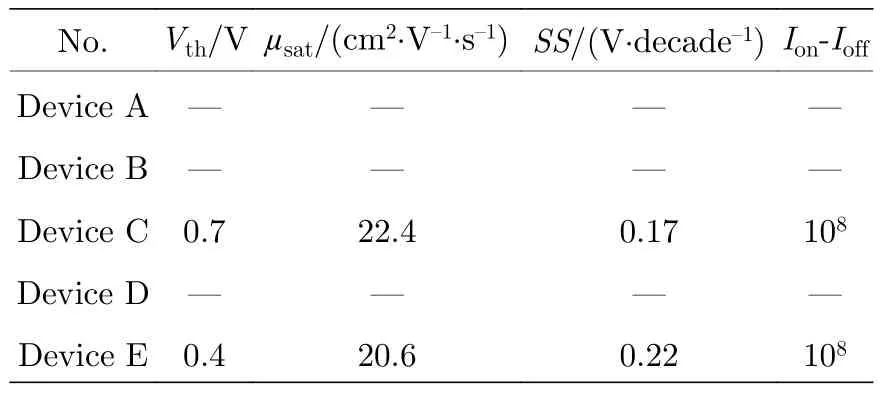

表1 各器件性能参数表Table 1.Electronic parameters of each TFTs.

根据以上结果可知,在湿法背沟刻蚀金属氧化物薄膜晶体管的制备中,器件背沟道受制备工艺影响较大.未经N2O 等离子体处理的薄膜晶体管直接表现出“导通”状态,说明沟道层中载流子浓度过高,该区间栅压无法起到调控效果.通过引入N2O 等离子体处理,可以有效改善器件的开关特性;而且,N2O 等离子体处理的功率和时间对器件性能的影响非常明显,合适的功率和时间窗口是获得器件优化性能的关键.因此,有必要对其改善机理做进一步的研究.

3 实验结果与分析

3.1 器件偏压稳定性评估

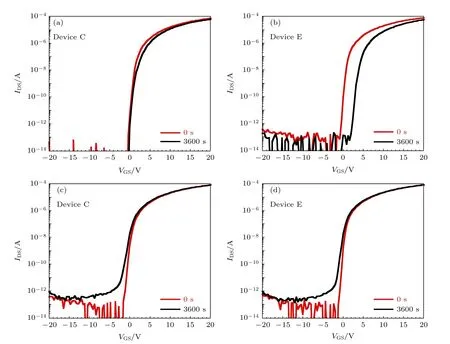

图3(a)和图3(b)分别为Device C 和Device E在正向偏压下的热稳定性 (positive bias temperature stress,PBTS)表征结果.其评估方式为:设置测试机台的温度为60 ℃,先测试初始状态下的器件转移特性曲线 (VGS=—20—20 V 扫描,VDS=10.1 V),紧接着加上一定的偏压 (VGS=20 V,VDS=0 V,T=60 ℃),保持3600 s 后再次测试器件的转移特性曲线,得到器件转移特性的变化情况.图3(a)和图3(b) 的结果表明,N2O 等离子体处理时间从30 s 增加至60 s 后,器件PBTS 的阈值电压漂移量从0.2 V 退化为3.1 V.对比Device C 和Device E 的结构和制备工艺,可推断其和器件背沟道的状态直接相关.根据Sheng 等[17]和Nahm 等[18]的研究结果,过多的氧诱导的缺陷态可能是其PBTS 稳定性退化的原因.简单而言,长时间的N2O 等离子体处理产生的过量的氧间隙态作为电子俘获中心,从而导致了器件PBTS 稳定性退化,后面将做进一步的验证.

进一步地,为评估N2O 等离子体处理的实用性,有必要对器件在光照条件下的负偏压热稳定性(negative bias illumination temperature stability,NBITS) 进行表征.NBITS 的测试方式为:设置测试机台的温度为60 ℃,先测试初始状态下的器件转移特性曲线 (VGS=—20—20 V 扫描,VDS=10.1 V),接着加上一定的偏压 (VGS=—20 V,VDS=0 V,T=60 ℃,白色LED 光源直接照射沟道区域,光强为5000 nits),保持3600 s 后再次测试器件的转移特性曲线,得到器件转移特性的变化情况.需要说明的是,该实验中加偏压后测试转移曲线时光源未关闭.Device C 和Device E 的NBITS稳定性分别如图3(c)和图3(d) 所示,可以看出,二者均表现出了良好的NBITS 稳定性,Vth漂移仅为—0.5 V.根据我们前期的研究结果[8,19,20],稀土镨元素的掺入,会在导带底附近引入“缺陷”态,其可作为光生载流子的快速复合中心.需要指出的是,虽然Device E 的背沟道界面具有相对较多的缺陷态,但是其NBITS 稳定性依然能保持和Device C 相当.很显然,稀土镨元素的掺入可以有效地提高器件的NBITS 稳定性.

图3 (a) Device C 和 (b) Device E 器件在PBTS 条件下的稳定性;(c) Device C 和 (d) Device E 器件在NBITS 条件下的稳定性Fig.3.Stability of (a) Device C and (b) Device E under PBTS conditions;stability of (c) Device C and (d) Device E under NBITS conditions.

3.2 薄膜晶体管的高分辨透射电镜分析

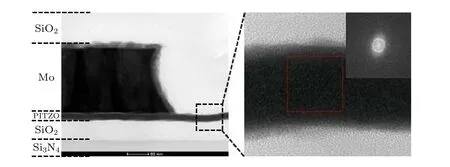

对于高可靠的薄膜晶体管而言,完整的器件结构是首先必须满足的前提条件.因此,在前面光学显微镜的基础上,有必要进一步评估该BCE 结构PITZO-TFT 的微观形貌结构.图4 所示为Device C 的高分辨透射电镜 (transmission electron micrography,TEM)图谱.很显然,该截面TEM 图中各膜层结构清晰可见,厚度和制备参数符合较好.需要特别指出的是,PITZO 薄膜虽然经历强酸的源漏电极刻蚀过程,但是无明显被刻蚀的迹象;而且,其上未发现有明显的刻蚀残留,表明PITZO 薄膜可以有效抵抗该强酸的刻蚀,具有较强的抗酸刻蚀特性.另外,在金属Mo 电极上有一薄氧化层,应该和N2O 等离子体处理相关.进一步,对PITZO薄膜的晶型结构进行分析,从快速傅里叶变换图可以清楚地判断其为非晶结构,由于不存在晶界的问题,这保证了其在大尺寸面板中应用的可能.

图4 TFT 器件的高分辨透射电镜谱图Fig.4.High-resolution transmission electron microscope spectra of TFT devices.

3.3 薄膜X 射线光电子能谱分析

在明确了器件性能和结构方面的信息后,有必要对N2O 等离子体处理的机理做深入的研究,因其对高性能器件的实现起到至关重要的作用.首先在玻璃基板上制备两个和器件相同溅射条件下100 nm 厚的PITZO 薄膜,然后把其中一个薄膜在N2O 等离子体中进行和器件 (Device C,150 W,30 s)制备处理一致的工艺过程,再分别对这两种薄膜进行X 射线光电子能谱 (XPS)深度剖析测试.

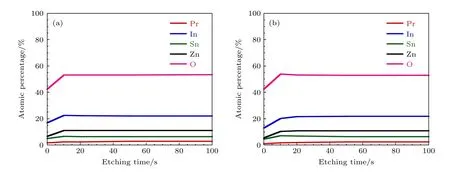

首先,两种薄膜中各元素随刻蚀 (Ar 离子枪)时间的分布结果如图5(a)和图5(b) 所示,其中图5(a)为未经N2O 等离子体处理的薄膜样品,图5(b)为经N2O 等离子体处理的薄膜样品.从图5 可知,从元素原子含量的角度而言,二者均在表面存在一个界面区域,未经N2O 等离子体处理的样品界面小于2 nm (Ar 离子枪刻蚀速率约为2 A/s),而经N2O 等离子体处理的样品的界面区域扩展到小于4 nm.更深区域的元素分布无明显区别,可以推断该N2O 等离子体处理条件仅影响距离薄膜表面几个纳米深度区域.另外,对比两种薄膜各元素含量的变化,未经处理的薄膜表面铟原子百分比约为16.9%,而经N2O 等离子体处理的薄膜表面铟原子百分比为12.9 %,其他主体元素含量未有明显区别.但是,在距离薄膜表面4 nm深度后,二者各元素含量无明显区别.考虑到铟在金属氧化物半导体薄膜中是提供载流子迁移的通道[21],即N2O 等离子体处理会有降低迁移率的趋势.因此,这也许是Device E 的迁移率和Device C 相比稍低的原因.

图5 PITZO 薄膜的深度剖析X 射线光电子能谱图 (a) 无N2O 处理;(b) N2O 处理后Fig.5.X-ray photoelectron spectroscopy depth-profile of PITZO films:(a) Without N2O treatment;(b) with N2O treatment.

另外,上述两种薄膜中氧元素 (O 1s)的X 射线光电子能谱和氩离子刻蚀时间的关系图谱如图6(a)和图6(b) 所示.对于未经N2O 等离子体处理的薄膜,其O 1s 的峰位变化主要表现在0 和10 s 之间 (向低结合能方向偏移0.3 eV),10 s 之后无明显位移.而经N2O 等离子体处理的薄膜,其O 1s 的峰位变化表现为0 和50 s 之间(向低结合能方向递进偏移0.3 eV),50 s 之后无明显位移.因此,从元素峰位的角度而言,该N2O 等离子体处理条件的影响深度约为距离薄膜表面10 nm.进一步地,对上述两种薄膜表面 (对应0 s)的O 1s 进行高斯分峰拟合,图6(c)和图6(d) 分别对应未经N2O 等离子体处理和经N2O 等离子体处理的薄膜样品.其中O 1s 图谱可以拟合成3 个高斯峰,OM(529.8 eV),O-V(530.7 eV)和 O-A(531.7 eV),分别代表金属结合氧、缺位氧和吸附氧,通过拟合峰面积可推知各峰位的占比情况.从图6(c)和图6(d) 可知,经N2O 等离子体处理后,薄膜中的O-V 占比由24.4 %降为14.6 %,表明薄膜中的氧空位浓度有一定程度的降低.大量的研究表明[22],金属氧化物半导体中氧空位是其载流子的一个主要来源,也即薄膜中载流子浓度会有一定程度的降低.这和我们霍尔测试的结果相符合,其载流子浓度由未处理时的3.46 × 1018cm—3降低至处理后的4.49 × 1016cm—3.需要特别指出的是,未经N2O等离子体处理的薄膜中O-A 占比为5.7 %,而经N2O 等离子体处理的薄膜中O-A 占比高达32.9%.上述结果表明,N2O 等离子体处理能在薄膜表面形成一个富氧、低载流子浓度的界面层.

图6 PITZO 薄膜在 (a) 无N2O 处理和 (b) N2O 处理后O 1s 的XPS 谱图随刻蚀时间的关系;Ar 离子枪刻蚀前 (c) 无N2O 处理和 (d) N2O 处理后薄膜O 1s 的拟合XPS 图谱Fig.6.The O 1s XPS spectra of the PITZO films (a) without N2O and (b) with N2O treatment related with the Ar ion gun etching time.Fitted O 1s XPS of the PITZO thin films (c) without N2O and (d) with N2O treatment before Ar ion gun etching.

根据相关的研究报道[14,16,23],类似的背沟道刻蚀型结构的器件呈“导通”状态(失去栅控的开关特性),其原因主要有两种情况.其一是器件的背沟道区域存在成分的偏析,即存在低电阻率(如高铟含量)的界面层,使得器件处于“导通”状态;另外一种是在PECVD 沉积二氧化硅钝化层的时候引入过多贡献电子的氢,以及由于等离子体轰击的影响而产生额外的缺陷.因此,通常钝化层沉积后,器件需要进行退火等相关工艺的处理.我们的器件亦存在该现象(见图2),未经处理的器件处于“导通”状态,只有当N2O 等离子体处理的功率增加至150 W,处理时间大于30 s 后,器件才表现出正常的开关特性.结合前面高分辨透射电镜的表征结果,器件的沟道层和氧化硅层的界面清晰,未发现有成分偏析层;而且沟道层未有明显被刻蚀的现象.我们推断,器件处于“导通”状态主要和钝化层的制备过程有关.根据XPS 表征的结果,N2O 等离子体处理的沟道层薄膜在表面存在一个富氧、低载流子浓度的界面层.因此,我们推测N2O 等离子体处理一方面能对器件背沟道的一些原子或分子基团进行化学氧化和物理轰击,在背沟道界面形成一个富氧、低载流子浓度的界面,可以有效抵抗PECVD 沉积氧化硅时氢的引入和等离子体轰击的影响.原因可能是弱结合的吸附氧可以作为氢的钝化体,抑制作为施主的低能级间隙氢的产生,这和Kang[24]等的研究有类似的效果.具体地,当N2O 等离子体处理功率较低或时间较短时,形成的界面层不足以抵抗PECVD 沉积氧化硅时的影响,器件表现为“导通”状态.另一方面,当N2O 等离子体处理时间过长时,产生了过多的吸附氧态,从而引入了过量的电子缺陷[25],致使器件的“磁滞”现象明显和PBTS稳定性的退化.因此,合适的N2O 等离子体处理条件是获得优化器件性能的关键,需要根据具体材料具体设定.以上可知,N2O 等离子体处理是一种低成本、高效的薄膜晶体管性能优化方式,其在低温工艺或溶液法工艺中可能会有一些特别的应用,相关研究还在进行中.

4 结论

本文通过采用稀土元素镨掺杂铟锡锌氧化物半导体作为薄膜晶体管沟道层(能有效抵抗铝酸的刻蚀),成功实现了基于强酸的湿法背沟道刻蚀薄膜晶体管的制备.进一步引入N2O 等离子体处理薄膜晶体管的背沟道界面的方式,对处理功率和时间对器件性能的影响做了具体的研究.结果表明,在一定的功率和时间处理下能获得良好的器件性能,所制备的器件具有良好的PBTS 和NBTIS 稳定性.高分辨透射电镜结果显示,该非晶结构的金属氧化物半导体材料可以有效抵抗铝酸的刻蚀,在器件的制备过程中未见其厚度有明显的变化.进一步的X 射线光电能谱测试表明,N2O 等离子体处理能在界面处形成一个富氧、低载流子浓度的界面层,有效地修复器件背沟道的损伤以及抵抗钝化层沉积的影响.本文提供了一种低成本、高效的薄膜晶体管性能优化方式,在实际产业化中具有广阔的应用前景.