一种集成无源电容式高硅铝合金基微波功率芯片载体技术

刘米丰,任卫朋,赵 越,陈 韬,王盈莹

(上海航天电子通讯设备研究所,上海 201109)

以微波收发组件为核心的有源相控阵雷达具有快速扫描、数字波束形成以及空间功率合成等优点,可同时完成预警、跟踪制导和火力控制等多种功能,具有非常强的多目标处理能力,是现代作战体系依赖的先进设备[1-4]。

作为微波收发组件的核心器件之一,微波功放芯片的作用是将低功率的射频信号放大成高功率的射频信号,直接决定了雷达的最大探测距离和抗干扰等关键性能。由于微波功放芯片在工作过程中会产生大量的热量,需要及时、高效地将热量导出,否则会出现芯片失效、烧毁等现象。同时,微波功放芯片与微波组件壳体材料的热膨胀系数(CTE)不一致,需要在两者之间设置过渡结构,从而降低热应力对微波功放芯片的冲击,提高微波组件的可靠性[5-7]。

高硅铝合金材料因具有高导热、低CTE、低成本以及可加工性高等优点,可满足微波功放芯片对芯片载体的要求[8-11]。因此,本文提出了一种基于高硅铝合金基底的一体化集成功率芯片载体,其主要特点是在高硅铝合金基板上集成了含薄膜电容和导线的内匹配电路,可减少后续芯片电容贴装工序,提高微波组件的生产效率与可靠性。

1 高硅铝合金基薄膜电容制备

1.1 高硅铝合金基板表面前处理

一体化集成芯片载体的薄膜电容结构要求高硅铝合金衬底表面平整、光滑且不能有裂纹等缺陷,否则就无法在衬底表面形成致密、无缺陷的薄膜电容介质层,并导致电容短路、击穿电压降低以及漏电流增加等问题。此外,一体化芯片载体的焊接膜层粗糙度也与高硅铝合金衬底表面粗糙度相关,而低粗糙度的焊接膜层是实现高质量、低空洞率共晶焊接的关键因素之一。因此,首先需要采用高硅铝合金表面处理技术,以获得具有无裂纹、平坦化的高硅铝合金基板表面。

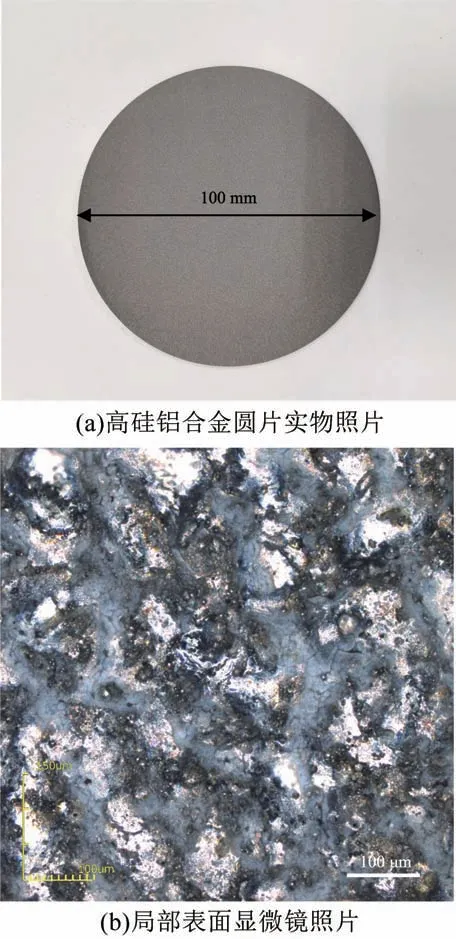

采用机械加工方式将高硅铝合金块材加工成直径100 mm、厚度1.2 mm 的高硅铝合金(70Si30Al,CTE=7)圆片,利用光学数码显微镜(Olympus OLS4100)对高硅铝合金圆片表面进行三维建模,得到检测结果如图1 所示,其表面存在大量的瘤状物,粗糙度也高达2.917 μm。

图1 高硅铝合金圆片初始表面形貌Fig.1 Initial morphology of high Si-Al alloy wafer

由于高硅铝合金圆片表面的瘤状物尺寸在几十微米以上,因此先采用机械研磨方法将基板表面的瘤状物研磨去除,再采用化学机械抛光(Chemical Mechanical Polishing,CMP)技术将表面粗糙度降至纳米级。此外,由于高硅铝合金圆片存在铝与硅晶胞混合的复杂表面,要求CMP 抛光液能同时对铝和硅起化学反应。因此,选择Logitech 公司的SF6 型碱性溶液作为高硅铝合金圆片的抛光液,该抛光液主体成分是纳米级的硅溶胶、无机碱、络合剂以及螯合剂,并通过用去离子水对原液进行稀释,将抛光液pH 值调节至8 左右。

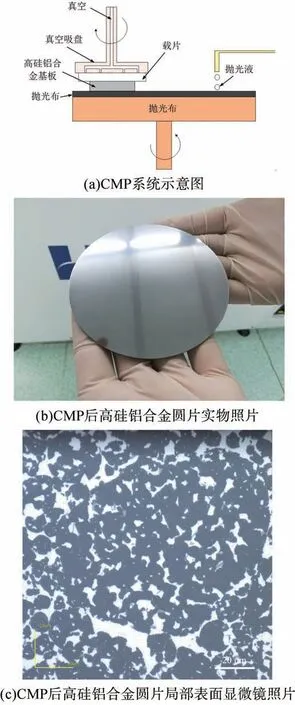

图2(a)所示为Logitech 公司的PM5 型CMP 系统,该系统由真空吸盘、抛光盘和抛光液三个主要部分构成。将研磨后高硅铝合金圆片用石蜡粘贴到直径100 mm 的玻璃圆片正面,然后利用真空将玻璃圆片背面吸附到减薄抛光机的真空吸盘上,并将上转盘倒置到抛光盘上,就可实现高硅铝合金圆片的研磨加工。设置抛光盘转速为70 r/min,真空吸盘上施加6 kg 的压块,设置抛光时间为1 h。完成CMP 后,通过光学数码显微对抛光后的高硅铝合金圆片进行三维建模,可得高硅铝合金圆片的表面粗糙度降低至23 nm,满足后续薄膜加工需求,如图2(b)和(c)所示。

图2 高硅铝合金圆片表面平坦化Fig.2 Surface planarization of high Si-Al alloy wafer

1.2 Ta2O5-Al2O3混合介质层薄膜电容制备

薄膜电容的比容量与电极相对面积、介质材料介电常数以及介质层厚度相关。而增大薄膜电容面积则会导致一体化芯片载体面积增大,进而对微波组件的高密度集成和低成本形成不利影响。因此,为了获得更大比容量的薄膜电容,只能增加薄膜电容的介质层厚度或者选择更大介电常数的介质材料。相比于常规的SiO2材质介质层,薄膜形态Ta2O5的相对介电常数可达到18~28,是SiO2薄膜的6~8 倍[12-17]。此外,由于Ta2O5具有良好的热、化学稳定性,因此选择其作为功率芯片一体化集成载体的薄膜电容的介质层。

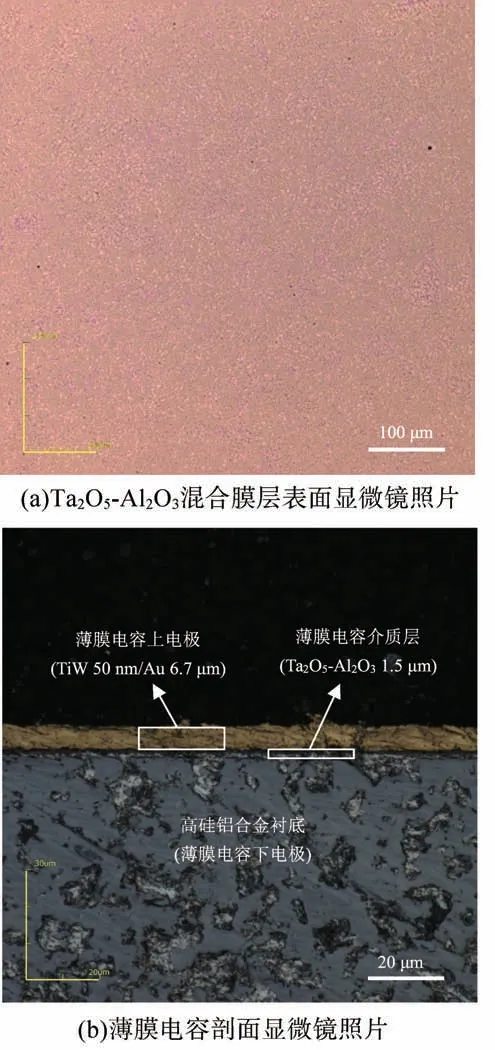

在高硅铝合金基板表面制备Ta2O5膜层时需要考虑与Ta2O5与铝硅界面的结合力。为此,采用美国丹顿DISCOVERY 635 磁控溅射仪器在高硅铝合金基板表面溅射一层Ta-Al 混合薄膜层,具体制备工艺参数为:Ta 靶功率为400 W、时间4000 s,Al 靶功率为400 W、时间1000 s。通过台阶仪(KLA Tencor ASIQ3) 对Ta-Al 混合膜层厚度进行测量,测试结果为1.5 μm。然后,将高硅铝合金基板放入质量分数0.1%的柠檬酸溶液中进行阳极氧化,氧化电压为200 V,溶液温度低于10 ℃,氧化时间为20 min,阳极氧化完成后用去离子水冲洗10 min 并氮气吹干。图3(a)为Ta-Al 混合膜层阳极氧化后的显微镜照片,采用万用表对该膜层进行电测试,测试结果表明接触膜层的表笔与接触基板背面的表笔之间为绝缘,由此得到该混合膜层已经被阳极氧化成Ta2O5-Al2O3混合膜层。在Ta2O5-Al2O3混合膜层表面通过磁控溅射TiW(50 nm)/Au(100 nm)种子层并采用电镀将Au 膜层加厚至6 μm以上,形成薄膜电容上电极,从而实现高硅铝合金基薄膜电容的制备,如图3(b)所示。通过半导体参数分析仪(Keysight B1500A),采用4 端对(4TP)测量方法对薄膜电容的比容量进行测试,测试结果约为7 μF/mm2。

图3 高硅铝合金基薄膜电容Fig.3 Film capacitance based on high Si-Al alloy substrate

2 一体化集成功率芯片载体制备

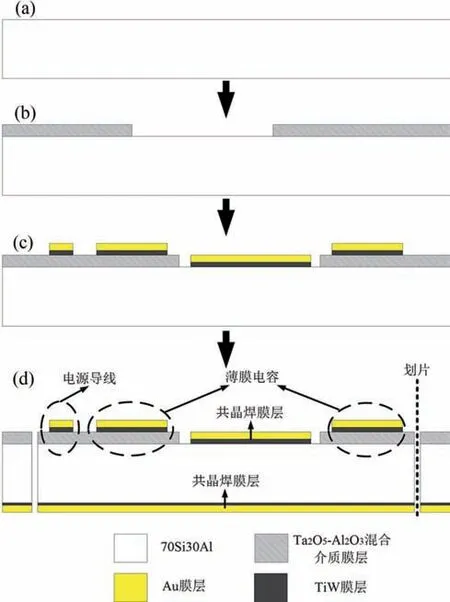

在高硅铝合金基薄膜电容制备技术基础上,开发了一体化集成功率芯片载体制备的工艺流程,具体如下:

(1)对线切割后的高硅铝合金基板表面进行研磨和CMP 处理,完成后用丙酮超声清洗将基板表面的石蜡去除干净,然后用去离子水冲洗并用氮气吹干,如图4(a)所示;

(2)在表面处理后的高硅铝合金上表面通过磁控溅射沉积一层厚度为1.5 μm 的Ta 和Al 混合膜层,然后在质量分数0.1%、10 ℃的柠檬酸溶液内进行200 V的阳极氧化20 min,将Ta-Al 混合膜层氧化成Ta2O5-Al2O3混合膜层,通过光刻技术在基板的薄膜电容区域覆盖上光刻胶,然后浸入HF 溶液(HF 与H2O 质量比为1 ∶50)中4~6 min,去除薄膜电容区域外的混合介质层,如图4(b)所示;

(3)在完成薄膜电容介质层制备的基板上,表面采用磁控溅射一层TiW/Au(50 nm/200 nm)种子层,然后采用图形电镀技术将薄膜电容电极、焊接膜层和导线的金层加厚至6.7 μm,最后将光刻胶掩膜和TiW/Au 种子层去除,便可同时形成薄膜电容电极、焊接膜层和导线结构,如图4(c)所示;

(4)最后在基板背面通过磁控溅射和电镀形成一层TiW/Au(50 nm/2 μm)膜层作为下表面的焊接膜层,并通过划片完成功率芯片一体化集成载体的制备,如图4(d)所示。

图4 一体化集成芯片载体制备工艺流程Fig.4 Process of the integrated chip carrier

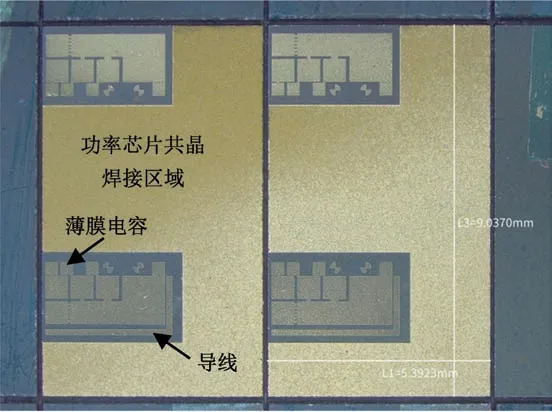

按照上述工艺流程,完成微波组件的一体化集成功率芯片载体制备,实物照片如图5 所示,单个载体内部含有8 个集成薄膜电容和一个导线。

图5 一体化集成功率芯片载体样品实物Fig.5 The integrated power chip carrier samples

根据功率芯片对匹配电容的要求,要求每个薄膜电容的电容值在50~100 pF 范围内,且其中3 个薄膜电容需进行并联。采用万用表测得3 个并联电容的容值约为187 pF,独立电容的容值约为70 pF,满足功率芯片的外围电路匹配要求。

3 应用与讨论

3.1 微波组件应用

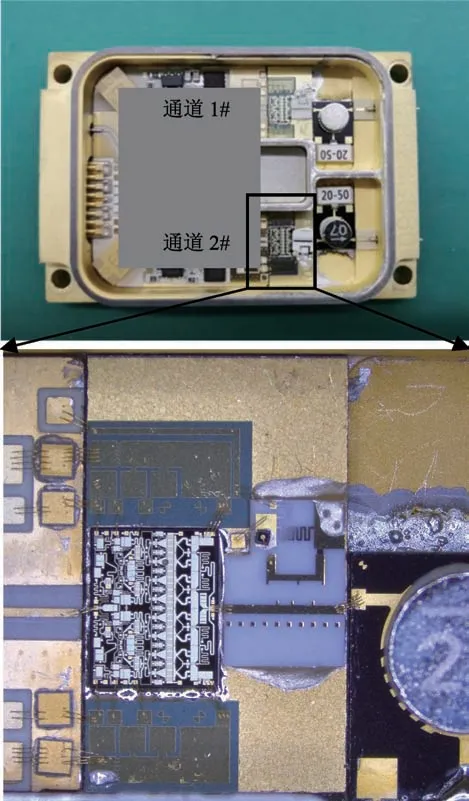

先利用自动共晶焊接技术将GaAs 功率芯片焊接到一体化集成功率载体的焊接区域上。然后通过金丝引线键合技术实现功率芯片与内匹配电路的电互连,完成T/R-MMICs 模块制备。最后将整个TR-MMICs模块通过焊料焊接方式装配到组件壳体中,并利用金丝键合将其与微波组件基板、环隔器等进行互连,完成某型号双通道微波发射组件制备,如图6 所示。

图6 基于一体化功率芯片载体的双通道微波组件实物Fig.6 Double-channel microwave module based on integrated power chip carrier

3.2 性能测试

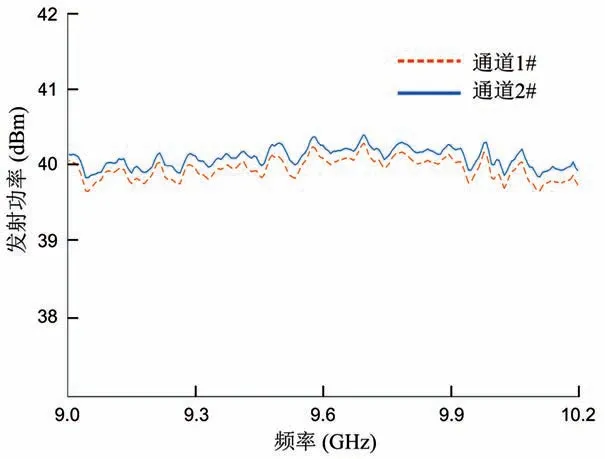

采用射频功率计(BOONTON 4500B)对微波组件发射功率进行测试,测试结果如图7 所示,在9~10.2 GHz 频率范围内,通道1#的发射功率大于39.473 dBm(约9.8 W),通道2#的发射功率大于39.801 dBm(约9.6 W),满足组件设计要求。

图7 微波组件发射功率测试结果Fig.7 Transmission power test result of microwave module

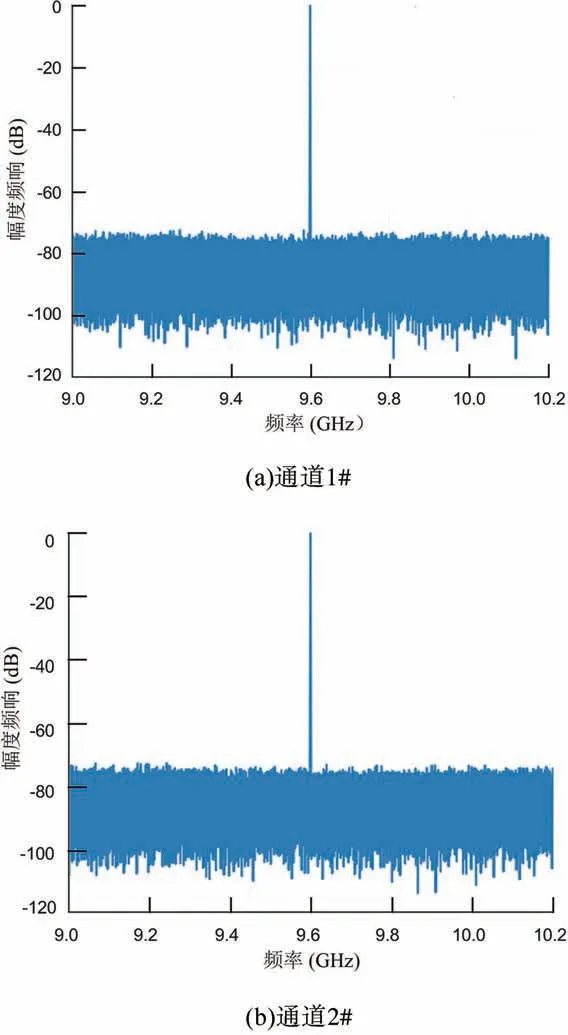

采用射频功率计(Agilent E4440A)对微波组件杂散抑制进行测试,测试结果如图8 所示。由图8 可知,在9~10.2 GHz 频率范围内,通道1#杂散抑制约为-76.24 dB,通道2#杂散抑制约为-75.09 dB,满足组件设计要求。

图8 微波组件杂散抑制测试结果Fig.8 Spurious suppression test result of microwave module

4 结论

通过CMP 技术实现了表面粗糙度为23 nm 的高硅铝合金圆片制备;利用磁控溅射和阳极氧化技术在高硅铝合金表面实现了厚度1.5 μm 的Ta2O5-Al2O3混合膜层的制备;基于Ta2O5-Al2O3混合介质层的薄膜电容的比容量约为7 μF/mm2。

制备了基于高硅铝合金基板的一体化集成功率芯片载体,集成了薄膜电容和导线的内匹配电路,单个薄膜电容的电容值约为70 pF。将一体化集成功率芯片载体应用到了某型号的双通道微波发射组件中,发射功率的测试结果为9.8 W(通道1#)/9.6 W(通道2#),杂散抑制的测试结果为-76.24 dB(通道1#)/ -75.09 dB(通道2#),测试结果满足设计指标要求。

由于高硅铝合金基一体化集成功率芯片载体不仅可以减少微波组件组装步骤,而且能提高集成密度,同时自身还具备批量化制造优势,因此该技术在高功率微波组件中的应用前景十分广阔。