一种基于FPGA 对主从通信的优化设计

黄姣英,李胜玉,高 成,杨达明

(北京航空航天大学可靠性与系统工程学院,北京 100191)

RS 485 是一种采用差分收发形式的串行通信标准,采用其标准的主从通信具有传输距离长、速度较高、电平兼容性好、使用灵活方便、成本低廉和可靠度高等优点,并在监测、交通、工业自控中广泛应用[1-4]。魏金文等人提出了一种基于嵌入式的RS 485 多机通信方案探究,分析了普通自动地址识别模式通信下存在的隐患和传输系统效率低下的原因[5]。鄢涛等提出一种基于FPGA 和外接1 MB SRAM,并采用RS 485 标准的数据通信协议的点对点传输设计[6]。刘纯提出基于FPGA 的RS 485 主从通信协议,实现了点对多的高速数据传输[7]。白曦提出一种基于状态机的RS 485 总线的主从通信方法,解决了主从设备收发冲突问题[8]。

本文基于FPGA 在RS 485 主从通信接收端利用串并转换模块对数据进行识别过滤,采用双口RAM 替代传统FIFO,使得上位机PC 可以灵活读取缓存数据。实验结果证明,整个主从系统传输效率得到提升,数据接收端每步采用反馈机制,提高了传输系统的可靠性。

1 数据帧格式

8B/10B 编码内含有一些特殊字符,可用作帧同步字符和其他的分隔符或控制字符,有助于比特流的码组定位和信息识别[9-10]。根据同步高速协议标准把传输帧格式的帧头定义为8B/10B 编码中的K28.5 字符“0101111100”,帧尾采用K28.1 字符“1001111100”。在任意数据组合中,K28.5 与K28.1 只作为控制字符出现,而在数据部分不会出现,因此可以有效地避免帧同步的假同步现象,如图1 所示。

图1 帧格式

Label 可以根据接收端点个数进行设计,本次拟采用2 bit,分别为00,01,10,11。User data 可以根据用户自己定义,本次采用7 bit,每个DATA 都采用1 bit 奇偶校验。为避免传输数据混乱和传输效率低下的现象,发送端和接收端的DATA 格式统一采用包括Label 和Parity 在内的10 bit格式,如图2 所示。

图2 DATA 格式

2 主从通信方案设计

RS 485 主从通信结构如图3 所示,发送端由上位机PC 下达数据发送指令到数据发送端FPGA,发送端与接收端均采用Xilinx 公司的Spartan 6 系列FPGA。串行数据通过ADM2582E 集成式隔离数据收发器使得TTL 电平与差分信号相互转换,最后数据由接收端FPGA 接收。接收端上位机PC 通过基于AU9254A21 的USB 集线器向数据接收端FPGA 采集数据,验证主从通信系统的可靠性和完整性。

图3 主从通信结构图

2.1 接收端设计

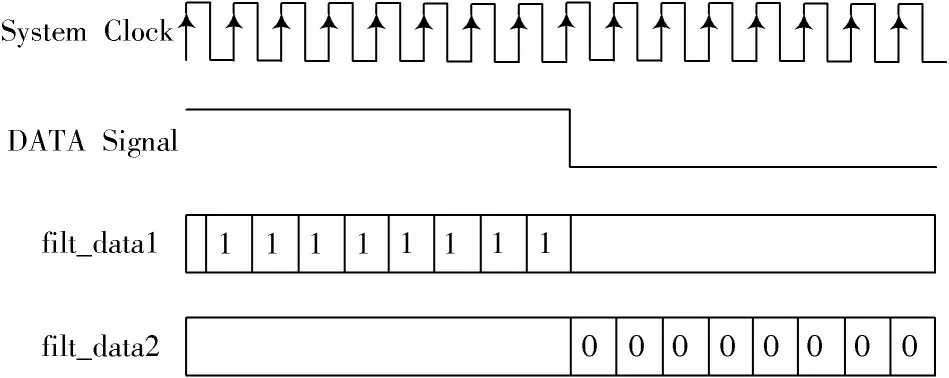

接收端在接收数据前需要预设置,为达到高精度采样,本设计以最高系统时钟50 MHz 进行位同步采样,高速数据传输需要进行位同步与数据帧同步[11]。首先进行位同步,接收端把每次在系统时钟条件下采样的数据存放在2 个10 bit 寄存器,当filt_data1 寄存器为1 与filt_data2 寄存器为0 时即证明接收数据开始,见图4。

图4 位同步示意图

当检测到位同步时,串并转换模块向采样时钟模块传递一个使能启动信号,采样时钟开始对数据进行采样,如图5 所示。本设计采用10 MHz 的采样时钟与数据传输速率相匹配,在设置一个10 bit 移位寄存器条件下,每10 bit 串行数据进行一次串并转换,当该寄存器完整收到编码中的K28.5 字符“0101111100”时,证明位同步和帧同步已完成。

图5 接收端结构图

2.2 数据识别功能与双口RAM 设计

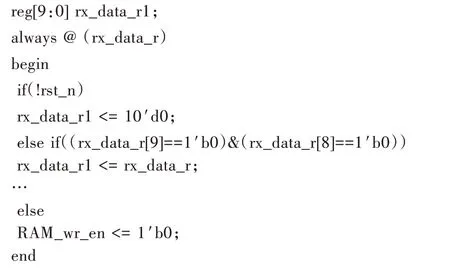

本设计把数据识别过滤功能融入到了数据串并转换模块中,首先对接收到的数据进行Label 识别判断,如果符合本接收端数据,则转移到双口RAM;如果不符合,直接对冗余数据进行过滤。然后基于状态机设计了一种反馈装置,当帧同步检测、奇偶校验和双口RAM 任意一步发现数据错误即向上位机报错,中止后续数据传输操作,如图6 所示。数据识别过滤部分代码如下:

根据本次主从通信所传输的数据格式可知,基于FPGA 设计的双口RAM 是具有两套完全独立的数据线、地址线和读写使能线,并允许两个独立的系统同时对其进行随机性访问的存储器,即共享多端口存储器[12-15]。基于ISE 软件采用Verilog 语言设计的双口RAM 如图7所示。上位机PC 可以通过寻址读取RAM 里任意数据,并且整体上读写可以同时进行,比传统FIFO 更具有灵活性。

图7 双口RAM 设计图

双口RAM 有两组输入、输出数据线(RAM_wr_data& RAM_rd_data);两组地址(RAM_write_addr &RAM_read_addr);两 个 使 能 端(RAM_wr_en &RAM_rd_en),一个端口只读,另一个端口只写,见表1。

表1 部分端口注释表

3 数据分析

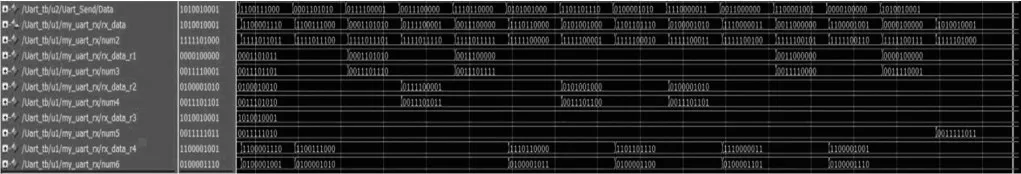

为模拟RS 485 主从通信数据传输,本文采用Matlab 随机函数y=dec2bin(randi([0,1 023],1 000,1),10)生成一组1 000 个10 bit 0~1 024 的数据,最后把生成的随机数据复制在上位机PC 来进行总线数据传输。为进一步提供大量实验样本,本文利用搭建的主从通信传输平台完成数倍于样本的数据并且进行100 次传输。某次传输数据仿真如图8 所示,主发送端数据定义为Uart_Send/Data,从属接收端识别寄存器数据定义为rx_data,4 个接收端ram 分别定义为rx_data_r1、rx_data_r2、rx_data_r3 和rx_data_r4。为核算每次传送数据是否存在丢帧现象,本次优化设计为每个寄存器配备数据计数器,分别定义为num2,num3,num4,num5 和num6,误码率定义为rxw。

图8 RS 485 模块发送和接收数据仿真图

本文随机抽取5 组数据,并与常规接收端的缓存数据进行对比,如表2 所示。

表2 优化设计与常规设计缓存数据对比

由第1 组数据可知,常规型主从通信当每个接收端接收到1 000 个数据时传递给缓存器,本设计的第一个接收端根据识别传递到RAM 寄存器为241 个数据,较常规优化率为75.9%;第二个RAM 寄存器读数为237,较常规优化率为76.3%;第三、四个较常规优化率依次为74.8%,73.0%。

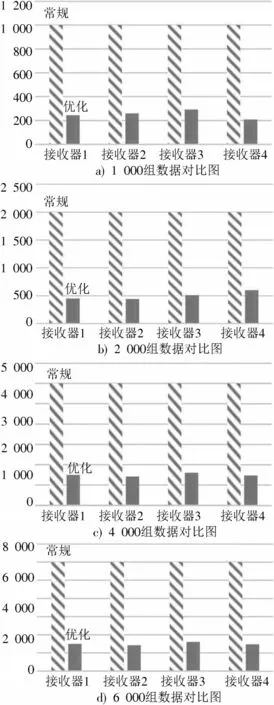

由上文可知,在传输1 000个数据且接收端为4个的情况下,本设计较常规型主从通信平均优化率为75%。为进一步证明本设计的优化性,实验又分别采取了1 000,2 000,4 000 和6 000 组数据进行传输,如图9 所示。通过实验结果分析证明,通信优化率都达到了75%。本文设计双口RAM 较传统FIFO 数据读写平均有50%的提升,由此可知在具有1 个数据发射器和4 个从属接收器的情况下,本文优化设计相比常规型主从通信效率提升了37.5%。

图9 优化与常规设计接收数据对比图

4 结 语

常规基于FPGA 的RS 485 主从通信具有体积小和成本低的特点,本优化通过对FPGA 进行硬件编码,相对于常规主从通信在数据处理方面具有显著效率提升;数据收、发两端每步都设置反馈程序,提高了数据传输的可靠性。经数据分析可得,本优化设计在从属接收器数量越多的情况下数据处理效率越高。随着主从通信设备硬件的发展,低成本、高效率和高可靠性仍是用户的首选,实验证明,本设计在主从通信方面具有较好的应用前景。