一种基于CMOS工艺的91.6~93.2 GHz压控振荡器设计

李 嵬,刘 杰,吕金杰,刘 军,苏国东,3

(1.中国电子科技集团公司信息科学研究院,北京 100086;2.杭州电子科技大学射频电路与系统教育部重点实验室,浙江 杭州 310018;3.毫米波国家重点实验室,江苏 南京 210096)

0 引 言

毫米波具有大带宽、波束窄、穿透力强等优点,极大推动了毫米波技术在通信、雷达、生物监测等领域的发展。基于W波段(75~110 GHz)研制的固态集成电路是毫米波应用技术的硬件基础,作为诸多固态集成电路模块之一的压控振荡器实现了直流信号到交流信号的转化,是毫米波通信系统本振电路、雷达系统信号产生电路中的核心器件。随着互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)工艺技术的进步,CMOS晶体管的截止频率和最大振荡频率已达到赫兹频段(300 GHz~10 THz),为毫米波压控振荡器的研制奠定了工艺基础,进一步推动硅基毫米波压控振荡器的研究及产业应用推广[1-3]。目前,硅基毫米波频段压控振荡器(Voltage Control Oscillator,VCO)在提升工作频率方面的研究主要集中在2个方面。一种是通过基波VCO的方式直接产生毫米波信号[1,4-5],另外一种是将基波VCO产生的信号通过倍频的方式间接产生毫米波信号[2-3]。此外,还可以采用开关电感或开关电容的方式来拓展VCO的调谐范围。随着电路工作频率的提高,硅基无源器件的品质因子进一步降低,导致VCO相位噪声恶化;同时,调谐范围的提升对变容管的容值变化范围提出更高的要求,进一步恶化了基波VCO的相位噪声。因此,在确保VCO电路具有适中调谐范围的前提下,提升毫米波基波VCO电路的相位噪声具有一定的难度和挑战。

本文提出一种基于变压器结构的高品质因子电感(Transformer-Based Inductor,TB_IND),有助于改善VCO电路的相位噪声,并采用金属氧化物半导体(Metal Oxide Semiconductor,MOS)开关与变容管相结合的策略,确保VCO电路调谐范围的同时进一步改善其相位噪声。基于65 nm CMOS工艺,设计了一款工作频率为91.6~93.2 GHz的VCO,可应用于W波段的通信系统、雷达系统、生物监测等系统。

1 VCO电路结构及设计方案

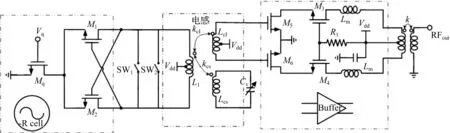

CMOS工艺的截止频率和振荡频率虽然已进入太赫兹频段,但设计一个良好性能的毫米波VCO依然存在不小的挑战。首先,在毫米波频段中,晶体管的器件模型与实际测量值之间的拟合度存在差异,设计加工后的VCO易出现频率偏移、调谐范围变窄和相位噪声恶化等问题;其次,由于CMOS场效应管的低输出功率和低栅氧击穿电压,难以实现VCO的高输出功率;再次,随着频率的提高,硅工艺的衬底损耗、金属的趋肤效应等易造成无源器件的品质因子降低,从而导致谐振电路的品质因子降低,恶化VCO电路的相位噪声;最后,随着电路工作频率的提高,CMOS场效应管的本征增益反而降低,直接导致毫米波VCO的负阻单元器件尺寸增加,抵消了谐振单元品质因子降低所产生的影响,加大了毫米波频段的基波VCO的设计难度。基于以上因素,本文设计了一款CMOS毫米波VCO电路,其原理图如图1所示。

图1 CMOS毫米波VCO电路原理图

图1中,VCO电路由负阻单元-R Cell(由M1,M2,Mq组成),TB_IND,MOS开关阵列(SW1,SW2),变容管(Cv),输出Buffer(由M3—M6组成)和输出匹配电路构成。其中,负阻单元采用经典的交叉耦合负阻单元维持VCO稳定的输出毫米波信号。TB_IND采用变压器的初级线圈作为电感(L1),与变容管Cv以及MOS开关共同构成的VCO电路的谐振单元;次级线圈I(Lcs)接可变电容,通过变容管容值的改变影响次级线圈Lcs和初级线圈L1之间的耦合,进而改变谐振频率。次级线圈II(Lcl)通过磁耦合将VCO的输出信号输入到Buffer电路;VCO通过输出Buffer电路与负载之间相连,有效降低了负载电阻对VCO电路中负阻单元的影响,确保VCO电路与外电路相连时依然能稳定输出毫米波信号。为了方便电路测试,本文设计的片上变压器实现了信号差分转单端的功能,该变压器与电感Lm构成匹配网络,使得输出Buffer和50 Ω负载阻抗达到更好的匹配。

2 VCO电路设计

从宏观上来区分,图1所示的VCO电路设计分为有源电路单元设计和无源元件设计两部分。有源电路单元包含负阻单元和输出驱动电路,无源电路元件包含电感、MOS开关、变容管、片上变压器、传输线等器件。

2.1 有源电路

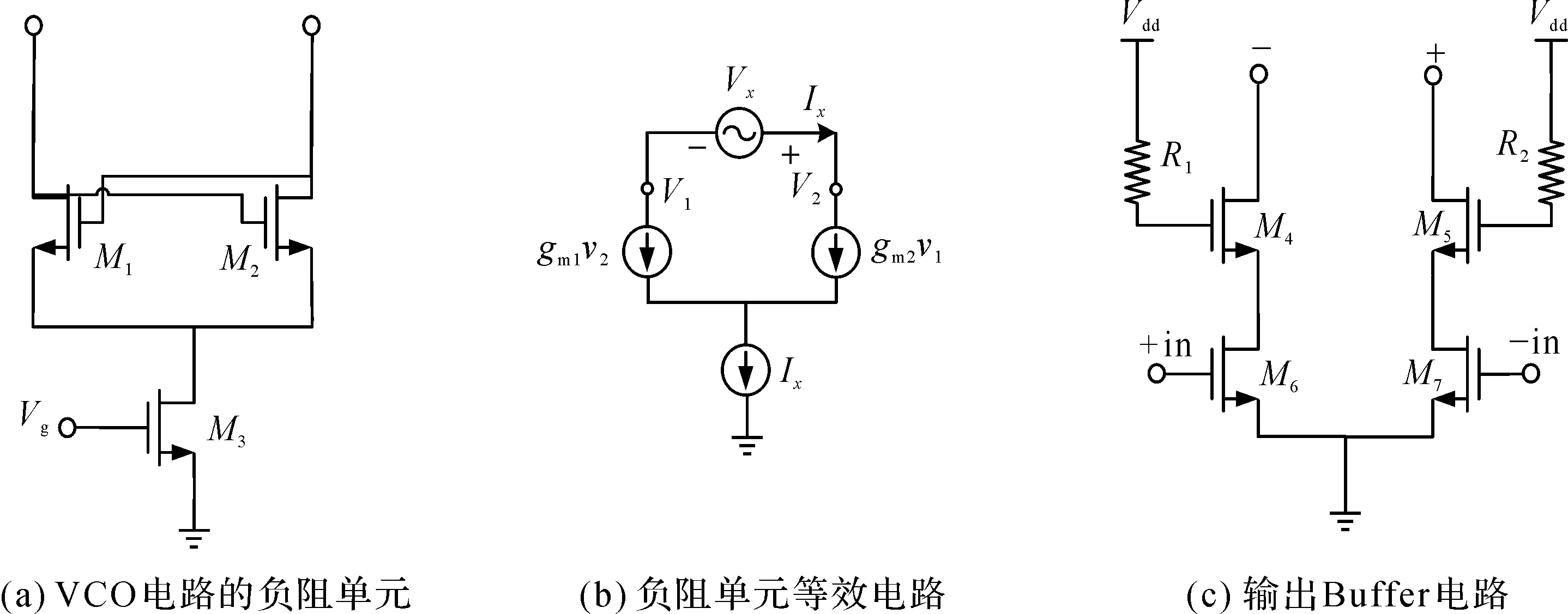

图2给出了本文设计的VCO电路的负阻单元、负阻单元的等效电路和输出Buffer电路。

图2 VCO负阻单元及其等效电路、输出Buffer电路

负阻单元采用经典的交叉耦合差分单元如图2(a)所示,主要用于补偿谐振单元及其他与负阻单元相关电路的损耗,维持VCO交流信号的稳定输出。负阻单元由交叉耦合对场效应管M1,M2及尾电流源场效应管M3共同组成,其中M3可以改善交叉耦合对场效应管所产生的输入共模信号对电路的影响。此外,将M3的栅极设计为独立供电端子,在电路测试时,通过调节M3的栅极电压来改变交叉耦合对场效应管的电流,进而改变负阻单元的阻抗。负阻单元的等效电路如图2(b)所示,当交叉耦合对场效应管的总栅宽一致时,负阻单元的阻抗为:

(1)

式中,gm为晶体管的跨导。通过对场效应管M1,M2相关参数的选择,使得交叉耦合对场效应管形成的跨导略微高于VCO谐振单元的跨导,从而保证VCO在起振后,能尽快输出稳定的交流信号。同时,晶体管选择时,需要进一步考虑晶体管本身的寄生电容,寄生电容会降低VCO的振荡频率,减小VCO的调谐范围。本文设计中,M1和M2的单指栅宽为1.0 μm,总栅宽为24.0 μm;尾电流源管M3的单指栅宽为2.0 μm,总栅宽为80.0 μm。

电路工作频率进入毫米波频段后,MOS场效应管的栅-漏寄生电容对晶体管的影响愈发重要。在VCO的输出Buffer设计中,如未将栅-漏寄生电容的影响考虑在内,极有可能因为负载阻抗反向加载到VCO的负阻单元端口,导致VCO停振或者相位噪声增加。因此,本文设计采用共源共栅放大器结构,如图2(c)所示。与共源电路相比,共源共栅电路具有更大的输出电阻,具有较高的反向隔离度,其输出阻抗为:

Ro=gm4×ro4×ro5

(2)

式中,gm4为晶体管M4的跨导,ro4和ro5分别为M4和M6的输出电阻。

经过优化仿真,图2(c)中,M4和M5的总栅宽选为6.4 μm,M6和M7的总栅宽选为12.0 μm。

2.2 无源器件

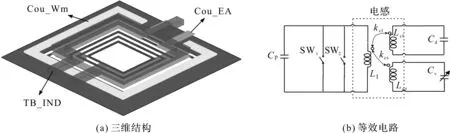

在VCO电路设计过程中,无源器件主要分为LC谐振网络和输出匹配网络。随着电路工作频段的逐渐增大,尤其进入毫米波频段后,场效应管、电感、传输线等的寄生参数(电阻、电容、电感等)在电路中的影响逐步增加,器件之间的互扰增加,影响电路的性能。因此,设计时需充分考虑寄生参数无源器件与电路中其它器件之间的相互影响。通常情况下,低频VCO电路设计时,MOS开关、变容管、负阻单元及输出Buffer电路均接在电感的端口。但在毫米波VCO设计中,这种连接方式使得器件之间的互耦增强,从而影响电路的性能。此外,目前的电磁仿真工具并不能准确估量场效应管在不同直流偏置下的相互耦合情况。因此,本文设计了一种基于片上变压器结构的高品质因子电感,在参与谐振电路的同时,通过线圈之间的磁耦合将振荡信号输送至输出Buffer,并在版图设计时,将变容管搬移至变压器的次级线圈的接口。TB_IND的3微结构图及其等效电路如图3所示。

图3 TB_IND的三微结构图及其等效电路

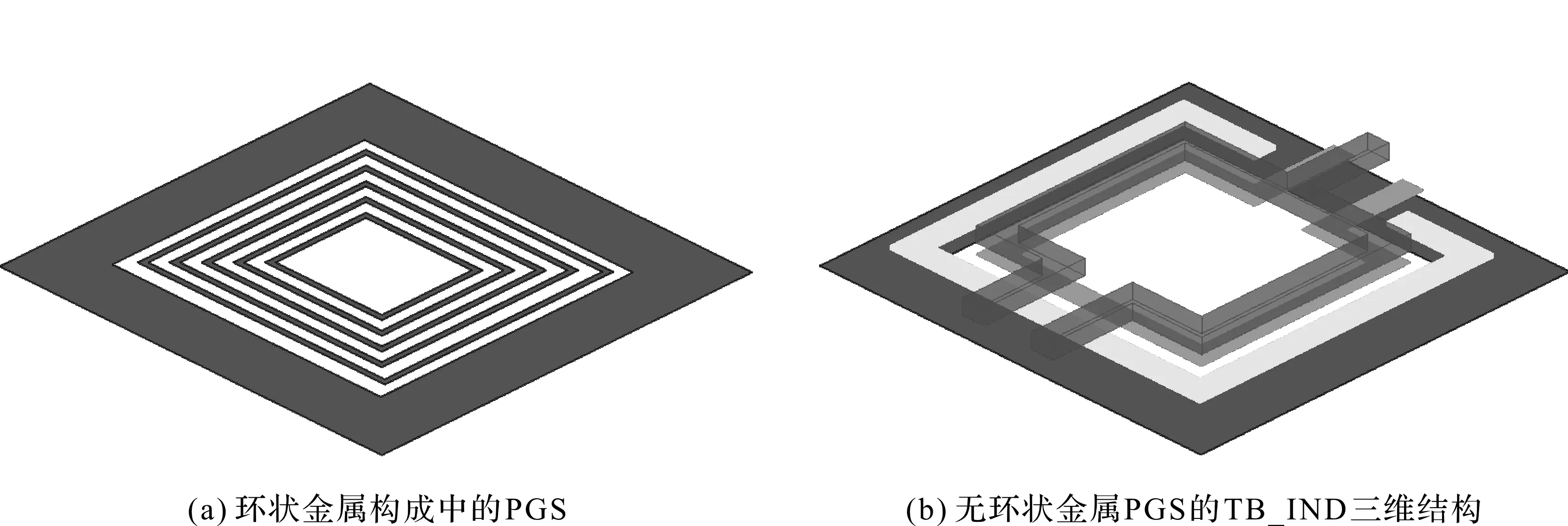

图3(a)中,Cou_Wm线圈和Cou_EA线圈为变压器的次级线圈,分别接输出Buffer和变容管,变压器的初级线圈(TB_IND)则为谐振网络中的电感。为了便于分析,图3(b)给出TB_IND的等效电路拓扑结构,其中Cp为交叉耦合单元及开关管的寄生电容,Cd为输出Buffer的寄生电容,Cv为变容管的电容,文中设计的VCO电路的输出频率由电感L1、次级线圈的互感及Cp,Cv和Cd映射到初级线圈的电容共同决定。为了提高基于变压器的电感的品质因子,电感的初级线圈采用工艺中的厚金属(金属层M8,铜,厚度为3.3 μm),用于降低金属的损耗,同时采用一种改进型屏蔽地[6]来降低衬底损耗,该屏蔽地采用底层金属M1设计的环状金属构成,TB_IND的PGS与无环状金属PGS的TB_IND三维结构如图4所示。图4(a)中,由楞次定律可知,电感上的变化电场会在金属环上感生电流,而金属环之间亦会感生电流。金属环之间的感生电流方向相反,从而形成了相互减弱的磁场,减弱了对电感的影响,改善了电感的品质因子。

图4 TB_IND的PGS和无环状金属PGS的TB_IND三维结构图

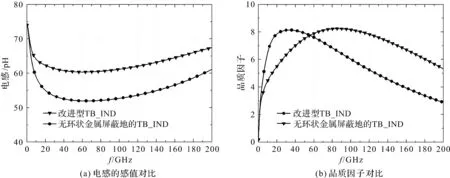

通过电磁仿真方法,评估本文提出的TB_IND和无环状金属屏蔽地的TB_IND的电感感值和品质因子,结果如图5所示。从图5(a)可以看出,电感在200 GHz范围内未出现谐振点,满足VCO电路设计时的指标要求;从图5(b)可以看出,文中提出的TB_IND在W波段的品质因子约为8.25,较无环状金属屏蔽地的TB_IND的品质因子提高了约20%,说明改进型TB_IND可有效改善VCO电路的相位噪声。

图5 TB_IND与无环状金属PGS的TB_IND随频率变化

在VCO电路设计过程中,输出匹配网络主要通过片上变压器和微带线来实现。片上变压器采用了边缘耦合结构,为了减小金属损耗,初级线圈和次级线圈均采用顶层金属(M8)设计而成。微带线的信号线亦采用工艺中的顶层厚金属(M8)设计以降低金属损耗。同时,为了减小衬底的涡旋电流对无源器件品质因子的影响,采用底层金属(M1)作为输出匹配网络中的传输线和片上变压器的屏蔽层,以提高信号在匹配网络中的传输效率。此外,片上变压器在实现阻抗匹配的同时实现了差分信号转单端的功能,方便在片测试。

3 版图与仿真实验

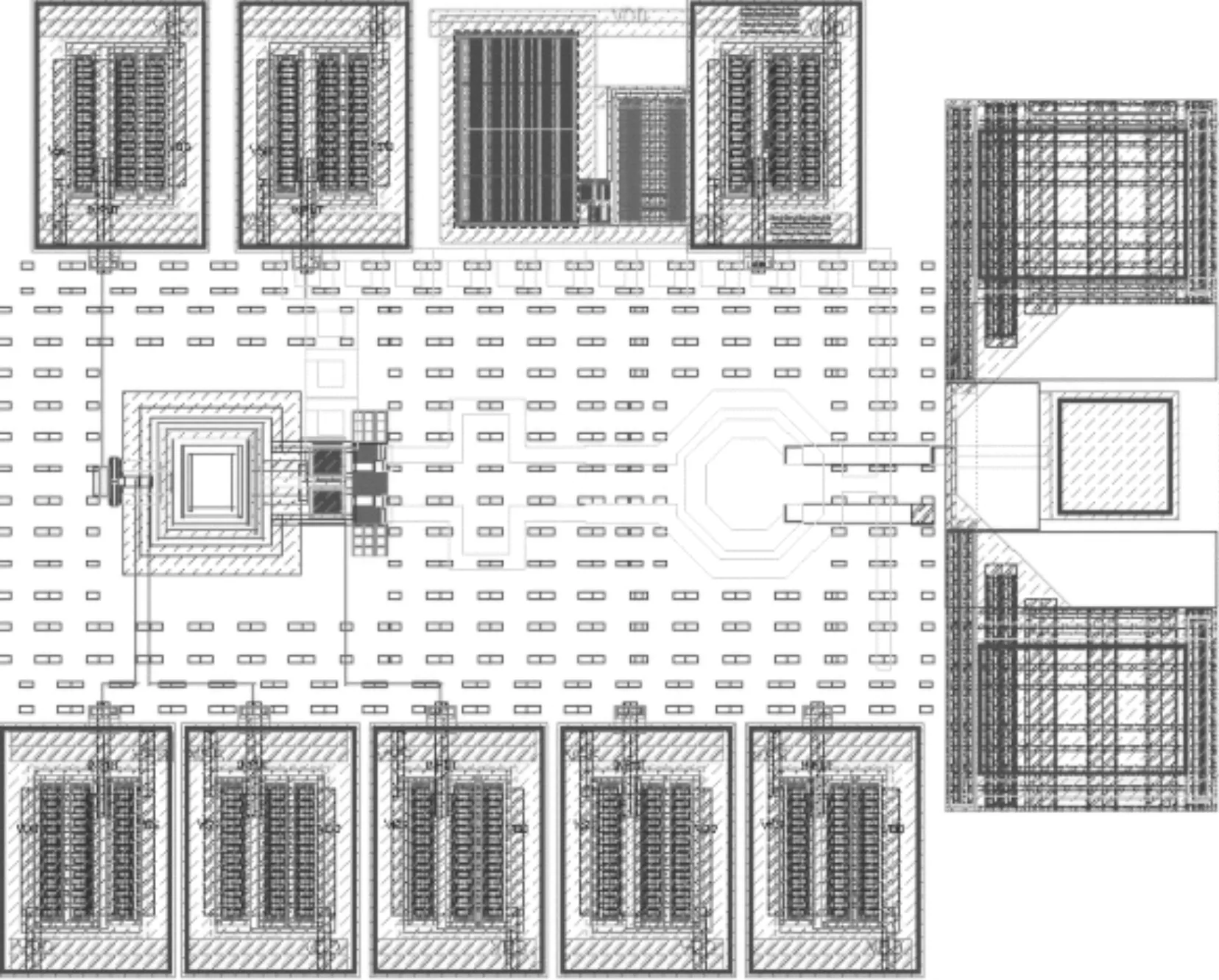

图6 VCO电路版图

基于65 nm CMOS工艺,本文设计了一款工作频率为91.6~93.2 GHz的VCO,版图如图6所示。电路版图设计中,充分考虑对称性,并根据仿真结果对版图进行优化。VCO电路中使用的GSG焊盘、电感、传输线和片上变压器等无源器件均进行了电磁仿真评估,并与有源器件结合,完成设计。为了提高无源器件的品质因子,电路中的电感、传输线均采用工艺中的顶层厚金属,变压器采用边缘耦合结构,初/次级线圈均采用顶层厚金属铜。同时,采用工艺中提供的底层金属M1作为屏蔽地,有效提高了无源器件的品质因子。信号通路及直流通路上均采用ESD保护。VCO电路芯片的大小为0.2 mm×0.2 mm。

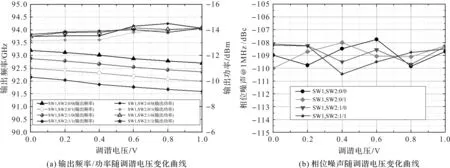

通过2组MOS开关与变容管共同实现VCO的频率调谐。2组MOS开关共有4种组态,扩展了VCO的调谐范围。本文的VCO设计中,采用小尺寸变容管来实现频率调谐,其容值变化范围小,在结合MOS开关共同调谐时需要保证每个开关态的调谐频率具有一致性,故设计的VCO调谐范围为1.6 GHz,工作频率范围为91.6~93.2 GHz,VCO的输出功率大于-14.5 dBm,在偏离谐振频率10 MHz处的相位噪声优于-107.7 dBc/Hz。图7给出了MOS开关工作在0/0,0/1,1/0和1/1状态时,VCO的输出频率、输出功率及相位噪声随调谐电压变化的情况。

图7 开关1/2工作在4种状态下的输出频率/功率、相位噪声随调谐电压变化曲线

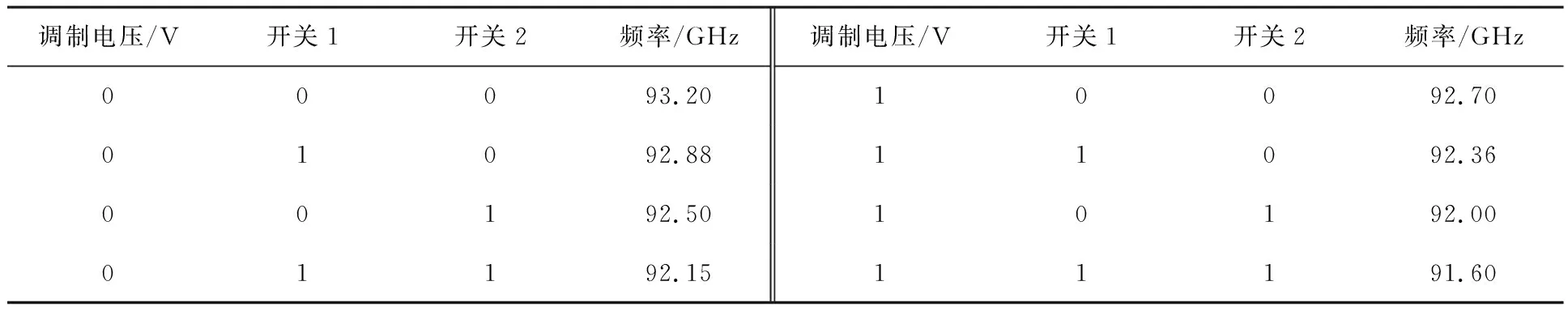

在4种状态下,VCO输出的交流信号的频率随调谐电压、开关状态变化情况如表1所示。从表1可以看出,结合变容管的容值变化,MOS开关的每种开关态可实现不小于0.45 GHz的调谐范围,同时考虑工艺加工偏差等因素,在各个开关态的频率范围有所交叠,VCO电路实现了1.6 GHz的频率调谐范围,且输出频率在开关的4种状态下均能连续调谐。

表1 VCO输出频率随调谐电压、开关状态变化表

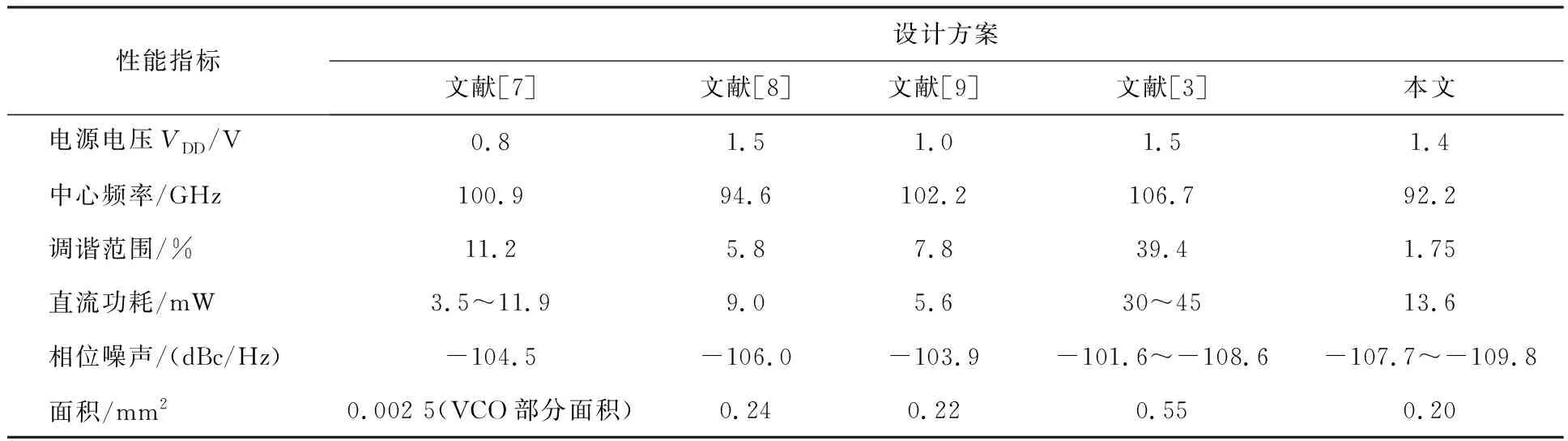

选取近年来基于65 nm CMOS工艺设计的W波段的VCO设计方案进行比较,不同设计方案的性能参数如表2所示。

表2 基于65 nm CMOS工艺的VCO设计方案性能对比

从表2可以看出,和其他设计方案相比,本文提出的VCO设计方案的相位噪声达到-107.7~-109.8 dBc/Hz,在相位噪声方面具有一定的优势。

4 结束语

基于65 nm CMOS工艺,本文提出了一种基于变压器结构的具有高品质因子的电感设计方案,在此基础上,设计了一款工作频率为91.6~93.2 GHz的VCO电路,改善了VCO电路的相位噪声,拓展了VCO电路的频率调谐范围,为应用于通信、雷达、生物检测等系统的窄带信号产生电路提供设计参考。后续计划进一步研究提高电感品质因子的方法,在确保谐振网络品质因子的同时提高VCO电路的频率调谐范围。