基于FPGA的二维双向CFAR处理器的设计与实现

高巍,谢芳,蒋荣堃,杨昊,王晓华,吕余青

(1.北京理工大学 信息与电子学院,北京 100081; 2.中国船舶集团有限公司第八研究院,江苏,南京 210000)

在雷达自动检测系统中,恒虚警率(constant false alarm rate,CFAR)处理是一种提供自适应检测门限的信号处理技术[1-4].经典的CFAR处理分为两类,即均值类(mean level,ML)CFAR和有序统计类(ordered statistics,OS)CFAR[5].单元平均(cell-averaging,CA)CFAR[6-7]是最早提出的CFAR方法,在均匀杂波背景环境下具有优异的检测性能,但在非均匀杂波背景环境下,检测概率大大降低.为了提高非均匀杂波背景和多目标背景下的检测性能,后来陆续出现了最大选择(greatest of,GO)CFAR[8]、最小选择(smallest of,SO)CFAR[9]和OS-CFAR.

CFAR处理工程化的传统方法通常是在DSP平台上实现的[10],但是由于FPGA处理速度高和并行处理结构的特点[11],使其成为实现CFAR检测器更好的选择.赵冰等[12]介绍了GO-CFAR在FPGA上实现的过程和结果,证明了利用FPGA实现CFAR检测的优势;Cumplido R等[13]在FPGA上实现了一维ML CFAR检测器,支持CA-CFAR、GO-CFAR和SO-CFAR,参考单元数为32,保护单元数为8;Perez-andrade R等[14]设计了基于FIFO的线性排序器在FPGA上实现了OS-CFAR;Sana S等[15]提出了兼顾CA-CFAR、OS-CFAR、剔除平均(trimmed-mean,TM)CFAR的硬件实现结构,参考单元为24.

以上CFAR检测器均在同一维度(即距离维或多普勒维)对目标进行检测,参考信息较为单一,且检测器参数固定或局部可配.本文提出一种基于FPGA的二维双向CFAR处理器.该处理器同时考虑距离维和多普勒维的检测结果,检测误差降低.该处理器支持包括CA-CFAR、GO-CFAR、SO-CFAR、有序统计平均(ordered statistic cell averaging,OSCA)CFAR[16]、有序统计选大(ordered statistic greatest of,OSGO)CFAR[17]、有序统计选小(ordered statistic smallest of,OSSO)CFAR[17]等6种检测算法可选.同时,它还支持参考单元数量、保护单元数量、排序值、门限因子可配置,结构灵活,适用于多种杂波背景环境.

1 算法模型

本文实现的二维双向CFAR处理器结构涉及了CA-CFAR、GO-CFAR、SO-CFAR、OSCA-CFAR、OSGO-CFAR和OSSO-CFAR等6种检测算法,如图1所示.

图1 不同的检测算法示意图Fig.1 Schematic diagram of different detection algorithms

图中D为待检单元,其两侧的阴影部分为保护单元,目的是为了防止待检单元的能量泄露到参考窗,导致检测门限有误,影响检测结果.yi、xi为前后窗参考单元的采样值,前后窗的长度均为n.前后窗杂波功率的均值估计值为YML、XML,排序估计值为YOS、XOS.利用上述6种检测算法可以得到杂波背景估计值Z.待检单元D与门限阈值通过如式(1)的判决准则判断待检单元是否存在目标.

(1)

式中:H0为待检单元不存在目标;H1为待检单元存在目标.

对处于边界的待检单元,为了防止信号突变影响CFAR有效检测,当前窗或后窗不完整时,用参考窗内剩余有效单元的均值对残缺参考窗进行补充,即

(2)

式中m为参考窗内有效单元的数量.

2 硬件结构

本文的目的是基于6种一维CFAR检测算法在FPGA上设计与实现能够对雷达距离-多普勒二维数据进行检测的二维双向CFAR处理器.该二维CFAR处理器由控制模块和检测模块组成,其结构如图2所示.

图2 二维CFAR双向处理器硬件结构Fig.2 Two-dimensional CFAR bidirectional processor hardware structure

2.1 控制模块

图中控制模块包括RAM、FIFO、参数寄存器组、筛选排序模块、读控制模块和目标缓存模块.RAM深度为16 384,FIFO深度为1 024.假设在外部存储设备DDR中缓存的一帧距离-多普勒雷达数据尺寸为D×W,参考单元数量为N,保护单元数量为P.在控制模块对DDR进行行读取(列读取)时,雷达数据存入RAM以便后续检测.当W(D)<16 384,该行(列)数据一次完全读取和检测,检测结果准确.当W(D)>16 384,该行(列)数据分批次读取和检测,每次检测结果中最后(N+P)/2个点由于RAM存储深度的原因使得检测门限由边界处理的方法得到,误差较大,因此每次读取将最后N+P个点存入FIFO,在下一次检测时先输入FIFO内的数据,再输入RAM里的数据.RAM+FIFO的设计可以保证对大尺寸雷达回波数据的有效检测且存储量较小,节省硬件资源.参数寄存器组对输入的有效参数进行锁存,在控制信号触发下对检测模块生效.可配置参数包括前窗检测器、后窗检测器、检测方法、参考单元数量、保护单元数量、排序值k和门限因子.各参数的可配置范围如表1所示.检测器和检测方法的嵌套支持6种检测算法的实现.

门限因子设计为16位定点无符号数,包括8位整数和8位小数.筛选排序模块用于处理检测结果,一方面是筛除重复的列地址,另一方面是对列地址按照从小到大的顺序重新排序.在读控制模块中,顺序列地址寻址比乱序列地址寻址速度更快.目标缓存模块主要由寄存器组成,其目的是将检测结果的相对地址转化为绝对地址.

表1 可配置参数范围

2.2 检测模块

检测模块由多路选择器、均值计算模块、排序计算模块、检测方法模块、乘法器和比较器组成.在均值计算模块中,输入数据通过流水加法和减法得到前窗累加值,在移位寄存器中延时N/2+P个周期得到后窗累加值.两者分别除以对应的有效参考单元数量,即可算出前窗均值和后窗均值.排序计算模块的设计使用了比较器和寄存器.前窗参考单元通过N/2级流水比较得到从小到大的有序值,根据排序值k选出前窗排序值,同样通过移位寄存器的延时得到后窗排序值.移位寄存器的设计使均值计算模块和排序计算模块减少了一半的运算量[18],提高了检测效率.如图2所示,det信号控制前窗、后窗检测器的选择.该信号取决于参考单元数量和前、后窗检测器的参数配置.假设参考窗内实际参考单元数量为n,当n

2.3 处理器工作流程

控制模块内部设计了有限状态机(finite state machine,FSM)[19]来控制处理器的工作流程.具体状态跳转流程如图3所示.

图3 处理器状态跳转框图Fig.3 Processor state transition diagram

未启动时,处理器处于空闲状态.启动信号触发,开始检查和配置参数,参数错误则返回空闲状态等待下一次启动信号触发,参数有效则进入数据读取状态,逐行对DDR进行读取.读取状态结束,对数据进行算法检测.当一次检测结束,状态机进入检测结果处理状态.在该状态,若检测目标数量为0,返回空闲状态.若已检测行数量小于二维数据深度,行地址信号有效,继续对行数据进行读取、算法检测和保存检测结果.若已检测行数量等于二维数据深度,即行检测结束,对检测结果进行筛选排序,列地址信号有效,读取目标列数据并进行算法检测和保存检测结果.当已检测列数量等于目标列数量,地址信号无效,处理列检测结果地址.列检测结果处理结束,进入目标输出状态.输出目标功率、目标地址和目标数量.输出完成,结束信号有效,返回空闲状态.

3 实现结果

基于实际工程应用需求以及满足数据精度和不溢出的要求,该处理器中输入数据为32位无符号定点整数,内部处理数据设计为40位无符号定点数数,其中整数32位,小数8位.

设置FPGA芯片为Xilinx Kintex7 XC7K325T,在软件Synplify Premier上对处理器进行综合,资源使用结果如表2所示,逻辑单元使用量远小于FPGA资源.综合最大时钟频率为137 MHz,速度较快.

表2 资源使用情况

表中LUT(look up table)为查找表,BRAM为存储单元,FF(flip flop)为寄存器.

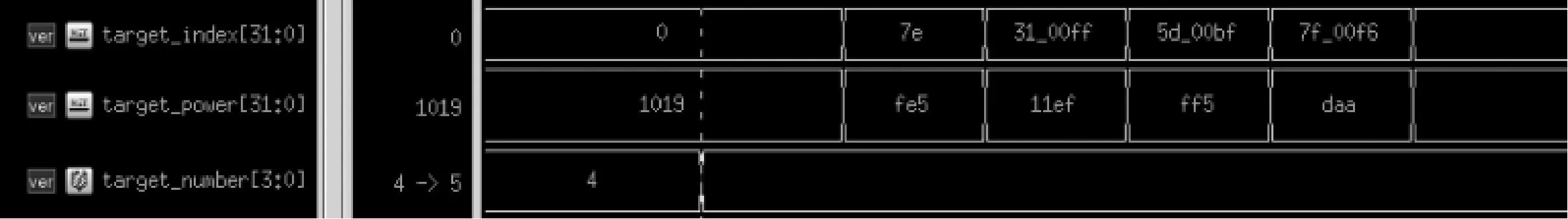

利用Matlab生成雷达回波仿真数据对该二维CFAR处理器的性能进行测试.假设回波数据服从瑞利分布,尺寸为128×256,随机设置5个目标点,信噪比为12 dB,虚警率为10-6.分别配置处理器的参数如下:参考单元数量为16,保护单元数量为1,门限因子为17.277 6,检测算法选择CA-CFAR.使用VCS进行仿真,其结果如图4所示.

图4 CA-CFAR仿真结果Fig.4 Simulation result of CA-CFAR

依此类推,针对6种检测算法分别进行100次重复实验,其中回波数据的设计考虑到了均匀和非均匀的混合环境,涵盖均匀环境、多目标环境和杂波边缘环境[20].除门限因子外,处理器参数配置与上述保持一致.门限因子的配置与选择的检测算法有关[1].排序值k取参考单元数量的3/4,即12,3/4为经验值.表3列出了不同的检测算法对应的门限因子和检测概率.表4给出了每种检测算法在上述配置下的资源使用情况.

表3 不同检测算法的检测性能

表4 不同检测算法的综合结果

由表3可知,在信噪比为12 dB的条件下,6种检测算法的检测概率均在80%以上,其中SO-CFAR的检测概率最高,为94%.相比之下,OS类的检测算法检测性能更稳定.由表4可见,OS类的检测算法比ML类的检测算法使用了更多的查找表和寄存器,这是因为OS类的检测算法在排序的过程中使用了大量的比较器和寄存器.

4 结 论

本文设计实现了一种基于FPGA硬件平台的二维双向CFAR处理器.该处理器支持6种检测算法可选、支持参考单元数量、保护单元数量、排序值、门限因子等动态可配,适合在多种杂波环境中使用.该处理器通过控制模块的设计将一维CFAR算法应用于二维检测结构中,同时考虑了距离维和多普勒维的检测信息,提高了检测精准度.在雷达仿真数据信噪比设置为12 dB的实验中,各检测算法的检测概率均在80%以上,检测性能良好.该处理器综合最大时钟频率可以达到137 MHz,逻辑资源使用量远小于总体数量,满足FPGA设计对速度和资源的要求.由实验结果可知,该处理器满足二维CFAR检测的工程应用要求.