多通道实时伪码发生器的设计与实现*

张瀚青,王彦革,李上彦,彭一文,郭银春,石云墀

(上海航天电子技术研究所,上海 201109)

0 引言

在直接序列扩频系统中,伪码具有非常重要的作用。伪码全称为伪随机噪声(Pseudo-Random Noise,PRN)码,又称为扩频码。在发射端,数据通过调制速率远高于数据速率的扩频码,达到扩宽频谱的作用,利于信号的播发,提高抗干扰性能。在接收端,利用扩频码良好的相关性能对接收信号进行解扩。解扩需要在本地生成与信号相对应的伪码,因此本地码生成器是扩频接收机必不可少的组成部分。

目前,接收机中伪码发生器多采用在只读存储器(Read Only Memory,ROM)中存储的方式。这种码发生器装置占用资源少,但是在恶劣太空环境下发生单粒子翻转[1]难以修复,可靠性不足。根据奈奎斯特定理,系统时钟至少是码速率的2 倍。一些码发生器采用分频时钟来实现码速率的降频[2-3],会对接收系统的时钟同步性造成了影响。

本文设计了一种基于现场可编程门阵列(Field-Programmable Gate Array,FPGA)的实时生成的码发生器结构,利用双端口RAM 两个独立的读写装置和伪码的周期性特点来对伪码进行同时不间断的写入和读出。写数据基于系统时钟计数,读数据利用NCO 技术输出读地址。在每个码周期结束时对码初相重新置位,减少了恶劣太空环境下码翻转对捕获系统造成的影响,实现了全局时钟下码频率的变频处理,避免了FPGA 使用分频时钟造成的不稳定性,同时通过控制读地址和NCO 累加器的初值来控制输出码的相位,实现了高精度的可控相位输出。该码发生器可广泛应用于伪码滑动相关的扩频终端同步系统。

1 工作原理

1.1 Gold 码生成原理

Gold 码是直扩序列扩频系统中常用的一种伪码,具有生成容易和相关性能好的优点[3]。Gold 码由两个相同级数的线性反馈移位寄存器所产生的相同长度的m序列经异或相加实现[4]。

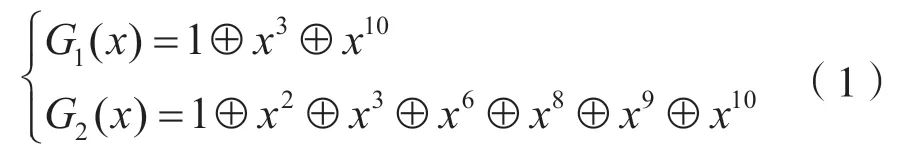

设Gold 码特征多项式为:

式中,⊕为异或符号。

Gold 码为周期性序列,其周期为2n-1,n为移位寄存器的阶数。文中采用10 位的移位寄存器,则对应码周期为1 023。

对两个寄存器设定相应的初相,两个寄存器的初相分别取:

则码生成的原理如图1 所示。

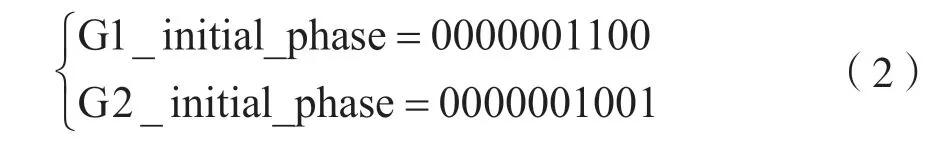

1.2 数控振荡器原理

数控振荡器(Numerical Controlled Oscillator,NCO)的作用是产生正交的正弦样本和余弦样本,通过查表法将事先根据各个正余弦波相位计算好相位的正余弦值[5]按照相位角度作为地址,存储该相位的正余弦值,从而构成一个幅度-相位转换电路。图2 为NCO 的一种电路设计,在系统时钟控制下由相位累加器对输入频率控制字不断累加,得到以该频率控制字为步进的数字相位,再通过相位相加模块进行初始相位偏移得到要输出的当前相位。利用NCO 对数据变频处理,具有频率分辨率高、变化率快以及相位可连续线性变化等优点。

图2 NCO 原理

1.3 双端口RAM 原理

双端口RAM 是在一个静态随机存储器(Static Random Access Memory,SRAM)上同时具有两套完全独立的数据线、地址线和读写控制线,并允许两个独立的系统同时对该存储器进行随机性访问,即共享式多端口存储器。双端口RAM 最大的特点是存储数据共享。

本文采用Xilinx 公司的ISE 开发工具中的双端口RAM 的IP(Intellectual Property)核。IP 核的接口如图3 所示。可以看出,一个存储器上配备两套独立的地址——数据和使能,允许两个独立的CPU或控制器同时异步访问存储单元。因为数据共享,所以必须存在访问仲裁控制。内部仲裁逻辑控制提供对同一地址单元访问的时序控制、存储单元数据块的访问权限分配以及信令交换逻辑等功能。在读写地址不冲突的情况下,可以通过两套独立的读写地址和使能对数据进行读写操作。

2 实时生成方案

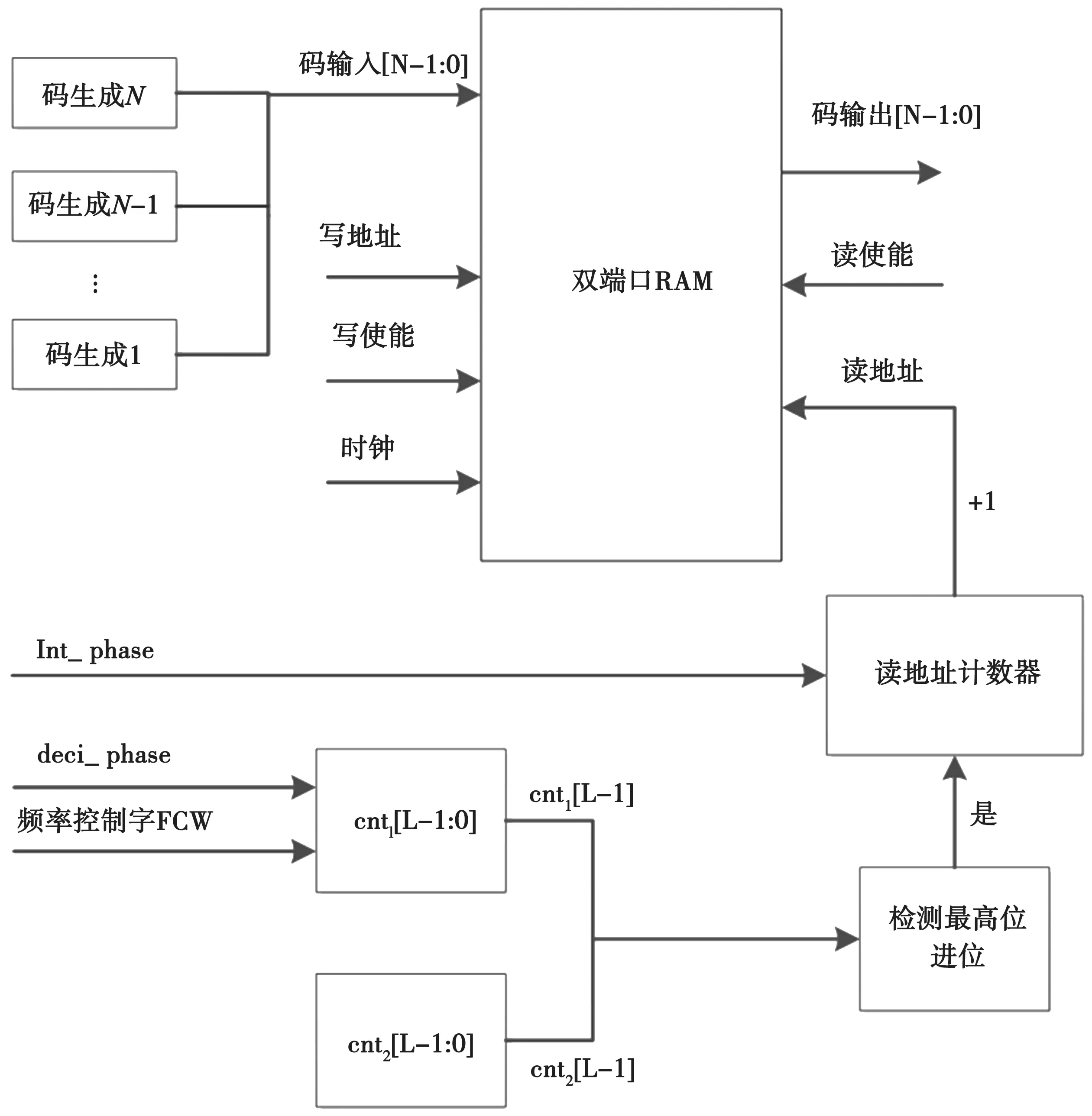

码生成器硬件生成方案如图4 所示。在开始信号脉冲给出后,写使能置为“1”,此后写使能一直处于高电平,同时给出在一个码周期长度循环累加的计数器作为写地址。每次周期结束给出一个置位脉冲,对两个移位寄存器的初相进行重新赋值。如果要对码进行截短,则可以将置位脉冲设置到需要截位的码相位上。

图3 双端口RAM 接口原理

由于双端口RAM 可以同时进行读操作和写操作,设置码NCO累加器的频率控制字来控制读地址,进而改变输出码的频率。此时,输出的码速率为:

图4 码生成器原理

式中,fclk为系统时钟,FCW为频率控制字,L为累加器位宽。

设置两个累加器cnt1和cnt2来进行累加器的进位检测。cnt1的位宽为L,每次读数开始脉冲给出后,对累加器赋相位初值。每个时钟累加值为相位控制字FCW,对累加器cnt1延时一个时钟得到cnt2。对cnt1和cnt2的最高位进行进位检测,若两个计数器发生进位,即当cnt2的最高位为“1”而cnt1的最高位变为“0”时,认定cnt1发生进位,对读地址加1。

码初相的设置分为整数位和小数位两部分,分别设定为参数int_phase 和deci_phase。整数位int_phase范围为0~1 022,小数位x范围为0~1,换算到累加器的位宽中则小数位初相deci_phase 可以表示为:

此时的输出码相位phase_out 为:

输出数据的相位分辨率reso_phase 可以表示为:

具体的工作流程:在开始给出脉冲后,对写地址赋高电平,写地址开始累加,此后码开始源源不断地进行写入;每个码周期结束时给出置位脉冲,对移位寄存器的初相重新赋值,确保伪码不因太空中的单粒子翻转发生错误;对两个移位寄存器的相位赋初值,动态刷新存储器中的码;读数开始信号需要在一个完整码周期的伪码写入存储器之后给出,以确保读写操作不发生冲突;读书开始脉冲给出后,读使能赋高电平,对读地址和累加器相位赋初值,此后变频后的伪码开始不间断输出。其中,双端口RAM 的输入位宽决定了可以同时写入的伪码通道数量;码NCO 的累加器位宽、相位控制字和系统时钟决定了输出码速率。

3 结果仿真

在Modelsim 上进行仿真,系统时钟为10 MHz,码速率为3.069 MHz,累加器位宽为32,带入式(3)可得频率控制字FCW为:

输出码初相取5.8,则可知个位数地址int_phase为5。小数位地址deci_phase 带入式(4),可得:

deci_phase=0.8×232=3 435 973 837 (8)

由式(6)可得此时的码相位分辨率reso_phase为:

仿真结果如图5 所示,可以看出写地址和读地址有着不同的位宽,输出码速率已经进行了降速处理,输出码相位也对应了5.8 的设置值。

图5 仿真结果

4 结语

本文设计了一种实时生成的码发生器结构,利用双端口RAM 和伪码的周期性特点来进行源源不断地进行刷新存储,减少了恶劣太空环境下码翻转对捕获系统造成的影响,同时利用码NCO 来实现全局时钟下码频率的变频处理,减少了在FPGA 使用分频时钟造成的不稳定性。通过设置整数位相位初值和小数位相位初值实现码相位的输出变化,具有相位分辨率高和易于相位调整的优点。此外,对码发生器进行功能仿真,得到了设计预期的结果,可广泛应用于伪码滑动相关的扩频终端同步系统。