一种基于FPGA的步进电机控制系统的设计*

邱靖超刘新妹殷俊龄杨冰

一种基于FPGA的步进电机控制系统的设计*

邱靖超1,刘新妹1,2,殷俊龄1,杨冰1

(1.中北大学信息与通信工程学院,山西 太原 030051;2.中北大学电子测试技术国防科技重点实验室,山西 太原 030051)

基于FPGA技术设计了一种对步进电机的控制系统,通过对三种加、减速算法的分析与研究,采用HDL(Hardware Description Language)硬件描述语言编写了步进电机运动控制程序,并且通过Modelsim软件仿真验证了控制系统的可行性,最终实现了系统的软硬件设计。结果表明本步进电机控制系统能满足课题需求,并可扩展到实现多路步进电机的闭环控制等方面。

FPGA;步进电机;脉冲控制;梯形加减速算法

随着数字电子技术的迅猛发展,步进电机及其脉冲控制和高精度的特点已被广泛应用于运动控制系统,且要求也越来越高[1]。基于FPGA对步进电机简单的控制包括电机的启动、运行以及停止等动作,也可进行位置和速度的控制[2]。本设计就是基于FPGA的对电机的速度、位移、方向等做精确控制的系统设计。

步进电机最常用的速度控制方法是运用单片机产生控制信号[3],实际工程应用中,由于各种电机驱动参数不同,就需要设计不同的驱动器,而传统的控制方法操作模式复杂,制作成本也较高[4]。步进电机控制采用单片机和DSP芯片作为其核心,常以定时器的方式产生控制脉冲[5],因此占用可观的系统资源[6],脉冲频率更是为微控制器所限制。本设计基于FPGA(现场可编程门阵列)实现参数可配置的步进电机驱动控制系统,采用FPGA作主控芯片,为课题中实现对两相混合式步进电机的控制,充分发挥FPGA在编程、I/O资源丰富、计算速度快(并行)等方面的优势[7]。

1 步进电机控制理论简介

1.1 步进电机及工作原理

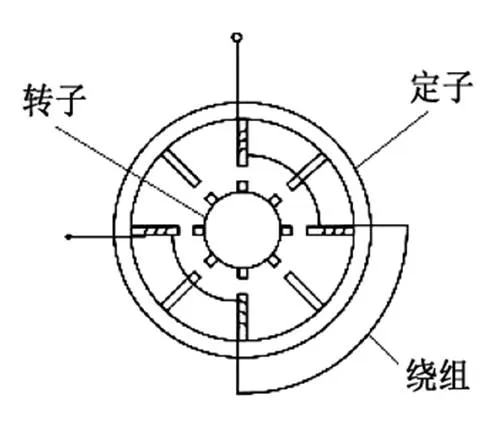

步进电机是将电脉冲信号转化为角位移或线位移的数字式开环控制元件[8],在进行加减速时,通过控制单位时间内输出的脉冲数来改变其脉冲频率[9]。脉冲信号的频率和脉冲数能决定步进电机的转速和停止的位置。工作原理是利用电子电路,将直流电变为分时供电的多相时序控制电流,用这种电流为步进电机供电,步进电机才能正常工作。步进电机按结构可以分为反应式步进电机、永磁式步进电机、混合式步进电机等,其中最广泛使用的使两相混合式步进电机,其内部结构如图1所示,主要由定子、定子绕组、转子组成。

步进电机的基本参数有空载启动频率、步距角和精度。空载启动频率即步进电机在空载情况下能够正常启动的脉冲频率,其中步距角表示控制系统每发一个步进脉冲电机所转到的角度,由以下公式确定[10]:

s=180°/r(1)

式(1)中:为定子相数;r为转子齿数。

图1 步进电机内部结构(一相绕组)

本设计使用两相混合时步进电机的转子齿数为50,该种步进电机的基本步距角为1.8°。一般步进电机的精度为步距角的3%~5%,且不累计。

1.2 加减速控制算法(曲线)及特性

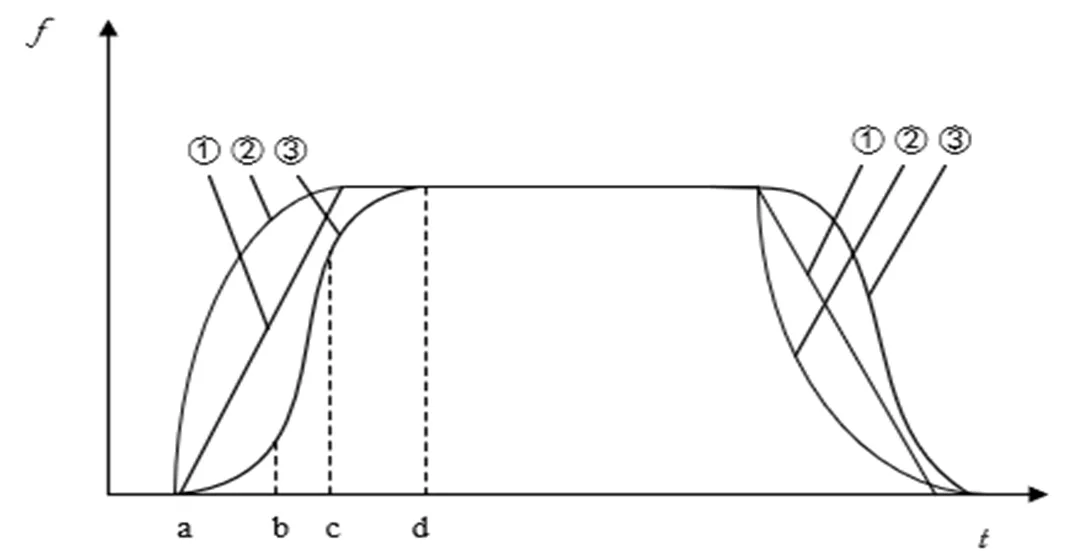

在数控系统中按控制算法分类加、减速控制曲线主要有梯形曲线、指数曲线和S形曲线等三种[15],其特性曲线如图2所示。

图2 三种加减速控制曲线图

图中曲线①所示梯形加减速控制曲线数学方程式为:

s()=0+(2)

式(2)中:s()为进给脉冲频率;0为加减速起始进给脉冲频率;为加速度。

如果设c为指令脉冲频率,则当s()≠c时,系统可根据加速度进行加速或减速控制。

梯形加减速控制特点为:在加减速起点和终点存在加速度突变,速度过渡不够平滑,但由于算法简单,仍得到广泛应用。

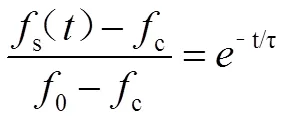

图中曲线②所示指数加减速控制曲线数学方程式为:

式(3)中:为加减速时间常数。

对于式(3),开始加速时(=0),设起始进给脉冲频率0=0;当→∞,将进入匀速运行阶段;如果减速降频开始,设输入指令脉冲频率为0,则起始进给脉冲频率等于原指令脉冲频率,即0=c。

指数型加减速控制特点为:指数型与梯形相比,平滑性好,运动精度高,但在加减速的起点仍然存在加速度突变且实现算法比较复杂,占用过多的CPU资源,对处理器平台要求过高[16]。

S曲线加减速控制曲线。

如图2所示,S曲线加减速控制特点为:以加速阶段为例,S曲线加减速控制可划分为加加速段(ab)、匀加速段(bc)和减加速段(cd)。S曲线法能保证加速度的变化是连续的,从而可避免柔性冲击。但S曲线加减速控制要实现多阶段和自动加减速控制,参数调整不易,算法实现较为复杂,因此S曲线加减速控制多用软件来实现。

2 基于FPGA的步进电机控制器的设计

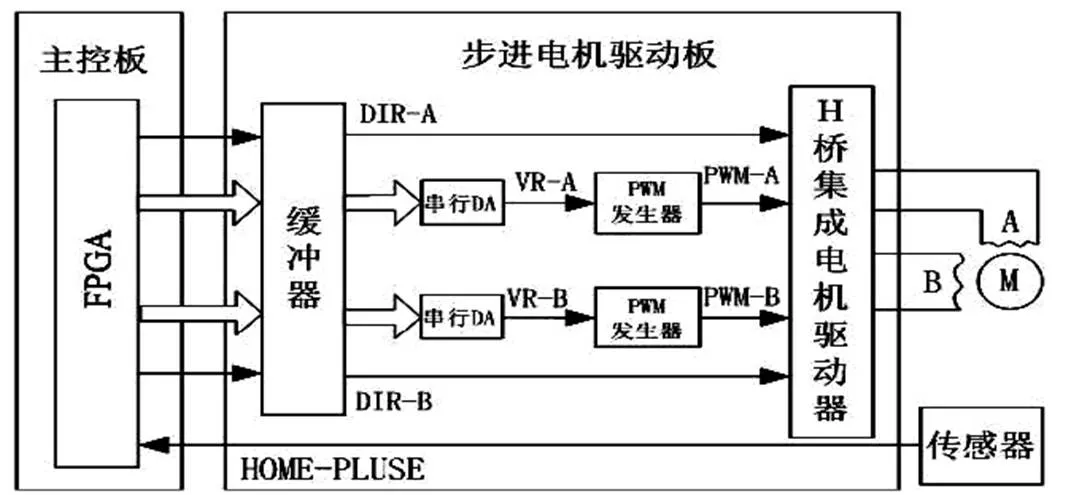

本设计的控制系统由FPGA、步进电机驱动模块和步进电机本体三部分构成。

2.1 系统硬件设计

步进电机控制系统结构硬件框图如图3所示。FPGA选用Altera公司的CycloneⅣ系列的EP4CE6E22C8N芯片为核心,利用串口通信,把上位机的命令传递给FPGA,FPGA通过电机驱动芯片A3977控制步进电机。A3977是一种新型的专门用于双极性步进电机的微步进电机驱动集成电路,它主要的设计功能包括:自动混合模式电流衰减控制,pwm电流控制,同步整流,低输出阻抗的DMOS电源输出,HOME输出,休眠模式以及易实现的步进和方向接口等。FPGA与A3977之间通过数字IO进行步进电机驱动控制,A3977对电机的驱动由其内部的双DMOS管组成H桥实现,将12 V加载到电机上实现驱动控制。

2.1.1 通信模块

FPGA与上位机之间通过串口(UART)转USB进行通信,芯片采用PL2303将标准的UART协议转换为USB协议,在计算机安装驱动后,便是一个虚拟串口实现UART的传输。UART的数据传输不需要时钟,只要两条信号线分别进行数据收发。UART最终通过USB接口与计算机连接,建立起虚拟串口通信。

图3 硬件设计框图

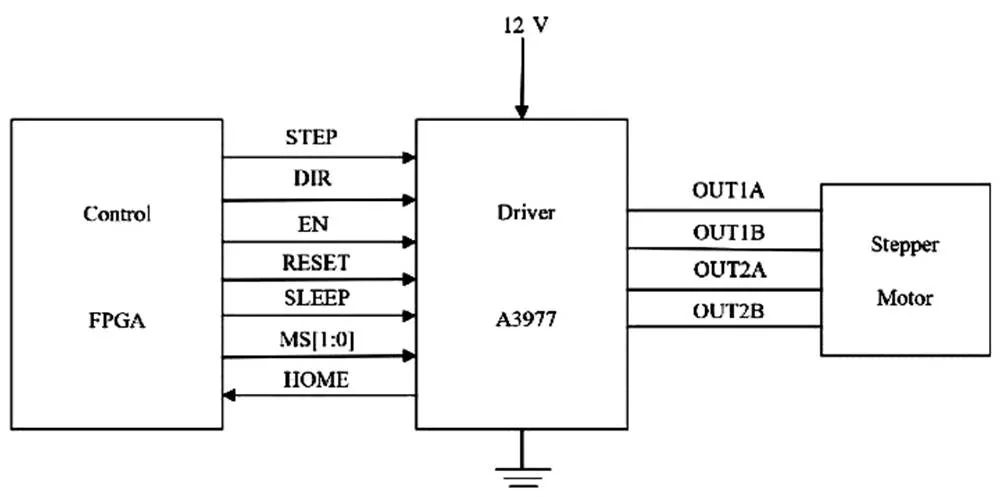

2.1.2 驱动模块

驱动器用于将FPGA发送的电脉冲信号转换为角位移。本设计使用42BYGH34-04A型号电机,FPGA与A3977的数字IO接口的连接如图4所示。

图4 FPGA与A3977的数字IO接口图

其中,STEP是驱动步进电机的脉冲信号。该信号的上升沿发起一个步进动作,即步进电机“迈”一步。而步进电机“迈”一步的步幅则由MS[1∶0]决定。DIR是步进电机方向控制信号;EN是步进电机工作使能信号,该信号拉低,STEP、DIR和MS[1∶0]信号的控制才有效。RESET是驱动芯片A3977复位信号,低电平有效。正常工作时,该信号需要拉高。MS[1∶0]是步进分辨率选择,即“步幅”的设定。HOME是回响脉冲。对应不同的步进分辨率,HOME脉冲的周期数不同。例如,MS[1∶0]=2´b11时,每32个STEP产生一个响应HOME脉冲。

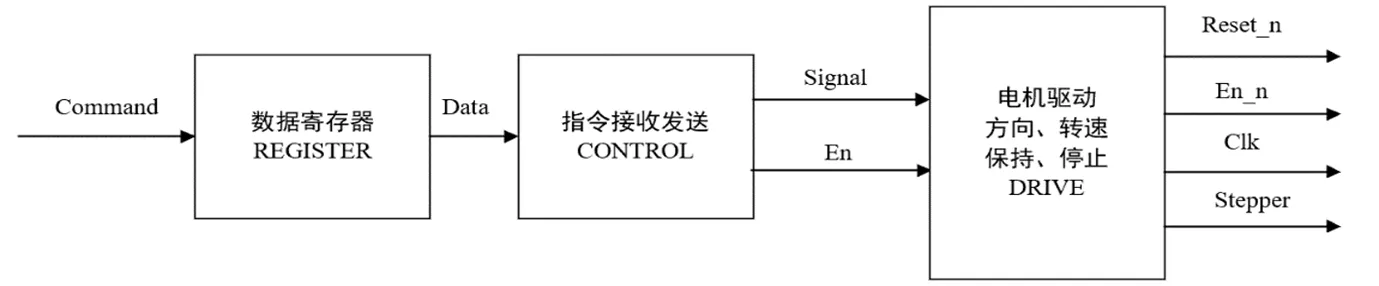

2.2 系统软件设计

本设计采用QuartusⅡ平台,运用Verilog语言自顶向下进行FPGA程序设计;主要分为数据寄存器、指令控制器和电机启动三个模块(模块划分及接口如图5所示),人机交互界面采用labview软件设计。从上位机发出的方向,步数等指令先传给数据寄存器,当外部驱动指令发出后,由指令接收发送模块将数据传递给电机驱动模块。模块DRIVE接收到信号后,控制步进电机的启停、方向和转速等。

2.2.1 步进电机控制模块

步进电机控制模块需要实现的功能主要有正反向、加减速、步数、启动和停止。虽然设定STEP处于不同的频率,从而控制步进电机的转速,但步进电机从停止到目标频率通常有一个加速过程,从目标频率到停止也有一个减速过程。步进电机有一个启动频率的概念,可以直接驱动步进电机从停止到低于启动频率的某个频率,不需要任何加速。因此,控制步进电机从启动频率(一般比启动频率低一点)加速到目标频率,减速也是从目标频率减到启动频率,然后步进电机停止运行。

图5 软件模块和接口设计

首先判断步进电机驱动的目标频率stepper_delay_tar-get与当前频率stepper_delay_current的值是否一致,若一致,则不作任何加速、减速操作,保持当前速度运行;若目标频率高于当前频率,则执行加速;若目标频率低于当前频率,则执行减速。

在加速或减速控制开启状态下,分频计数逻辑每10 ms产生一个高脉冲,用于切换当前的速度。这个10 ms的定时值可以根据实际电机驱动情况调整,对于匀速加速而言,步进电机从启动频率到目标频率需要经过个中间频率(的值越大,步进电机运转得越稳定,越不容易堵转或失步)。而定时10 ms,就是要保证步进电机在每个中间频率都停留10 ms。在电机稳定的加速或减速运转与耗费的时间之间寻求一个平衡。每10 ms,步进电机的速度都会加速或减速固定的频率值,本设计中设定为“100”,例如,从500 Hz 加速到5 000 Hz,依次经过的频率点为500 Hz、600 Hz、700 Hz……4 900 Hz、5 000 Hz。当加速或减速到目标频率时,加速和减速控制结束。

2.2.2 通信模块

本模块功能是接收从PC机向FPGA控制模块发送的步进电机控制信号,由3个功能模块组成,分别是波特率模块speed_setting.v,实现串口波特率的控制;接收模块my_uart_rx.v,该模块通过解析uart_rx信号获得串口数据字节;发送模块my_uart_tx.v,该模块将从上位机接收到的数据发送出去。

3 实验仿真与验证

本文采用勇敢的芯SF-CY4开发板进行仿真与实验验证,FPGA型号为EP4CE6E22C8N,系统时钟为50 MHz,周期为20 ns,驱动板芯片为allegro公司的A3977,供电电压为12 V。软件平台为QuartusⅡ13.1,使用Quartus自带的仿真软件Model-sim对FPGA的输出波形进行功能仿真,由以下几步完成。

3.1 编写testbench仿真测试.v文件

为了验证以上逻辑设计是否成功,在下载到开发板观察现象之前通过编写激励文件,并将其保存到工程对应的testbench文件夹下。

3.2 运行仿真

设置好仿真脚本后,选择Tools→Run Simulation Tool→RTL Simulation进行功能仿真,如图6所示。

图6 开启功能仿真

3.3 仿真结果与分析

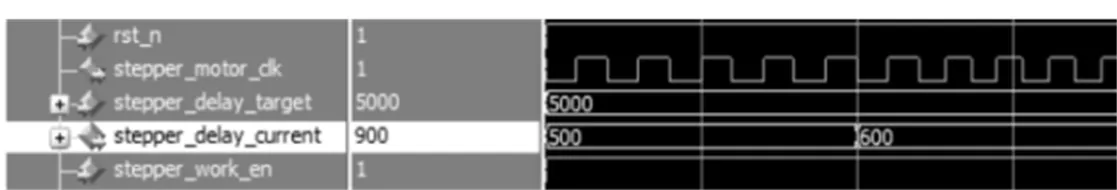

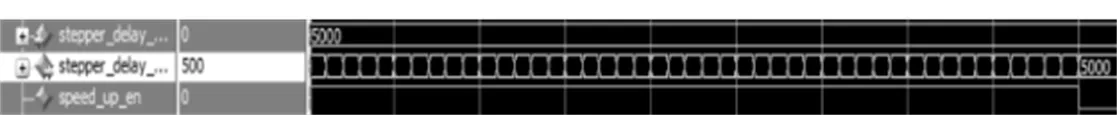

设定步进电机的起步频率为500 Hz,目标频率为5 000 Hz,仿真运行,在ModelSim图中rst_n为复位信号;stepper_work_en信号是步进电机的使能信号;stepper_delay_ current和stepper_delay_target分别为步进电机驱动脉冲的当前频率和目标频率;stepper_motor_clk信号是步进电机的前进脉冲。当复位信号rst_n为高电平且stepper_work_en信号也为高电平时,步进电机进入运行状态,图中rst_n和tepper_work_en信号都为1,stepper_motor_clk信号的一个上升沿就引起电机一个步距角的转动。前仿真波形如图7所示。

图7 前仿真波形

程序中设置的脉冲数为1 215,分频系数为45,在Model-sim中仿真的结果如图8所示。

图8 加速过程分频

因时间间隔相等,都为100 Hz(10 ms),从500 Hz加速到5 000 Hz,一共有45个速度等级,因此分频数是45;频率为500 Hz时脉冲数为5(500/100 Hz),脉冲为600 Hz时脉冲数为6(600/100 Hz),以此类推,当频率增加到4 900 Hz时,脉冲数为49,总的脉冲数为5+6+7+…+49=1 215。

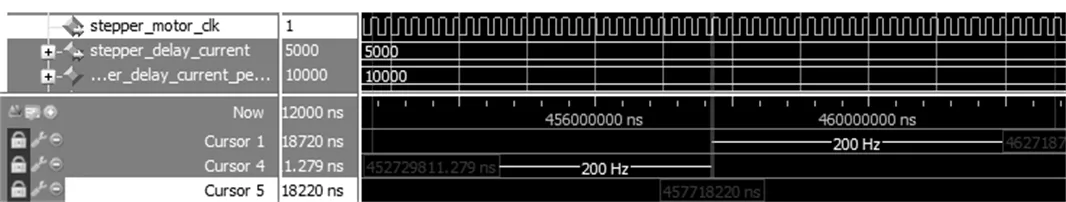

加速阶段中,脉冲频率每隔100 Hz增大一次,每个频率的保持时间为10 ms,因为每个单位时间内增加的脉冲频率也为100 Hz,所以脉冲数加1,即对应图中左边部分脉冲数为6,右边部分脉冲数为7。加速脉冲波形如图9所示。

匀速阶段中,当脉冲频率增加到了5 000 Hz时,脉冲宽度一定,频率不变,单位时间内的脉冲个数不再发生变化,每100 Hz的时间里脉冲个数为50。

图9 加速脉冲波形

匀速脉冲波形如图10所示。

图10 匀速脉冲波形

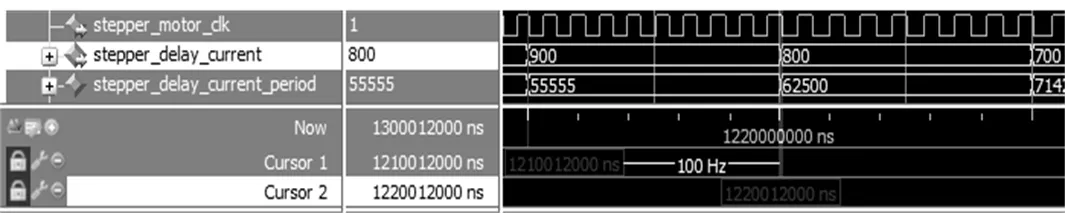

减速阶段中,脉冲频率每隔100 Hz降低一次,每个频率的保持时间为10 ms,因为每个单位时间内减小的脉冲频率也为100 Hz,故脉冲数减1,即对应图中左边部分脉冲数为9,右边部分脉冲数为8。减速脉冲波形如图11所示。

图11 减速脉冲波形

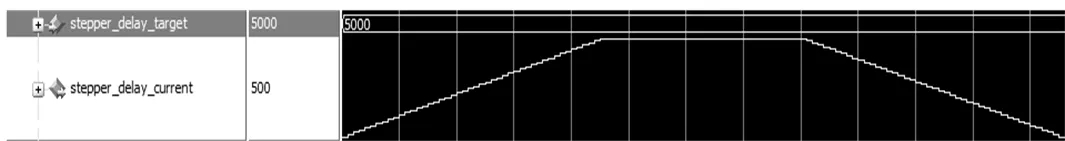

为了更为直观地观察输出波形的变化,通过把输出数据格式改为模拟的自动模式,即可看到FPGA输出的脉冲波形为梯形,如图12所示。

图12 梯形加减速仿真波形

4 结论

在加速阶段步进电机驱动当前的脉冲信号stepper_ delay_current频率逐渐增大,在匀速阶段维持不变,减速阶段逐渐减小。其中,每隔一定的时间,脉冲频率增大一次,每次增加100 Hz。一个脉冲步进电机产生固定的位移,在加、减速阶段由于频率的变化,步进电机的转速也会变化,单位时间内的位移会发生变化,并且可看出整体设计符合预期。通过以上对仿真波形的分析,脉冲频率的大小按照匀加速—匀速—匀减速这一规律变化,整个输出波形为一个等腰梯形,即步进电机的转速也按照这一形式变化,仿真结果与本设计相符,基于FPGA实现了步进电机的梯形加减速控制。

5 结语

本文针对步进电机控制系统的要求,采用FPGA设计了各个功能模块,并采用Verilog语言编程,进行了功能仿真和时序仿真。结果表明,各个功能模块逻辑清晰、合理,系统稳定性良好,各项指标符合设定要求。利用FPGA并行控制的特点,在本设计上的基础上可以实现多路步进电机的闭环控制,具有可移植性高、适用性广的特性。

[1]杨永清,吴学杰.基于ARM和FPGA的多通道步进电机控制系统[J].装备制造技术,2017(3):177-180.

[2]刘东征,吴学杰.基于FPGA的步进电机控制芯片设计[J].工业控制计算机,2011(4):71-72.

[3]张雷.基于FPGA步进电机开环驱动设计[D].哈尔滨:黑龙江大学,2013.

[4]潘涛,程耕国.步进电机控制器的FPGA实现[J].现代电子技术,2009(1):148-150.

[5]方旭,吴学杰,黄鸿国.多通道步进电机控制系统的设计[J].仪器仪表与分析检测,2014(3):1-4.

[6]杨永清.基于STM32和FPGA的多通道步进电机控制系统设计[D].成都:西南交通大学,2014.

[7]AVEY J.An FPGA-based Hardware Accelerator for Iris Segmentation[D].Ames:Iowa State University,2018.

[8]YU J,KANG H M,WANG Y S,et al.A control system of t-hree-axis stepper motor based on the FPGA[C]//International Conference on Mechatronic Sciences,Electric E-ngineering and Computer.Shengyang:IEEE,2013:3334-3337.

[9]ATES H E.Design and realization of a step motor driver with micro-stepping capability[D].Ankara:Middle East Technical University,2011.

[10]李信锋.两相混合式步进电机矢量控制和位置伺服算法研究[D].深圳:深圳大学,2015.

[11]丛爽,李泽湘.实用运动控制技术[M].北京:电子工业出版社,2006.

[12]李金洪.步进电机FPGA变速控制系统设计[J].电子制作,2015(18):15-16.

TN79

A

10.15913/j.cnki.kjycx.2021.08.004

2095-6835(2021)08-0011-04

山西省科技厅重点研发项目(编号:201903D121058)资助

邱靖超(1992—),男,工学硕士生,主要研究方向为电子测试技术、FPGA与嵌入式系统开发等。

〔编辑:张思楠〕