基于GaAs HBT的低相噪压控振荡器设计

陈志巍,何勇畅,毛小庆,高海军

(杭州电子科技大学射频电路与系统教育部重点实验室,浙江 杭州 310018)

0 引 言

当今无线通信技术发展迅猛,高集成度、高可靠性、低成本的收发机备受关注。压控振荡器(Voltage Controlled Oscillator,VCO)是收发机中的关键模块,其性能显得非常重要。蔡运城等[1]基于1 μm GaAs HBT工艺,VCO电路设计采用了考毕兹(Colpitts)结构,最终该电路实现可调频率在3.370~4.147 GHz范围内,对应的相位噪声和最大功率输出分别为-125.2 dBc/Hz@1MHz和-16.13 dBm。武岳等[2]基于1 μm GaAs HBT工艺,VCO电路设计采用了改进的π形结构,最终该电路实现可调频率在23.123~23.851 GHz范围内,中心频率为23.5 GHz,对应的相位噪声和最大功率输出分别为-103.12 dBc/Hz@1MHz和-1.68 dBm。相位噪声是压控振荡器的重要性能指标之一,直接干扰收发机接收和发射信号,影响有用信号输出的波形[3-4]。GaAs HBT工艺中,片上电感工作在较高频率时,由于其品质因数较低[5],限制了VCO相位噪声性能的提高。基于上述原因,本文在厦门三安2 μm GaAs HBT工艺的基础上,设计了一种1.6 GHz的宽频带高输出功率低相噪VCO,该电路在较宽的调谐范围内实现较低的相位噪声;通过添加输出缓冲器Buffer,该设计在低相位噪声的前提下实现了较高的输出功率。

1 差分Colpitts电路设计

1.1 低相位噪声VCO

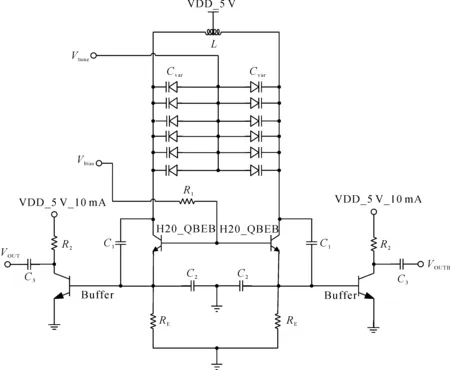

本文设计的差分Colpitts结构VCO如图1所示,其中H20_QBEB为工艺库中的三极管晶。为了保证晶体管偏置在线性工作区,本设计通过电阻R1限流,最终偏置电压Vbias为晶体管提供了微小的偏置电流,并且电阻R1还具有保护电路的作用。对于不同的偏置电压Vbias,选择合适的电阻R1来调节晶体管的静态工作点从而得到合适的相位噪声十分重要。本设计的发射极电阻RE应该选择大电阻的原因是大阻值的RE可以抑制其对相位噪声性能的恶化;但当RE的值过大时,压控振荡器的输出摆幅也降低,故本设计需要同时对电路的相位噪声和输出电压摆幅进行合理的权衡。与工艺库中自带的电感Layout元件相比,本文设计的差分螺旋电感L的品质因数更高,可以提高VCO的相位噪声性能,并减小了整体芯片面积。输出缓冲器Buffer被添加在输出两端来实现较高的输出功率;在所有元器件选定之后,通过调节控制电压Vtune实现频率调谐效果。

图1 差分Colpitts结构压控振荡器

谐振回路由差分螺旋电感L、变容二极管阵列电容Cvar及固定电容C1和C2构成。其中增加固定电容可以调节VCO输出的中心频率和增加谐振回路中的等效电容品质因数。简化后,谐振电路由电感L和等效可变电容C构成。振荡器谐振频率fosc为[6]:

(1)

式中,C的大小由固定电容和变容二极管阵列电容决定,L的大小则由本文设计的差分螺旋电感决定。

首先对固定电容进行设计,本设计定义固定电容的分配比为N=C1/(C1+C2)。为了达到减小VCO相位噪声的目的,本设计通过增大N值来实现,并且电路的脉冲敏感函数和导通角都会减小;但是增大N值也会恶化电路的两端电压摆幅,即摆幅减小。由于N值过大会减小输出电压摆幅和增大相位噪声,所以本设计需要通过迭代仿真优化N的值[7-8]。本文通过仿真得到N的最佳取值为0.311。然后对变容二极管阵列电容进行设计,在VCO设计中添加二极管,并使其反偏工作,通过改变反偏电压来实现变容效果。变容二极管的阵列并联提高了阵列电容Cvar。图1中,C1与C2串联,再与Cvar并联,总电容为:

(2)

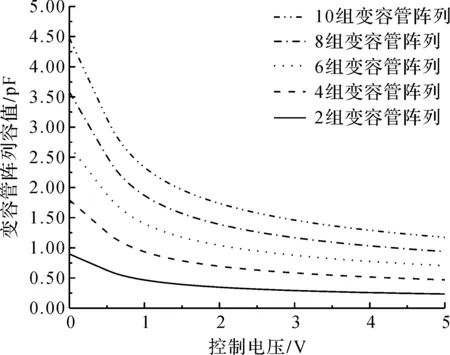

根据式(1)和式(2)可知,Cvar的取值范围越多,VCO调谐范围越宽,但不存在最优Cvar值。本设计通过权衡处理,并且电路必须在较宽的调谐范围内实现低相位噪声性能,最终使压控振荡器的频率调谐范围、输出摆幅和相位噪声同时得到最佳值。本文将相对可调谐范围指标设置在15%以上,当阵列数量过小时,在中心频率一定的情况下可调谐范围达不到所需指标。变容二极管阵列容值与反偏电压的关系为:反向偏压越大,变容二极管阵列电容越小。通过改变控制电压和变容二极管阵列的数量来调节变容二极管阵列电容的变化范围从而调谐VCO振荡频率范围。本文通过实验仿真得到GaAs HBT工艺下并联变容二极管阵列的电容值变化范围随变容管阵列数量和控制电压变化的曲线如图2所示。

图2 Cvar随控制电压变化的曲线

从图2可以看出,变容管阵列越多,电容值变化范围越大,等效中心电容也越大,过多的电容组数会影响谐振网络的中心频率和相位噪声。因此综合考虑,优化结果为变容管阵列是由6组Cvar并联构成,单个二极管的宽为30 μm,长为20 μm,叉指数为2。

1.2 差分螺旋电感

在振荡器电路中,电感的品质因数直接决定了整个谐振网络的品质因数[9]。电感的面积会增加芯片的整体面积,还可能影响到VCO的相位噪声性能。根据Leeson公式[10],VCO的相位噪声表示为:

(3)

式中,k是Boltzmann常数,F为常数,T为绝对温度,Δω为频率偏移值,Psig是谐振电路的功率损耗,QL为谐振电路有负载时的品质因数,ω0和ω1/f3分别是1/f2和1/f3相位噪声区域的拐角频率。

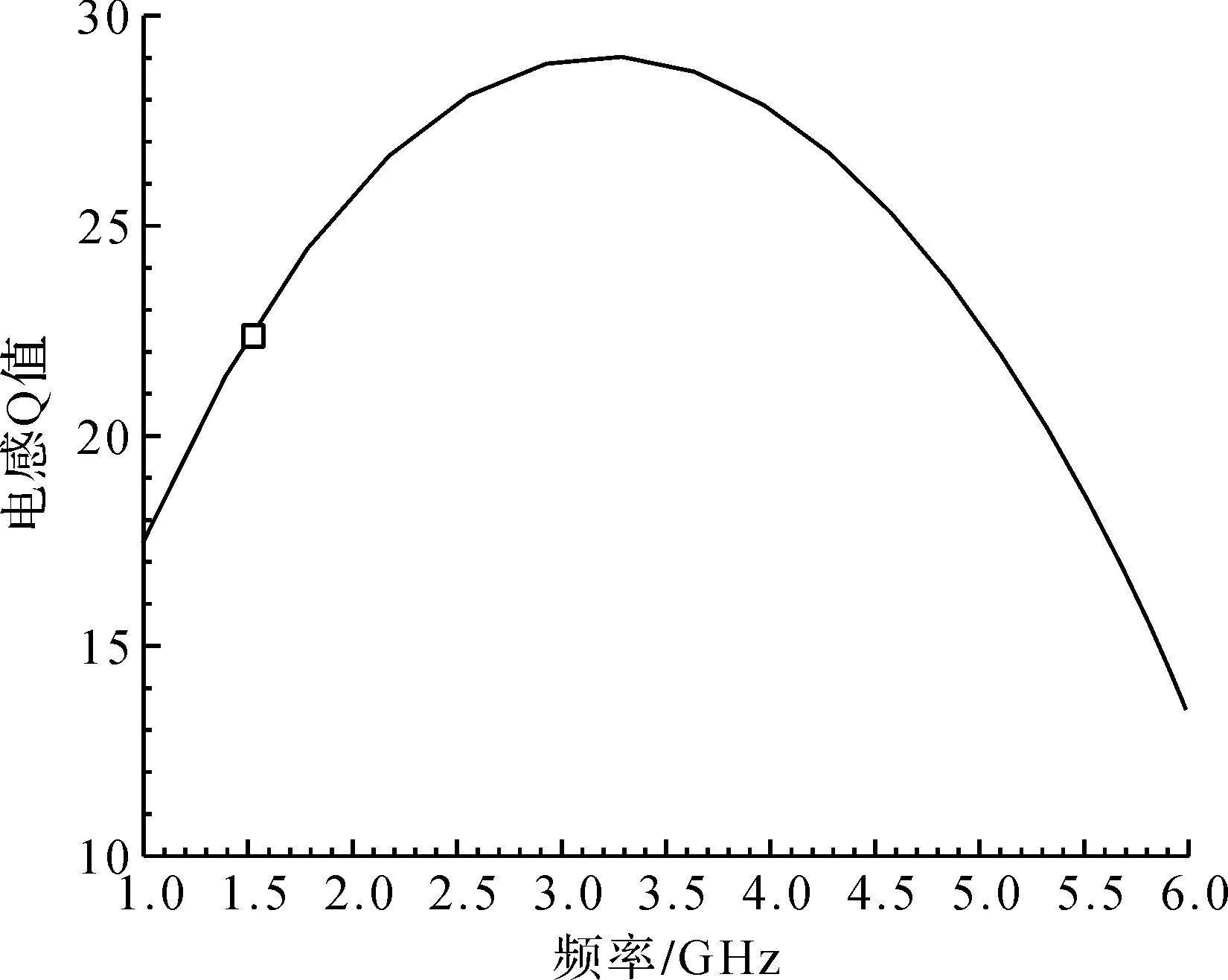

从式(3)可以看出,相位噪声与电感品质因数QL值成反比,故提高电感的品质因数有利于降低VCO的相位噪声[11]。一般情况下,电感的品质因数值随着频率的升高而增大,而电容的品质因数却随着频率的升高而减小;但是在毫米波频段以下,电容的品质因数仍然比电感高很多。因此,在设计平面螺旋电感时应尽量使其Q值最大化,保持其寄生电阻最小化,从而使得整个振荡电路的相位噪声性能达到最优[12]。

本文设计了带中心抽头的差分对称螺旋电感,可以进一步提高品质因数Q值。文献[13]总结了螺旋电感的感值计算公式为:

(4)

式中,μ为绝对磁导率(在自由空间中),n为电感圈数,davg为电感直径的平均值,ρ为填充系数,在圆形电感中,c1,c2,c3,c4均为常数。在s≤3w(s为电感线圈间距,w为电感线圈宽度)时,感值误差小于8%,且具有较高的准确性。

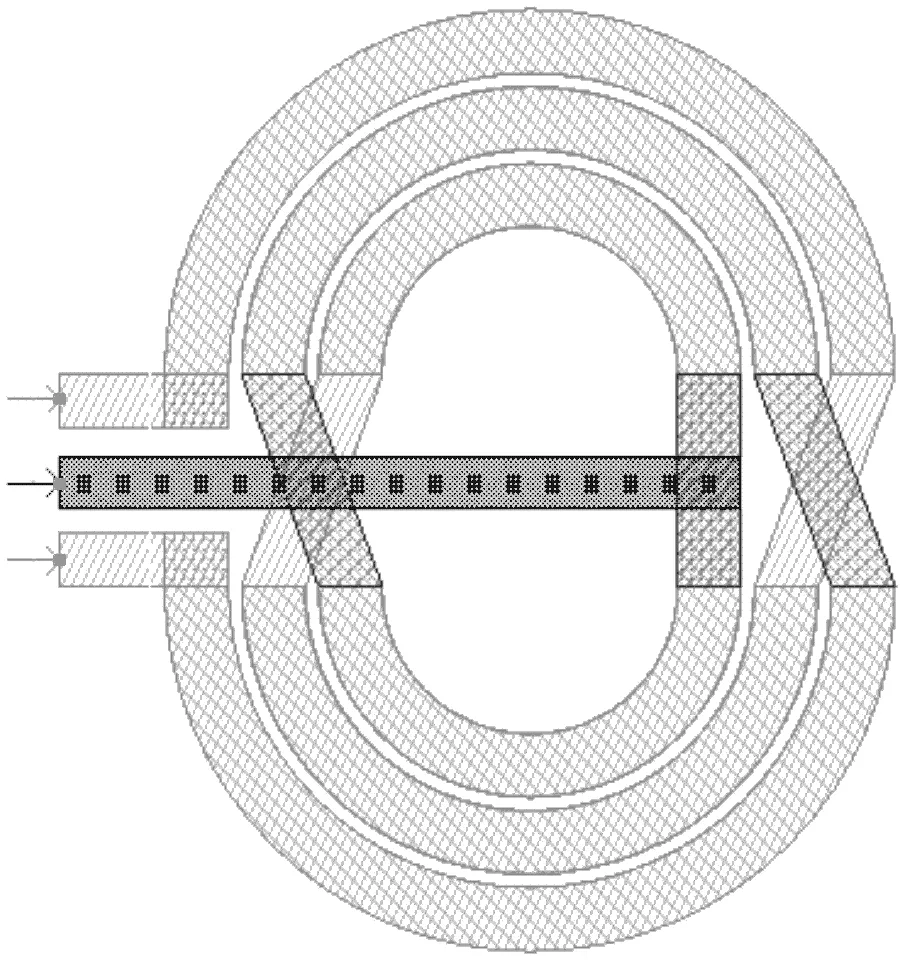

本文在GaAs HBT工艺中设计了高Q值电感,如图3所示,电感线圈的线宽为50 μm,线间距为10 μm,线圈内径为115 μm,圈数为3;所设计电感是在高级设计系统(Advanced Deisgn System,ADS)软件中进行电磁(Electro Magnetic,EM)仿真的。一般情况下,理想电感Q值应在峰值之前,电感的Q值仿真曲线如图4所示。从图4可以看出,在3.0~3.5 GHz频率范围之间电感品质因数达到峰值,且在1.6 GHz处的Q值在22以上。

图3 差分螺旋电感

图4 螺旋电感的Q值

1.3 共射级Buffer

图1中,输出两端分别加了1个输出Buffer,Buffer电路均为共射极结构,具有较高的输入阻抗和适中的输出阻抗。在输出端,适中的输出阻抗能在负载改变时减小输出电压的变化量,而对比共集电极放大电路(射极跟随器),共射极放大电路拥有更高的功率放大能力。为了最大限度地保留VCO的低相位噪声性能,同时获得较大的输出功率增益,本文通过仿真得到图1所示电路在1.6 GHz处的相位噪声及各次谐波功率值,如图5所示,输出信号功率为13.78 dBm,相位噪声约为-132.55 dBc/Hz@1MHz。

图5 1.6 GHz处带Buffer的各次谐波功率曲线和相位噪声曲线

2 测试结果及分析

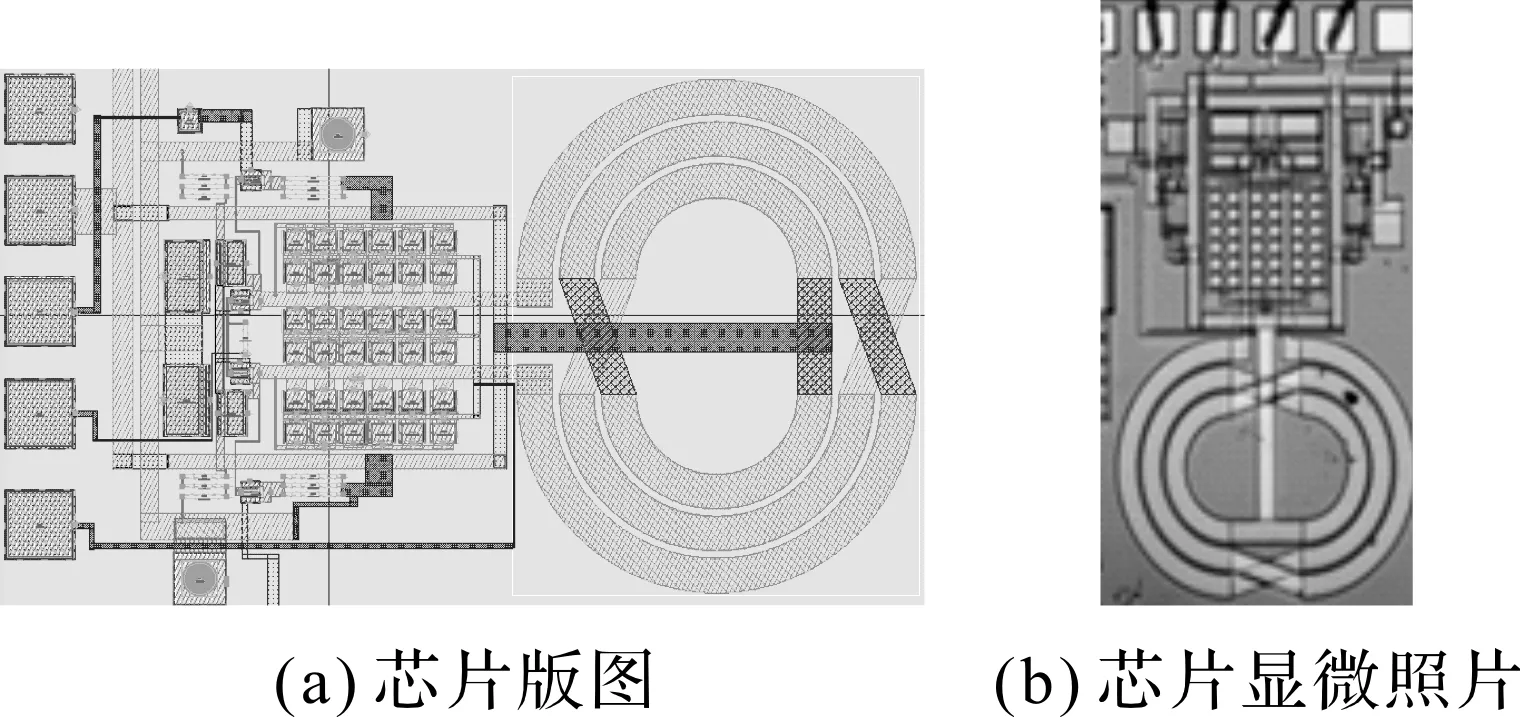

本文基于2 μm GaAs HBT工艺,使用ADS仿真工具,对设计的低相噪VCO进行设计与仿真,最后完成流片测试。锁相环芯片中VCO的部分的芯片版图和显微照片如图6所示,VCO芯片面积大小为1 300 μm ×760 μm,芯片位于PCB板的中央位置,通过键合线连接到对应的焊盘。给VCO加单独的电源电压和控制电压进行测试。

图6 VCO芯片版图和显微照片

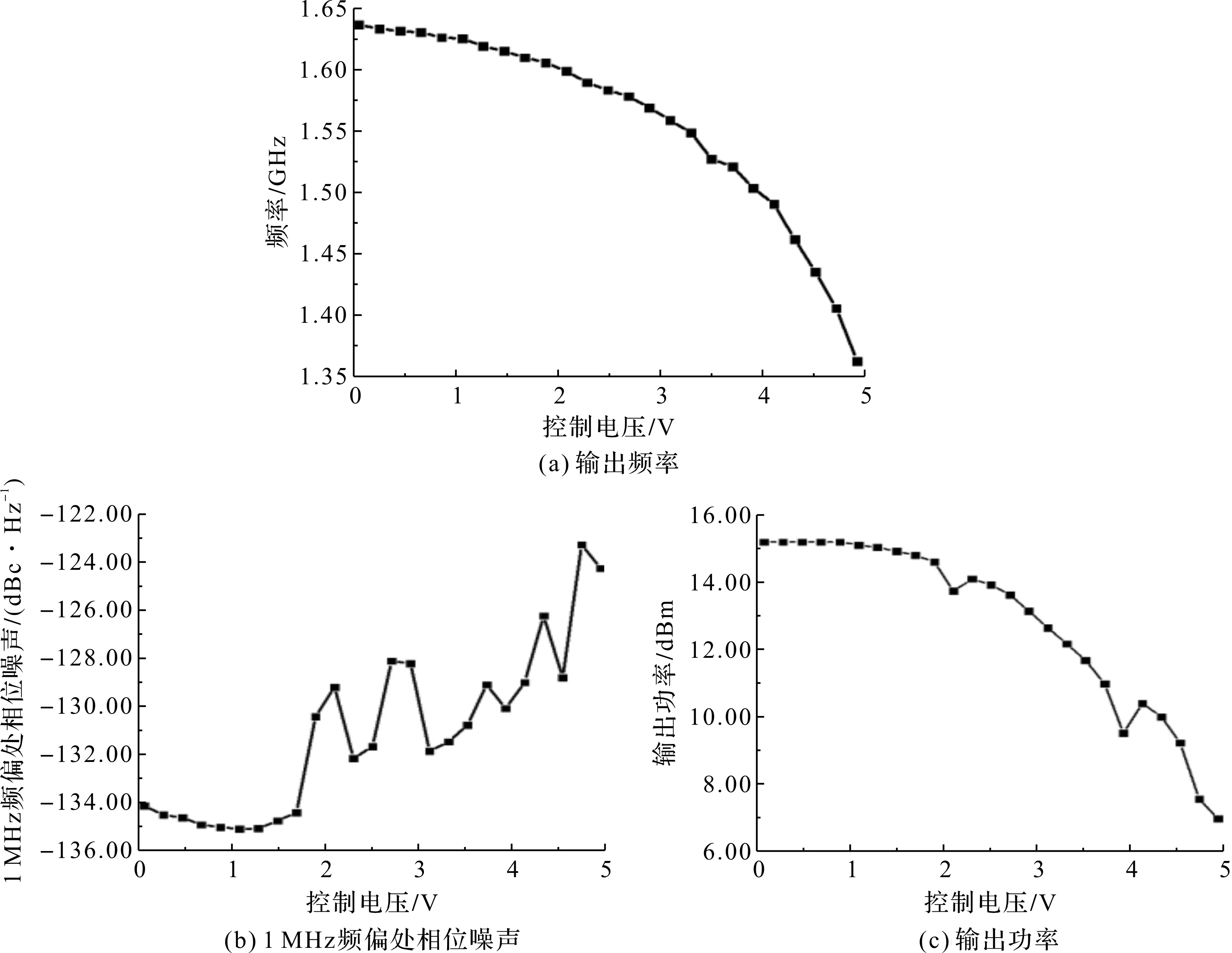

在供电电压为5 V的情况下,得到不同控制电压下压控振荡器的性能如图7所示。图7中,压控振荡器的输出频率范围为1.36~1.62 GHz,相对调谐范围为17.4%,输出频率范围内的相位噪声为-135.10~-123.50 dBc/Hz@1MHz,输出信号功率范围为7~15 dBm。通过以上结果分析表明,在较宽的调谐范围内,本设计同时实现了良好的相位噪声和较高的输出功率性能。

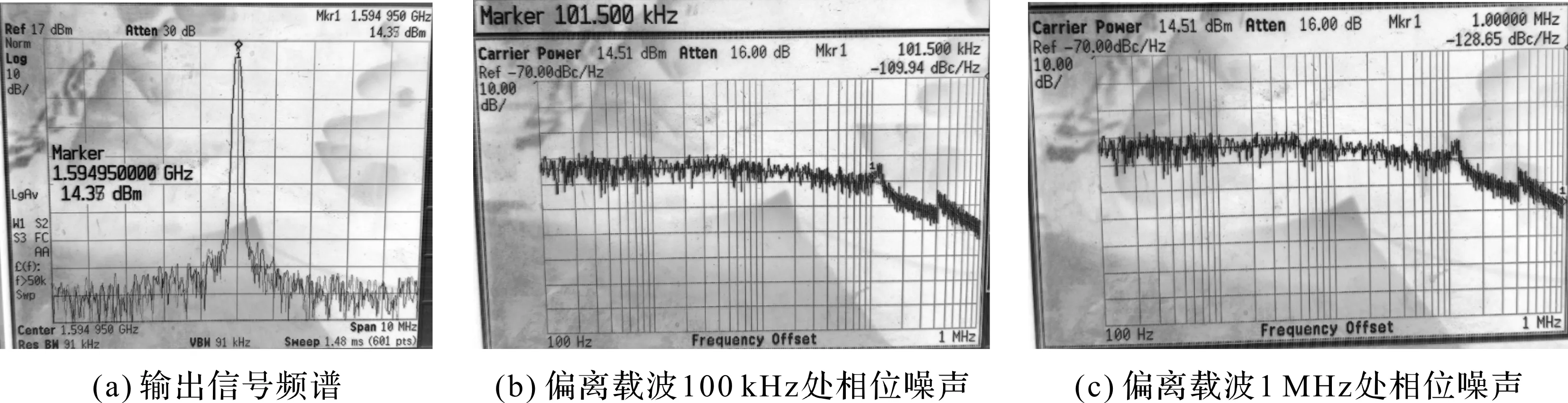

VCO输出频率为1.6 GHz时,输出信号频谱及相应的相位噪声曲线和输出功率曲线如图8所示。从图8可以看出,1.6 GHz处的信号功率为14.37 dBm,相位噪声为-109.94 dBc/Hz@100kHz和-128.65 dBc/Hz@1MHz。

图7 不同控制电压下振荡器的测试性能

图8 1.6 GHz处压控振荡器的测试性能

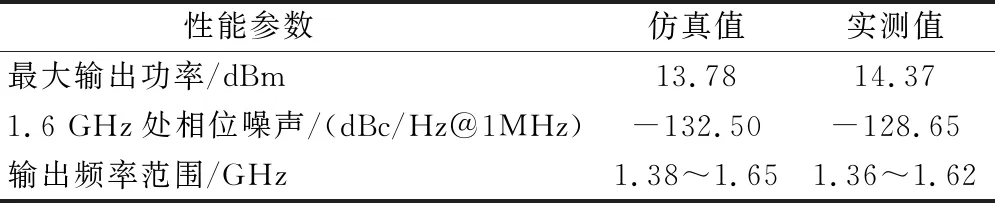

表1 仿真与测试的性能对比

1.6 GHz处仿真与测试性能的对比如表1所示。从表1可以看出,与仿真相比,实测值的最大输出功率仍然保持较大值;由于键合工艺、器件参数误差以及测量误差等原因,实测结果的相位噪声和输出频率范围偏差较大。

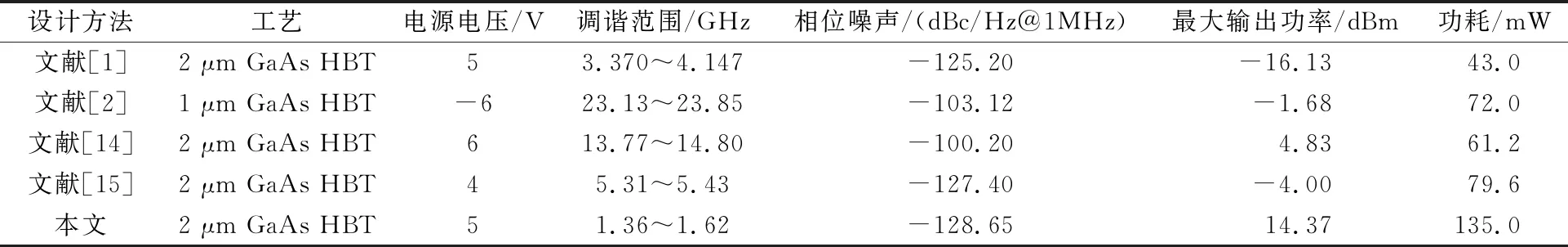

本文设计的VCO与部分文献的VCO的性能参数对比如表2所示。从表2可以看出,与文献[1]、文献[15]相比,实现了较宽的调谐范围;本设计具有较大输出功率的优势,同时也产生了较大的功耗。

表2 不同VCO的性能参数对比结果

3 结束语

本文基于厦门三安 2 μm GaAs HBT工艺,设计了一种宽频带低相噪压控振荡器,其相位噪声较低,调谐范围较宽,输出功率较高。基于本设计的测试与仿真结果,本文将继续优化电感Q值和电路整体功耗,特别是针对功耗性能较差的问题,需要对输出端Buffer的优化设置和它对相位噪声性能的影响进行权衡。