一种宽频率范围电荷泵锁相环快速锁定方法

王德龙,刘 彤

(无锡中微亿芯有限公司,江苏无锡 214072)

1 引言

随着集成电路技术的快速发展,FPGA 的系统集成度和工作频率也越来越高。锁相环(PLL)作为FPGA 芯片时钟管理模块的核心,具有宽范围频率合成、时钟抖动滤波、时钟网络去歪斜、相位调节、占空比调整等功能,且可以通过灵活配置来满足不同的时钟需求。电荷泵锁相环是一种常见的数模混合型锁相环,具有捕获范围大、锁定时相位差小、低功耗等优点,在理论上可以实现零静态相位误差,有着其他锁相环不可替代的优势[1]。本文所研究的上电快速锁定方法是基于电荷泵锁相环设计的。

上电锁定时间是指锁相环从上电启动到输出稳定频率所用的时间,是锁相环的一项重要参数指标。传统电荷泵锁相环仅通过电荷泵的充放电电流来调整压控振荡器控制电压,通常上电锁定时间会比较长,后续有文献提出一些方法来减小电荷泵锁相环的上电锁定时间,例如动态调整电荷泵充放电电流[2]、添加预充电电路[3]等,但这些方法对宽频率范围锁相环减小各频率下上电锁定时间的效果不太明显。本文通过对应用于FPGA 的宽频率范围锁相环的研究分析,提出一种在不影响锁相环正常功能的前提下,通过添加简单的辅助电路来大大减小锁相环上电锁定时间的方法。

2 电荷泵锁相环介绍

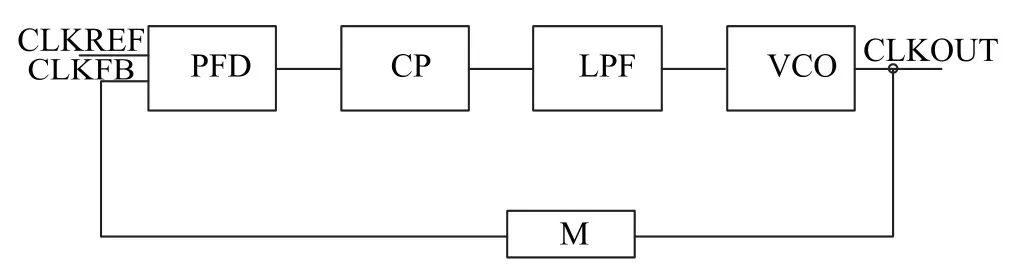

电荷泵锁相环一般由鉴频鉴相器(PFD)、电荷泵(CP)、环路滤波器(LPF)、压控振荡器(VCO)和反馈分频(M)等组成,通过连接反馈分频的输出与PFD 的输入构成一个反馈系统,利用反馈原理实现频率及相位的同步控制,如图1 所示。在PLL 上电后,首先由PFD获得输入参考时钟(CLKREF)与反馈时钟(CLKFB)之间的相位差,然后CP 将这个相位差转换为电流信号,再通过LPF 生成VCO 控制电压VCTRL,并滤除其中的高频分量,仅把直流分量输送到VCO,来改变VCO 的振荡频率。当反馈时钟和输入参考时钟之间的相位差恒定时,认为两者同步,也就是环路锁定。

图1 电荷泵锁相环结构

传统电荷泵锁相环一般仅通过CP 的充放电电流来调整VCTRL,而且基于环路稳定性考虑,这个充放电电流一般不会太大,所以在PLL 上电后要把VCTRL提升到合适位置需要很长的时间。有文献提出一种通过对VCTRL预充电的方式来减小上电锁定时间,这种方法会在上电后在一定时间内将VCTRL提升至一个初始位置,从而达到减小上电锁定时间的目的,然而这种方法会固定VCTRL的初始电压且无法精确控制,对于宽频率范围PLL 来说,还是需要通过电荷泵充放电电流花费较长的时间来调整VCTRL以达到锁定。本文将以一种VCO 频率范围为800~1600 MHz 的PLL 为例,在不影响PLL 正常功能的基础上增加一块频率比较电路来控制VCTRL的预充电初始位置,从而根据VCO 频率来调整VCTRL的初始位置。本例基于28 nm 工艺,通过spectre 仿真验证可以大大减小PLL 的上电锁定时间。

3 电路实现

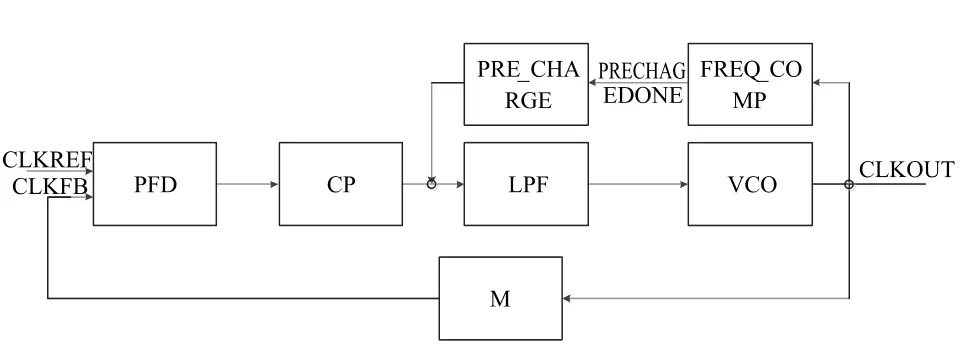

本文设计的上电快速锁定的方法为在传统电荷泵锁相环的基础上增加了2 个辅助电路,预充电(PRE_CHARGE)和频率比较(FREQ_COMP),如图2 所示。

图2 快速上电锁定的电荷泵锁相环结构

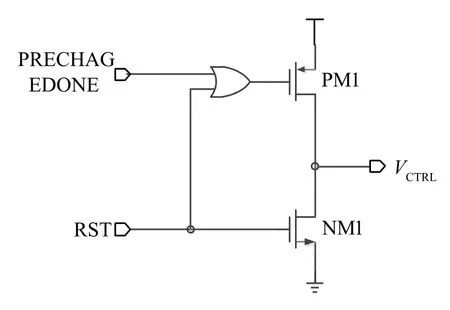

3.1 预充电电路

预充电电路可以提供较大的上拉电流将VCTRL电压拉升至合适的位置,如图3 所示。在PLL 上电后先对VCTRL电压清零,然后再进行预充电操作,可以避免因VCTRL上残留的电荷引起PLL 状态的错误。

图3 预充电电路示意图

3.2 频率比较电路

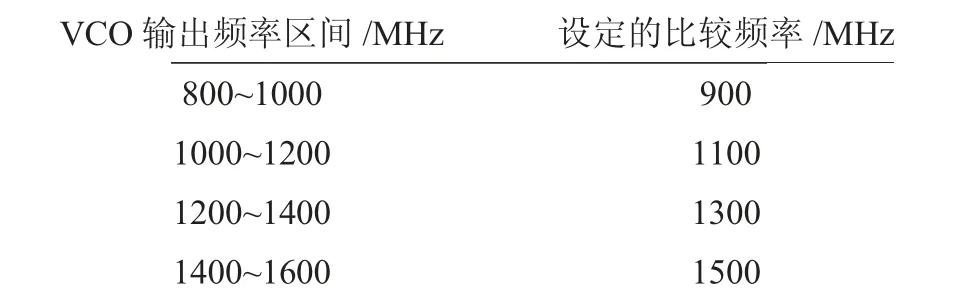

本文的PLL 中VCO 频率范围为800~1600 MHz,所需要的VCTRL范围也会比较大。为了让PLL 在VCO频率范围内都能做到快速上电锁定,本文设计了一种频率比较电路。该电路可比较VCO 输出时钟频率和设定频率的大小,当VCO 输出时钟频率大于设定频率时输出高电平控制预充电电路结束预充电。因此可以通过配置不同的设定频率来将VCO 的宽频率范围分成若干个窄频率范围区间,这样就可以均衡各种频率下的PLL 上电锁定时间,做到宽频率范围下均可快速上电锁定。

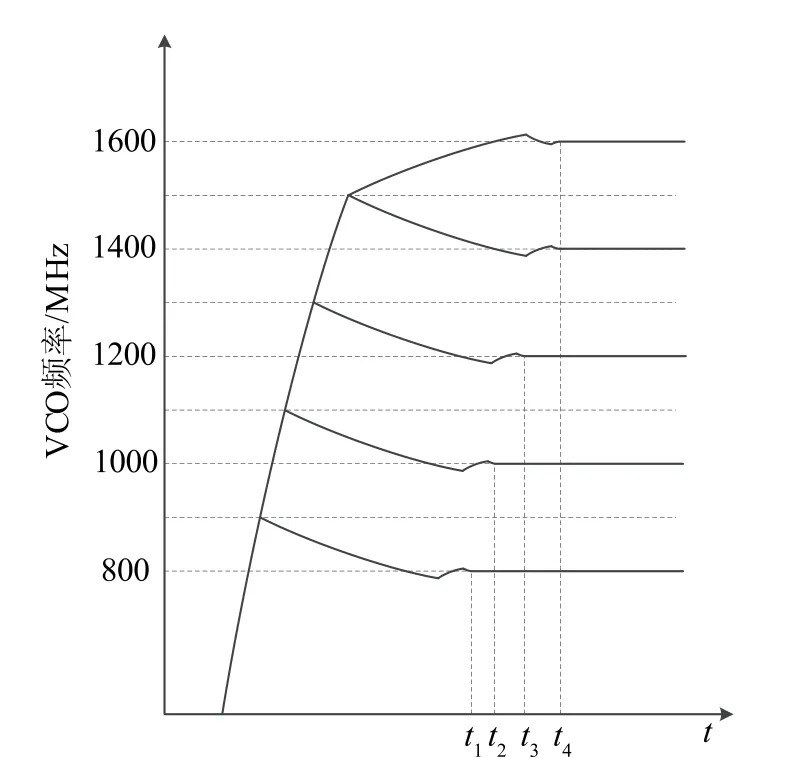

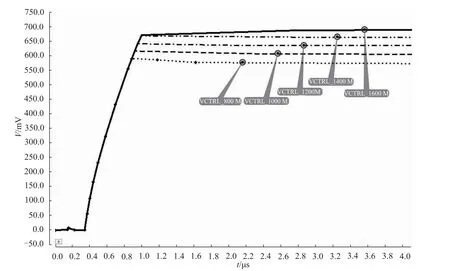

设定频率可根据VCO 输出频率范围权衡决定,例如本文VCO 输出频率为800~1600 MHz,可分为4个频率区间,每个频率区间的设定频率为该区间的中间频率,如表1 所示。图4 为VCO 输出各种频率下的上电锁定时间示意图,由图中可以看出VCO 输出频率 为800 MHz、1000 MHz、1200 MHz、1400 MHz、1600 MHz 时的上电锁定时间相差不大。

表1 频率区间以及区间中心频率

图4 各频率下上电锁定时间

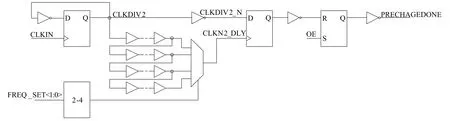

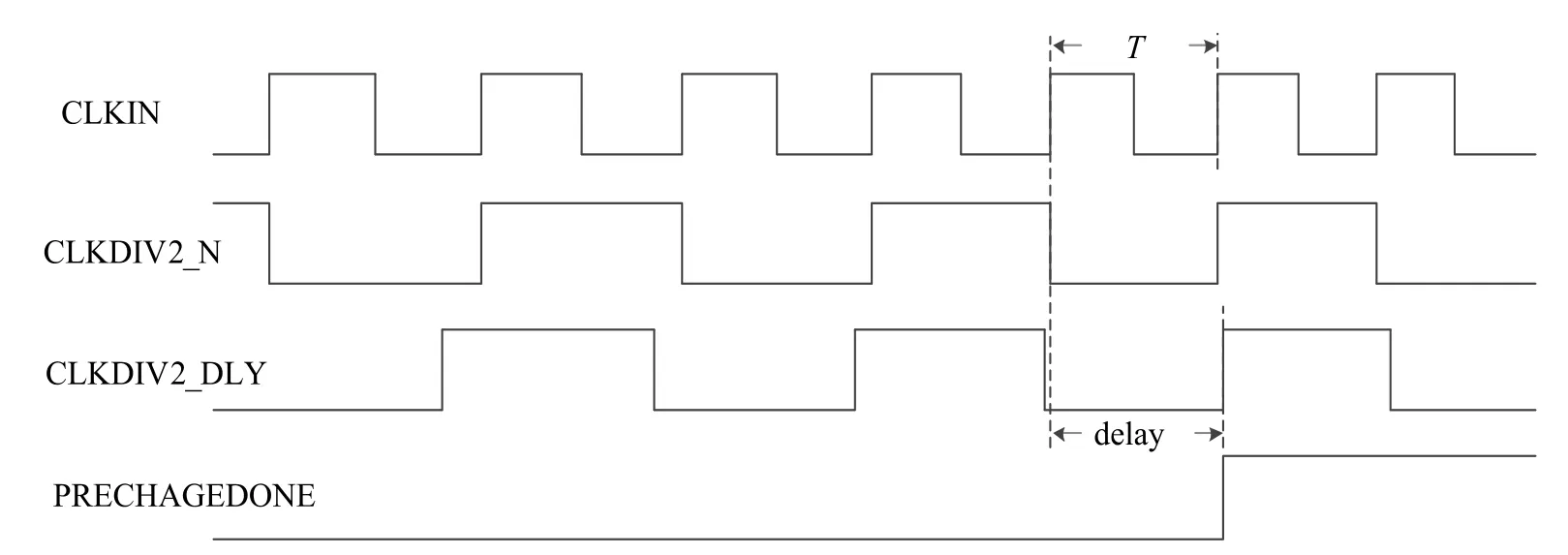

频率比较电路可通过比较时钟周期来实现,当VCO 输出时钟的周期小于设定频率的周期时,即可认为VCO 输出时钟频率大于所设定频率。图5 所示为频率比较电路的实现方式,其中CLKDIV2_N 为CLKIN 的2 分频取反,CLKDIV2_DLY 为CLKIN2 分频的延时,其延时的时间即为设定频率的周期。当CLKIN 的时钟周期小于设定频率的周期时,CLKDIV2_DLY 的上升沿将可以采到CLKDIV2_N 的高电平,这样输出PRECHANGEDONE 就会由低电平转为高电平,VCTRL预充电操作完成。为了避免所加辅助电路在VCTRL预充电完成后对PLL 的正常工作产生影响,在频率比较电路至PRECHARGEDONE 的输出路径中加入RS 触发器,使得当VCO 输出频率达到设定频率时即可保持PRECHAGEDONE 信号处于高电平状态,关断VCTRL预充电电流,不影响PLL 的功能。

为了适应宽频率范围PLL 的应用,本文在频率比较电路中做了延时可选配置,可根据输出时钟频率选择不同的延时值,实现宽频率范围PLL 的快速上电锁定。图6 为频率比较电路波形示意图,当delay 值大于CLKIN 的周期T时,PRECHAGEDONE 信号由低电平转为高电平,VCTRL的预充电操作完成。

图5 频率比较电路

4 仿真结果

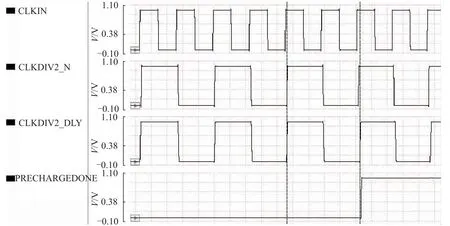

本文基于UMC 28 nm 工艺,利用Cadence 公司仿真工具spectre 对PLL 整体电路进行系统仿真。图7为频率比较器的仿真截图,当CLKDIV2_DLY 上升沿采到CLKDIV2_N 的高电平时,PRECHANGEDONE信号由低电平转为高电平,预充电完成。

图6 频率比较电路波形

图7 频率比较器仿真截图

图8 为VCO 输出频率分别为800 MHz、1000 MHz、1200 MHz、1400 MHz、1600 MHz 时的VCTRL仿真截图,可以看出不同VCO 输出频率下,VCTRL预充电达到的初始位置也不相同,符合图4 中的设计目标。

图8 VCTRL 电压仿真波形截图

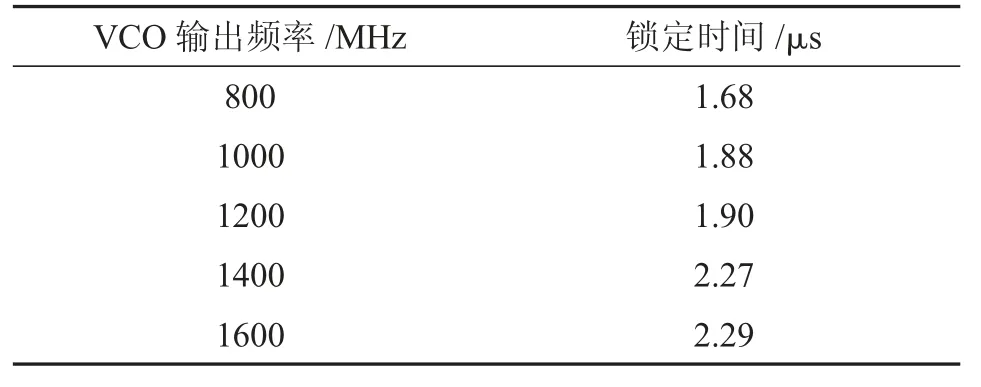

图9 所示为本例PLL 在VCO 输出频率分别为800 MHz、1000 MHz、1200 MHz、1400 MHz、1600 MHz时的锁定指示信号仿真截图,表2 为各频率下PLL 的锁定时间仿真数据。从表2 中可以看出本例PLL 在800~1600 MHz 的宽频率范围下,锁定时间范围为1.68~2.29 μs,最大锁定时间和最小锁定时间仅相差0.61 μs,实现了宽频率范围下PLL 的快速锁定。

表2 PLL 各频率下锁定时间仿真结果

5 结束语

本文介绍了一种宽频率范围电荷泵锁相环的快速锁定方法,通过在传统电荷泵锁相环里添加频率比较电路,将宽频率范围拆分为若干个窄频率范围,并结合预充电电路来实现VCTRL的快速充电,可大大减小并均衡宽频率范围电荷泵锁相环各频率下的上电锁定时间。本例PLL 在800~1600 MHz 的宽频率范围下,锁定时间范围为1.68~2.29 μs,最大锁定时间和最小锁定时间仅相差0.61 μs,实现了宽频率范围电荷泵锁相环各频率下的快速上电锁定。