基于皮尔斯振荡器的8 MHz 晶振电路设计

邵颖飞,鲁征浩

(苏州大学电子信息学院,江苏苏州 215006)

1 引言

电路设计中,需要一种产生时钟信号的振荡器,如晶振、RC 振荡器、环形振荡器等[1]。石英晶体振荡器的频率输出稳定且精确度高,因此在很多领域皆有广泛的应用,如电话通讯、全球卫星定位导航系统、精密电子仪器、微电子系统等[2]。石英晶体组成的振荡电路,其频率稳定度可达10-6~10-11数量级。在复杂的集成电路系统中,尤其是数字电路,需要一个稳定精确的时钟信号[3],皮尔斯(Pierce)晶体振荡电路常常在这些系统中被用作时钟发生器[4]。传统Pierce 晶体振荡电路的功耗大,起振时间长,单电压域工作且产生的输出时钟信号为正弦波,无法直接给数字电路使用。

本文设计了一种双电压域工作且输出时钟信号为方波的皮尔斯晶体振荡电路,由皮尔斯电路、使能控制及隔离电路、偏置电路和整形及电平移位电路组成。偏置电路可在功耗和起振时间之间实现折中。整形电路可将正弦波整形成占空比为50%±5%的方波。电平移位则能将输出波形的幅值从模拟电压域转换到数字电压域,实现双电压域工作。

2 振荡器原理及参数

在选择滤波器件时,一般优先考虑石英晶体。石英晶体包括一块平板压电电阻材料,可实现机械能与电能的转换[5]。石英晶体一般作为芯片的外围电路使用,很少集成到芯片内部。为便于对设计的晶振电路进行仿真分析,本文给出了一个8 MHz 石英晶体的电路模型。

2.1 改进的皮尔斯振荡电路

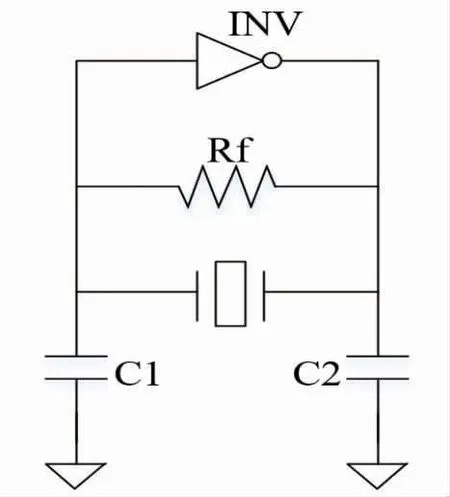

典型的皮尔斯振荡电路如图1 所示。它由两部分组成:一部分是反相器,主要用于提供180°相移;另一部分是由外部负载电容组成的反馈网络,用以提供电路所需的另一个180°相移。为了使反相器能够工作在线性区,在电路中需要引入反馈电阻RF。反相器和反馈电阻组成一个反向放大器,以实现晶振起振的目的。

皮尔斯振荡电路若要正确起振,则需满足巴克豪森准则:第一个条件,该电路在稳态下的整体相移为360°[6];第二个条件,该电路环路增益应大于或等于1[7]。

图1 皮尔斯振荡电路

C1、C2为晶振外部的2 个匹配电容,与石英晶体构成π 形网络带通滤波器。通过对这2 个小电容的值的微调,可以使晶振电路产生的频率调整到晶体的标称频率。

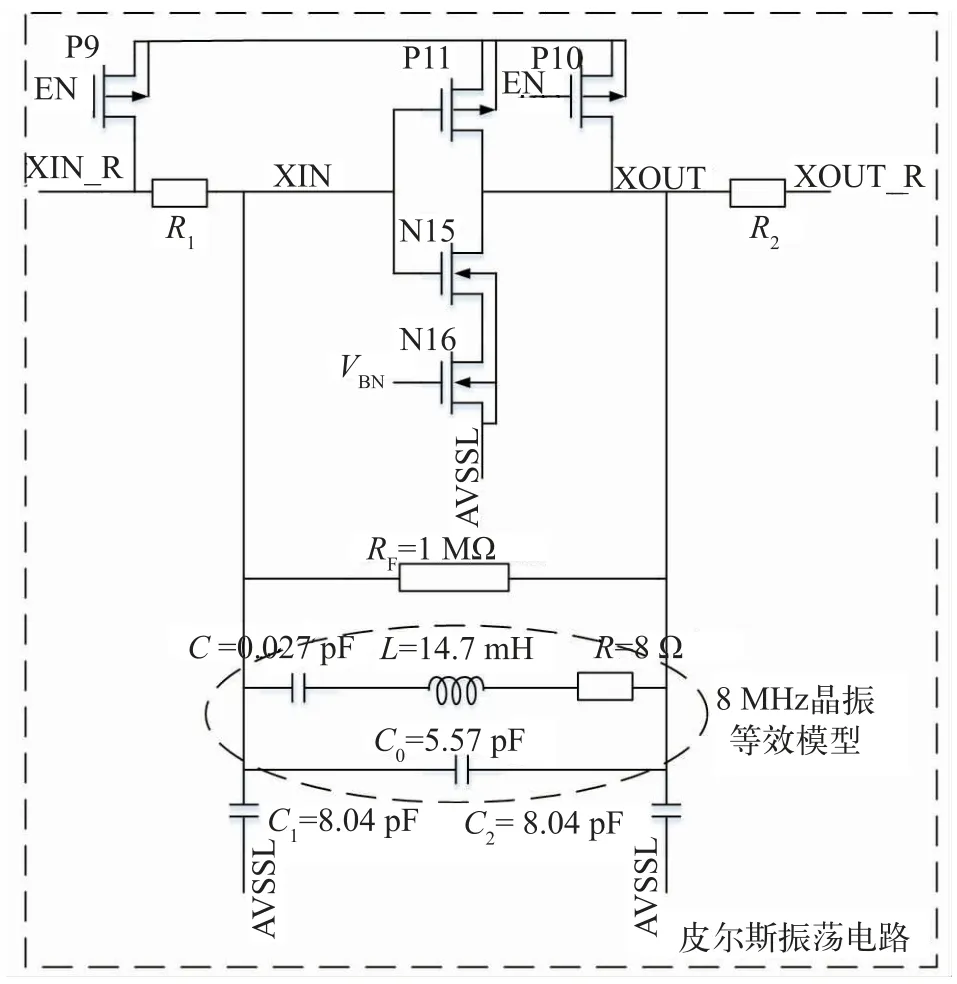

反馈电阻RF的阻值不能太小,否则会导致环路无法振荡,其值一般大于等于1 MΩ。本文改进的皮尔斯振荡电路如图2 所示,与传统皮尔斯振荡电路相比,改进后的电路功耗减小且起振时间缩短。

图2 改进的皮尔斯振荡电路

N16 管的栅极输入VBN由偏置电路提供。偏置电路正常工作时,VBN信号为一固定电压,使得N16 管保持导通,反相放大电路中的工作电流被限制,同时保证该工作电流能够维持反相放大电路的正常工作。该设计可以减小皮尔斯振荡电路的功耗,又能将起振时间控制在一个合理的范围内。

2.2 8 MHz 石英晶体等效模型

石英晶体的等效电路主要由动态电阻R、动态电感L、动态电容C和静态电容C0组成。本文给出一个8MHz石英晶体等效模型,对应的等效器件参数见表1[8]。

表1 8 MHz 晶振等效参数

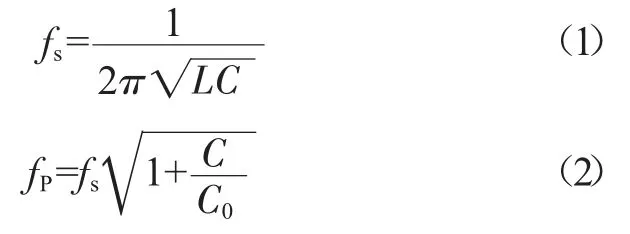

在高稳晶振设计中,需要设计一个可以满足设置频率且能精确调整频率范围的电路结构。在此情况下,在设计中就需要关注串联谐振频率(fs)、并联谐振频率(fP)和标称频率(fN)。它们的表达式分别为:

本文选用的石英晶体标称频率fN为8 MHz。fN的值应介于fs的值和fP的值之间。在该区域间,石英晶体呈感性,具有很高的品质因数,可在振荡电路中起到很强的稳频作用。根据表1 中的数据,计算可得fs=7988770 Hz,fP=8008109 Hz。

从式(3)中可以看出,若想让晶体振荡时能达到标称频率,可以通过调节负载电容CL来微调振荡电路的频率。根据选用的晶体参数,计算可得CL=4.03 pF。

振荡电路的增益裕量决定了振荡电路是否能正常起振。基于振荡电路设计理论,反相器跨导gm和晶振本征增益g0必须满足gm>g0。为保证振荡器可靠起振,增益裕量的最小值至少设为5。

皮尔斯振荡电路中的跨导为反相器中P11 管和N15 管的跨导之和,利用上述条件,可以计算出P11 管和N15 管的宽长比,从而实现电路设计。

3 电路设计

本文设计的晶振电路能够实现双电压域工作,输出时钟为方波,功耗小,起振时间短。偏置电路用来限制高电压时的工作电流,以减小电路功耗,同时避免高电压时的工作电流太小,以获得合理的起振时间;整形电路用于正弦波的整形,以输出可作为时钟信号使用的方波;电平移位电路用于实现整体电路的双电压域工作。

除石英晶体及外部电容C1、C2外,其他器件均可集成在电路内部。偏置电路、皮尔斯振荡器和整形电路的电源电压VDD3P3为3.3 V,电平移位电路的电源电压VDD1P5为1.5 V。

3.1 偏置电路

偏置电路如图3 所示。VBN信号能够控制皮尔斯振荡电路中反相放大电路的工作电流,使该工作电流的数值在一个合理范围之内,以达到减小电路功耗的目的。ENN 信号由使能控制电路提供,当ENN 信号为低电平时,偏置电路正常工作。

图3 偏置电路

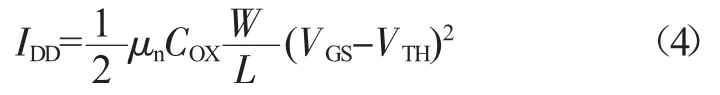

N11~N13 管的VGS等于VDS,VBN电压值就等于N11~N13 管的VGS相加。电流公式为:

其中,VGS-VTH为过驱动电压,W/L为管子的宽长比,μn、COX为工艺常数。由式(4)可知,VBN大小可通过调节N11~N13 管的W/L实现。

3.2 整形及电平移位电路

整形及电平移位电路如图4 所示。皮尔斯振荡电路的输出波形为正弦波,为得到方波形式的时钟信号,采用整形电路对晶振产生的正弦波进行整形。本文选用比较器和反相器作为整形电路。为实现电路的双电压域工作,反相器兼具了电平移位的功能。整形电路工作在3.3 V 电压域,电平移位电路工作在1.5 V电压域。

皮尔斯振荡电路正向接入比较器1,反向接入比较器2,使得比较器1 和2 的输出波形相差180°相位,将两者接入比较器3 中再次对波形整形。根据比较器的原理,每一级比较器都起到了整形电路的作用,可将振荡电路输出的正弦波整形成矩形波。

经过比较器整形后,电路输出的波形不够完美,通过3 级CMOS 反相器,再次对输出波形进行整形。反相器只需要输入端达到一定的翻转电压,就能使输出电平发生翻转,故可在一定的电压范围内实现电平移位。且最后一级反相器的W/L做得大些,可以增强整个晶振电路输出的驱动能力。

通过比较器和反相器,晶振产生的正弦波被整形成了形状良好且符合数字电压域的方波[9],可直接给数字电路提供时钟输入。整形及电平移位电路能够输出数字时钟,且实现双电压域工作的功能。

图4 整形及电平移位电路

4 仿真验证

为了验证本文设计的基于皮尔斯振荡器的8 MHz 晶振电路能够正常工作,且功耗相比传统的晶振电路有所减小,采用宏力0.11 μm 的器件模型,用Cadence Spectre 仿真软件进行仿真验证。

4.1 瞬态仿真(tran)

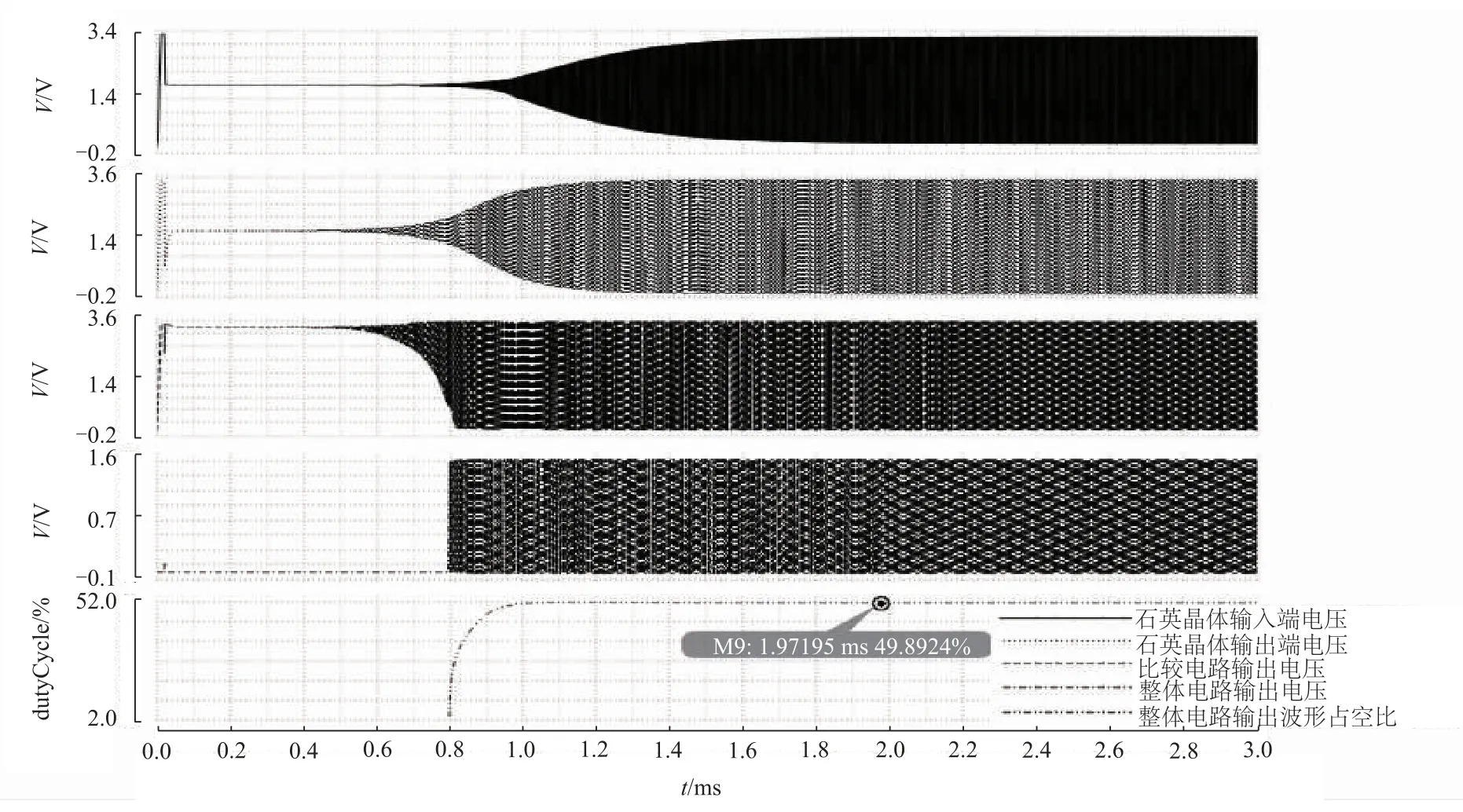

在20 μs 时,对电源电压VDD3P3和VDD1P5施加一个阶跃信号,石英晶体两端的信号XIN、XOUT和整体晶振电路输出信号DOUT的波形如图5 所示。

图5 8 MHz 晶振电路的瞬态响应波形

仿真结果显示,接入电路的晶体两端XIN和XOUT在0.35 ms 后开始起振。正常工作时,晶振电路的瞬间最大电流为1.67 mA。经计算,平均电流为350 μA。可以通过调整偏置电路的输出电压来调整电路中的工作电流,但需综合起振时间与工作电流考虑。波形的局部放大图如图6 所示。

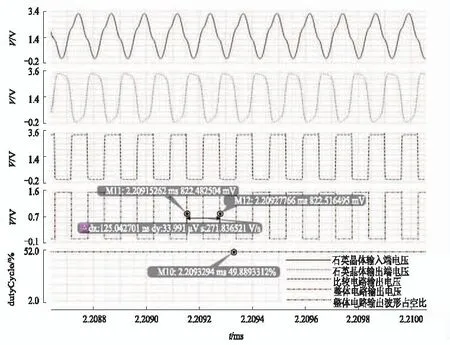

石英晶体两端XIN和XOUT上的波形接近正弦波。振荡器的输出幅度为3.3 V,频率与正弦波的频率一致,为8 MHz。比较电路输出的波形为矩形波,通过几级反相器整形,整体电路输出端DOUT上的波形为方波,误差为0.11%,输出幅度变为1.5 V,频率仍为8 MHz。典型条件下,晶振电路仿真参数如表2 所示。

图6 8 MHz 晶振电路的瞬态响应波形局部放大图

表2 8 MHz 晶振电路仿真参数总结

4.2 多工艺角仿真(PVT)

为验证不同条件下的晶振工作情况,对设计好的晶振电路进行PVT 仿真。仿真结果见表3。

根据表3,可知起振时间的最小值为0.13 ms,最大值为0.38 ms;工作电流的最小值为107 μA,最大值为1380 μA;占空比的最小值为48.88%,最大值为52.59%。各个条件下的仿真结果都在典型值的合理误差范围内,即晶振电路在各个工艺角下都能够正常起振,且输出波形的占空比误差在±3%之内。

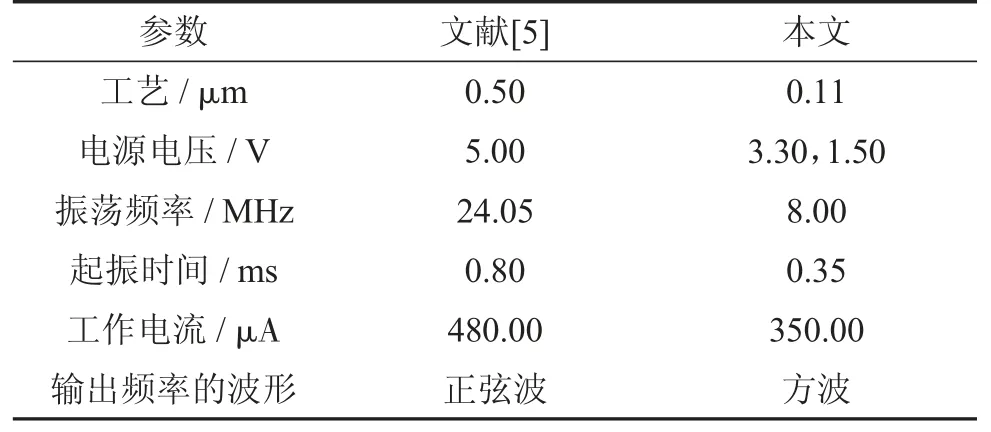

文献[5]的电路设计指标与设计电路的对比如表4所示。与该电路的设计指标相比,本文设计的8 MHz晶振电路工艺先进,起振时间短且工作电流小。本晶振电路拥有2 个工作电压域,能够实现模拟电压域到数字电压域的电平移位,输出的频率波形为方波,且幅值为数字模块的电压域,应用于数模混合电路时,可直接用作数字电路的时钟输入,不需另加电路。

表3 8 MHz 晶振多工艺角仿真参数

表4 8 MHz 晶振电路设计指标与现有文献对比

5 结论

本文在分析石英晶体等效电路和典型皮尔斯晶振电路的基础上,设计了一款基于皮尔斯振荡器的8 MHz 晶振电路。在该电路中,输出时钟波形为方波,满足双电压域工作,且相较于其他晶振电路,本文设计的晶振电路功耗小,起振时间短;采用宏力0.11 μm的工艺模型,对晶振电路进行了瞬态分析及PVT 仿真。仿真结果显示,振荡器的振荡频率为8 MHz,工作电流为350 μA,起振时间为0.35 ms,输出波形为1.5 V 幅值的方波,且占空比为49.89%。该电路可被应用于数模混合CMOS 集成电路,作为数字模块的时钟输入。