SAE AS6802 协议研究及模块化仿真平台设计

何向栋,孙靖国,陈长胜,王建宇,贾世伟

(中国航空工业集团公司西安航空计算技术研究所,西安 710065)

0 概述

目前,航空电子技术正朝着分布式综合模块化体系架构(Distributed Integrated Modular Architecture,DIMA)和标准化的方向发展,其复杂度日益增加,机载信息量、综合化程度不断提高,这对通信网络的实时性和容错性等提出了更高的要求,尤其是在安全关键和任务关键的应用领域。当前,应用在航电系统的总线均基于事件触发网络,如AFDX(Avionics Full Duplex Switched Ethernet)[1]。AFDX 网络作为航电系统的骨干网络,已经得到广泛应用,其采用速率限制(Rate-Constrained,RC)数据流传输,虽然保证了通信具备一定的确定性,但是其抖动时延为百微秒级,仍无法满足安全关键任务的时延需求[2]。

时间触发网络(Time-Triggered Ethernet,TTE)[3]是在IEEE 802.3 以太网基础上实现的实时网络协议,其融合了时间触发[4]、速率限制[5]和普通以太网数据流等混合流量机制,引入透明时钟[6]和时间同步[7]的概念,提供了严格的时间确定性与极好的容错性能[8],成为DIMA[9]航电系统体系架构[10]的骨干通信网络[11]。时间同步和时间触发通信机制的引入[12],增强了系统的时间确定性,提高了实时服务质量和错误隔离能力,其适用于高安全关键应用领域。TTE 已在火星项目“猎户座Orion”中得到洛克希德·马丁、Honeywell、西科斯基飞机以及通用电气等公司的应用支持,特别地,奥地利的TTTech 公司已经推出了多款具有商用价值的TTE 产品。目前,国内高校及科研院所尚处于算法理论研究阶段,多数就TTE 网络的相关算法[13]或某一特性进行分析与研究[14],尚未见成熟产品面市。

本文分析SAE AS6802 协议,分别对时间同步角色、时序保持算法、集中控制算法及同/异步派系检测等关键技术进行研究,设计实现时间同步算法IP核,搭建基于SystemVerilog 的模块化仿真平台,以验证时间同步算法的正确性。

1 时间触发协议分析

SAE AS6802 协议对时间触发网络中最重要的全局时间同步算法进行研究,而并未对传输物理特性、3 种业务流量通信调度(时间触发、速率限制和普通以太网数据流)及网络节点架构等作出说明。从广义的角度而言,SAE AS6802 协议可以将时间同步算法拓展到其他任何通信网络中。

1.1 算法研究

时间同步功能主要通过协议控制帧(Protocol Control Frame,PCF)实现,帧内容主要包括如下关键参数:整合周期(Integration Cycle),成员向量(Membership New),同步优先级(Sync Priority),同步域(Sync Domain),帧类型(Type),透明时钟(Transparent Clock)等。时间同步的关键点在于静态的时间计算配置、PCF帧通信交互及多种算法实现,同步流程如图1 所示。

图1 时间同步流程Fig.1 Time synchronization process

时间同步流程具体如下:

1)同步控制器(Synchronization Master,SM)向集中控制器(Compression Master,CM)发送PCF。在集中控制器CM 收到与之相连的各链路上不同的PCF 帧(PCF1~PCF3)之后,对接收到的PCF 帧进行时序保持,即保证PCF 帧的接收顺序与其发送顺序相同,然后根据接收到的PCF 帧携带的信息、到达时间以及全局时钟同步协议执行集中控制算法。

2)将第1 步的计算结果写入一个新的全局统一的PCF 帧(New PCF)中,发向时间触发网络中的各个构件,包括同步客户(Synchronization Client,SC)和同步控制器SM。网络中的各个构件收到由集中控制器CM 发回的PCF 之后,根据PCF 帧所携带的信息校正自己的本地时钟从而实现全局同步。

1.1.1 时序保持算法

时序保持算法[15]通过PCF 帧中的透明时钟和最大传输延迟,恢复各个SM 的真实时间先后顺序。其中,透明时钟Ttransparent_clock记录了PCF 帧在传输过程中的时间消耗,包括发送延迟Tsend_delay、链路延迟Twire_delay、转发延迟Trelay_delay和接收延迟Treceive_delay,如式(1)所示:

最大传输延迟Tmax_transmission_delay是指整个网络系统中任意2 个节点之间的最大延时,其为一个离线得到的通信配置值,在网络拓扑确定后,该值也随之确定,如式(2)所示:

网络拓扑、网络节点角色、链路长度以及链路速率等变化,造成各个节点到达目标节点SM 或者CM的先后顺序与实际发送顺序不一致,时序保持算法将恢复其原来的真实序列,如式(3)所示:

其中,PT(Point of Time)表示时刻,PTpermanence_pit表示时序保持点,PTreceive_pit表示接收节点的接收时刻。

式(3)将接收的PCF 帧延迟到最大传输延迟时刻。由于透明时钟不同,因此将各PCF 帧延迟至最大传输延迟时刻即正确恢复了各个发送节点的时间先后顺序。

1.1.2 集中控制算法

时序保持算法排列出PCF 帧的时间先后顺序,从而表征了各个SM 节点的时间差值。各个SM 的身份标识由PCF 帧携带的成员向量确定。集中控制算法主要对时序保持算法的PCF 帧进行集中收集、计算差值、求解差值平均值、修正时间并产生一个新的PCF 帧,然后广播至各个SM 或SC,进而实现全网的时间同步。集中控制算法主要包括3 个阶段:收集阶段,计算阶段,延时阶段,具体如下:

1)收集阶段

一个协议控制帧PCF 在到达时序保持点且当前该整合周期内没有其他集中控制算法正在收集PCF帧时,开启一个观察窗口(Observation Window,OW),OW 的大小一般设置为同步精度p(precision)。在收集阶段持续保持对PCF 帧的收集,如果每个OW 都有PCF 帧被收集,则开启一个新的窗口,继续收集PCF 帧。当开启的OW 窗口数为f+1(f为系统容错的设定值),或者新开启的OW 窗口内无PCF 帧时,进入计算阶段。值得注意的是,每个集中控制算法中收集的PCF 帧必须在同一个同步域、同一个整合周期、高于或等于第一个PCF 帧的同步优先级,否则,重新开启另一个集中控制算法。

2)计算阶段

根据收集阶段采集的PCF 帧与第一个接收PCF帧的接收时钟差值计算一个均衡值,计算时通过所收集PCF 帧的数目来确定计算规则,具体计算方法如式(4)所示:

其中,n表示收集阶段的PCF 帧个数,tn表示第n个PCF 帧与第一个PCF 帧的时钟差值分别表示n个时钟差值中的第k大值和第k小值。

3)延时阶段

式(4)中的Δt即为各个SM 的时钟偏差均衡值,也即延时阶段的延时值。时钟差值的不同和所收集PCF帧数的不同,导致延时值不一致、CM 的实际集中时间点cm_compressed_pit 与预计时间点cm_scheduled_pit不一致以及时钟差值不一致。

1.1.3 时钟纠正

时钟纠正首先需要计算时钟差值。TTE 的时钟差值等于离线计算的预计接收点与实际接收点的差值。对于同步集中器CM 而言,clock_corr 的ΔT计算如下:

对于同步控制器SM 和同步客户端SC 而言,clock_corr 的ΔT计算如下:

其中,smc_scheduled_pit 为SM/SC 的预计时间点,smc_permanence_pit 为实际时序保持点。

在本地时钟上直接进行时钟差值修正,如下:

1.1.4 派系检测

在同步通信过程中,在同一同步域内出现某些子同步派系,此时将不能进行全域同步。为解决该问题,需要对派系进行检测。派系检测可分为同步派系检测、异步派系检测和相对派系检测3 种方式。

同步派系检测是指在SM/CM/SC 的同步派系评估时刻sync_eval_pit,判定在当前整合周期内且落在接收窗口内的成员向量个数local_sync_membership与设定的阈值sync_threshold_sync 之间的关系,若local_sync_membership 异步派系检测是指在SM/CM/SC 的异步派系评估时刻async_eval_pit,判定不在本整合周期内且落在接收窗口之外的成员向量个数local_async_membership与设定的阈值sync_threshold_async 之间的关系,若local_async_membership>sync_threshold_async,则异步派系检测成功;否则,检测失败。 相对派系检测是指在SM 异步派系评估时刻async_eval_pit,判定同步派系值local_sync_membership与异步派系值local_async_membership 之间的关系,若local_sync_membership≤local_async_membership,则相对派系检测成功;否则,检测失败。 上述3 种派系检测算法对同步子集合进行实时检测,当3 种派系检测算法均检测成功时,网络构件进入失同步状态。若要再次进行同步,则需要重新进入冷启动握手或侦听IN 帧阶段,然后进入新的时间同步周期进行操作。 1.1.5 通道择优 在具体的网络拓扑中,网络规模、配置角色和冗余设计等不同,导致存在多个可同时满足同步需求的PCF 帧,此时需要选择最优通道的PCF 帧作为最优PCF 帧进行同步,择优计算具体如下: 在式(8)中,择优标准为:在接收的PCF 帧中,选择成员向量个数最大且时序保持时刻最近的PCF 帧。 依据上述SAE AS6802 协议的算法研究和协议中第9 章“启动与重启服务”内容,本文设计SAE AS6802 时间同步IP 核,如图2 所示。 图2 同步IP 核结构Fig.2 Synchronous IP core structure 时间同步IP 核中的各个模块功能具体如下: 1)端口0~端口N:端口对接收到的帧数据进行分析,解析出PCF 帧字段,包括同步域、同步优先级、透明时钟、帧类型、成员向量和整合周期等,同时记录接收时刻。 2)时序保持模块:对接收的PCF 帧进行时序保持计算,在达到时序保持时刻时上报至SM/SC/CM控制状态机。 3)SM 控制状态机:依据AS6802 协议的第9 章内容实现SM 的同步状态机。 4)SC 控制状态机:依据AS6802 协议的第9 章内容实现SC 的同步状态机。 5)CM 控制状态机:依据AS6802 协议的第9 章内容实现CM 的同步状态机,其包括普通完整性CM状态机和高完整性CM 状态机。 6)寄存器、参数计算模块:主要实现参数配置和计算功能。参数配置主要包括接收/发送延时、同步阈值、容错系数f、整合周期个数、最大传输延迟、同步域、优先级、同步精度、派发延迟和超时等参数。计算功能主要结合上述配置参数进行接收时刻、发送时刻、纠正时刻、派系评估时刻等计算。 时间同步IP 核输出同步时钟和同步状态以及发送PCF 帧信息,此IP 核在工作时只能作为SM、SC 或CM 中的一种同步角色。本文设计的时间同步IP 核完全满足SAE AS6802 协议的设计要求,独立于物理传输协议,可适用于基于IEEE 802.3、FC、总线等底层通信协议。 基于SAE AS6802 的时间同步算法的同步精度虽然相对于现有时间同步算法PTP[16]、DTP、NTP 等有较大提高,但在实际应用中,仍存在限制其同步精度提升的因素,主要包括时钟精度及漂移[17]、同步周期频率和透明参数准确度。 1.3.1 时钟精度及漂移 在实际的通信网络中,各个网络构件(交换机或端系统)的本地时钟(如晶振)精度值不一致,且与真实的时钟相比存在一定的偏差,即时钟漂移[18],这两者是各个网络构件间时间同步精度不同的重要影响因素。 假设网络中2个构件的本地晶振频率分别为FaMHz和FbMHz,本地晶振的时钟偏移采用ppm(part per million)作为衡量,2 个构件的本地晶振时钟偏移分别表示为Pa和Pb。假设一个同步整合周期为Tins,则在一个整合周期内,网络构件A的最大偏移为,网络构件B的最大偏移为,则2 个网络构件之间的最大时钟差值ΔTclk为两者之间的正负偏移之和,如下: 在式(9)中,假设Pa为100 ppm,Pb为50 ppm,Tin为0.01 s,则2 个网络构件在一个整合周期0.01 s 内的固有最大时钟偏差为1.5 μs。因此,对于高安全关键应用领域,其网络构件的本地时钟应选择高品质的时钟晶振。 1.3.2 同步周期频率 从式(9)可以看出,基于SAE AS6802 协议的同步精度与整合周期[19]也紧密相关。在整合周期为0.01 s 时,其固有时钟偏差为1.5 μs;在整合周期为0.1 s 时,其固有时钟偏差为15 μs。因此,整合周期越小,同步周期频率越快,时间同步精度越高,同步精度与同步周期频率之间成正比关系,如式(10)所示: 其中,ΔTprecision表示同步精度,ε表示正比系数,该系数与具体的网络特性相关表示同步周期频率。 在同步网络中,同步周期频率越快,同步精度越高,但同时由同步带来的带宽开销也随之增加。因此,网络系统设计者需要综合任务关键程度、带宽、网络规模和角色分配等多种因素来决定整个网络的同步周期频率。 1.3.3 透明参数准确度 同步算法依据大量的透明时钟参数进行计算,包括发送延迟、转发延迟、接收延迟和线延迟等参数,这些参数的准确度同样决定了网络静态配置时刻的准确度。 如果透明参数的记录或计算与静态配置的计算之间误差偏大,如动态的发送或转发延迟,其随物理端口处竞争带宽而动态变化,则实际时刻与静态配置时刻就存在设计上的同步时间误差,从而导致时间同步精度降低。因此,对透明时钟进行准确记录也是提高时间同步精度的重要因素。 考虑到时间同步算法的复杂度以及存在同步角色、网络拓扑、余度架构以及网络速率等不同的复杂应用场景,需要搭建合理且易用的模块化仿真测试环境,以验证满足SAE AS6802 协议的时间同步IP核的正确性。 在复杂的同步测试场景以及存在各种同步因素的实际应用中,测试需求如表1 所示。 表1 测试需求Table 1 Test requirements 面对复杂的测试要求,本文仿真测试平台设计采用面向对象的硬件验证语言(Hard-ware Verification Language,HVL)SystemVerilog,其具有接口、断言、受约束的随机化激励等特点,能够大幅提高测试效率,且具有较高的功能测试覆盖率。 为了对时间同步IP 核进行仿真测试,本文搭建的测试平台主要包括时钟模拟模块、发送/链路/接收模块、故障节点模拟模块以及配置IP 核模块等。 2.2.1 时钟模拟模块设计 网络构件的本地时钟精度和时钟偏移是时间同步精度的重要影响因素,鉴于各个本地晶振品质[20]的不同,为了测试真实通信环境,需要建立一个本地时钟模拟模块,如图3 所示。 图3 受约束的随机时钟示意图Fig.3 Schematic diagram of constrained random clock 在图3 中,时钟晶振品质以时钟周期(单位为MHz)为基本周期值,以时钟偏移(ppm)为约束条件,模拟产生不同的网络构件本地时钟。 2.2.2 发送/链路/接收模块设计 发送/链路/接收模块主要模拟PCF 帧的传输过程。其中,发送指PCF 帧在链路层、物理层及变压器中的发送过程,链路指PCF 帧在物理媒介中的传输过程,接收指PCF 帧在变压器、物理层和链路层的接收过程。发送/链路/接收模块如图4 所示。 图4 发送/链路/接收模块示意图Fig.4 Schematic diagram of transmit/link/receive module 在图4 中,发送/链路/接收模块主要实现PCF 帧的传输延迟,即PCF 帧在SM 或CM 产生之后进行一个发送延迟、线延迟和接收延迟,再进入接收时间同步IP 核中。其中,发送延迟和接收延迟与具体的链路层/物理层设计相关,可查看相关器件手册获取。线延迟Twire_delay计算公式如下: 其中,Llink_length为线缆长度,为传输速率。 值得注意的是,在同一网络中,可以存在多种不同的网络传输速率、线缆长度及发送/接收延迟,这样更能模拟真实的网络环境。 2.2.3 故障节点模拟模块设计 故障节点模拟主要针对PCF 帧进行模拟,其目的是受约束地随机生成一个PCF 帧类型,随机化的内容主要包括整合周期、成员向量、同步优先级、同步域、帧类型、透明时钟等,并在受约束的注入时机控制下进入网络拓扑中。 2.2.4 模块化平台设计 本文结合仿真模块和时间同步IP 核设计,搭建典型的模块化仿真平台,如图5 所示,其同时仿真测试时间同步IP 核的SM、SC 和CM 功能。 图5 模块化仿真平台设计示意图Fig.5 Schematic diagram of modular simulation platform design 在图5 中,首先由本地时钟模拟模块、初始配置单元(主要作用为初始化配置时间同步IP 核的基本参数)和时间同步IP 核等组成网络节点,网络节点由发送/链路/接收模块互联,故障节点实现PCF 帧的故障注入,以查看同步运行的稳定性。 从图5 可以看出,该仿真测试平台具有灵活的可配置性,可根据表1 的测试需求组合搭建不同规模数量的网络拓扑,从而提高测试效率和功能覆盖率。 对时间同步IP 核的基本功能进行仿真测试,仿真拓扑如图5 所示,基本通信参数设置如下:整合周期为2 ms,最大传输延迟为500 μs,时间同步精度为1 μs,整合周期个数为5,线缆长度为10 m,传输速率为1 Gb/s,仿真结果如图6 所示。 图6 时间同步仿真结果Fig.6 Time synchronization simulation result 同步精度结果如图7 所示,图中分别对SM0 与SM1、SM 与SC、SM 与CM 的时钟差值进行比较,均差值约为150 ns,最差精度在300 ns 以内,满足时间同步精度1 μs 的设计要求。 图7 同步精度结果Fig.7 Synchronization accuracy result 从图7 可以看出,同步角色SM、SC 和CM 状态机满足SAE AS6802 协议第9 章内容要求,结合同步输出状态local_sync_status_sm0/sm1/cm/sc 和时钟值local_clk_sm0/sm1/cm/sc 进行分析得出,SM、SC 和CM 同步工作稳定,同步精度达到300 ns 以内,验证了本文时间同步IP 核功能正确。 本文对时间触发网络TTE 协议进行分析,研究时间同步算法技术、时间同步流程、同步角色、时序保持算法、集中控制算法、时钟纠正算法以及同/异步派系检测,设计实现时间同步IP 核,并从测试角度出发,构建多参数、多复杂场景下的模块化仿真验证平台。仿真结果表明,该时间同步IP 核的时间同步精度可以达到亚微秒级,且具有较高的鲁棒性。为了进一步分析时间同步IP 核的同步性能,后续将在不同同步域、多种业务数据流混合的通信环境中进行研究,以提升该IP 核在机载网络通信中的健壮性。

1.2 同步IP 核设计实现

1.3 同步因素

2 模块化仿真平台设计

2.1 测试需求

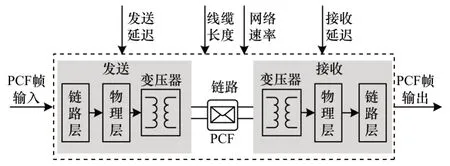

2.2 模块设计

3 仿真测试

4 结束语