基于Zynq的振动信号采集及频谱分析

谢玲芳,孟令军

(中北大学,电子测试技术国防科技重点实验室,山西太原 030051)

0 引言

Zynq-7000可扩展处理平台由ARM处理器和7系列FPGA资源构成,分别叫做PS(processing system)和PL(programmable logic)[1]。PS包含双核Cortex-A9,其启动和操作系统的运行不依赖可编程逻辑单元,PL包含FPGA逻辑单元,在该部分完成的各个功能模块可以封装为独立的IP核挂载在内部总线上,由ARM选择驱动与调度。这一架构充分发挥FPGA并行运算的优势,同时利用处理器系统的灵活性,增强了实时数据传输的稳定性,为高速信号的采集与处理提供一种新的设计方案。通过软硬件协同设计实现多路振动信号采集及频谱分析,提取信号的频谱信息,分析特征完成振动故障分析。

1 系统整体设计

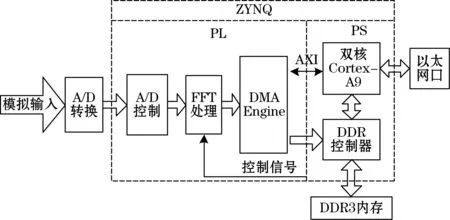

系统选择Zynq-7000 SOC平台作为控制核心,经过前端信号调理后,由可编程A/D转换、DMA传输、FFT变换和以太网传输来实现振动信号的采集和频谱分析。系统框架如图1所示。

图1 系统整体框架图

振动传感器采集的模拟信号作为前端输入信号。Zynq-7000的PL部分控制AD7606进行模数转换、FFT变换,通过AXI4总线协议进行DMA传输,将数据传输到处理器,经过 DDR3缓存,PS部分实现串口、千兆以太网的控制,完成PS端到PC端的数据传输以及PC端到PS端的指令传输。

1.1 A/D转换

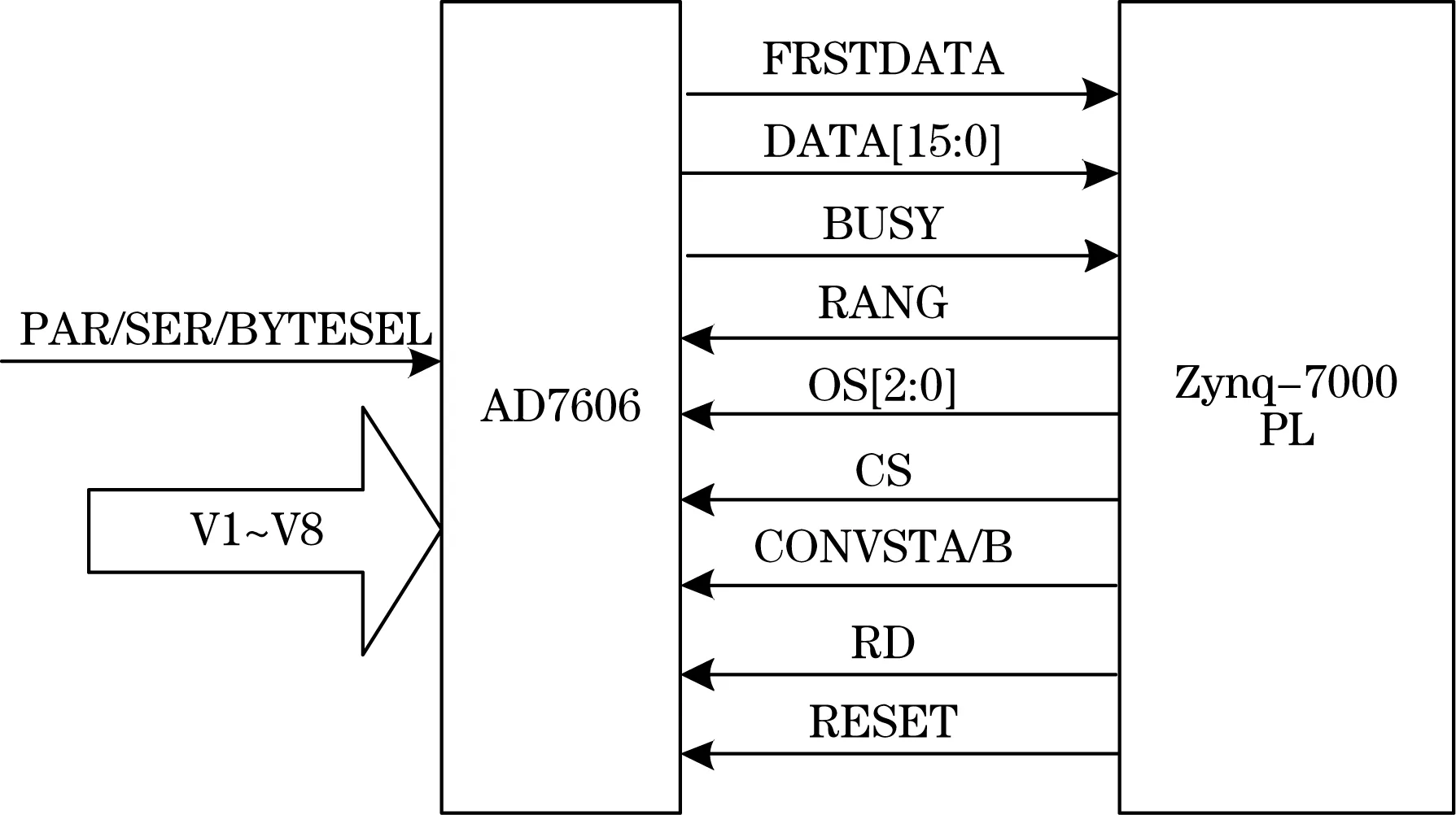

在本设计中,信号输入频率最大为50 kHz,即fmax=50 kHz。为了保证信号被完整复原,采样频率需满足fs≥2fmax,实际应用中,常选取2.5倍,因此fs至少取125 kHz,而且对采样精度有较高的要求[2]。综上所述,采用AD7606,具备 200 Ksps 的采样率,16 bit 采样精度,8路同步采样,灵活的串行并行接口,并且内部配有可设置的 FIR 滤波器[3]。A/D电路采用5 V单电源供电。AD7606与Zynq接口如图2所示。

图2 AD7606与Zynq硬件接口图

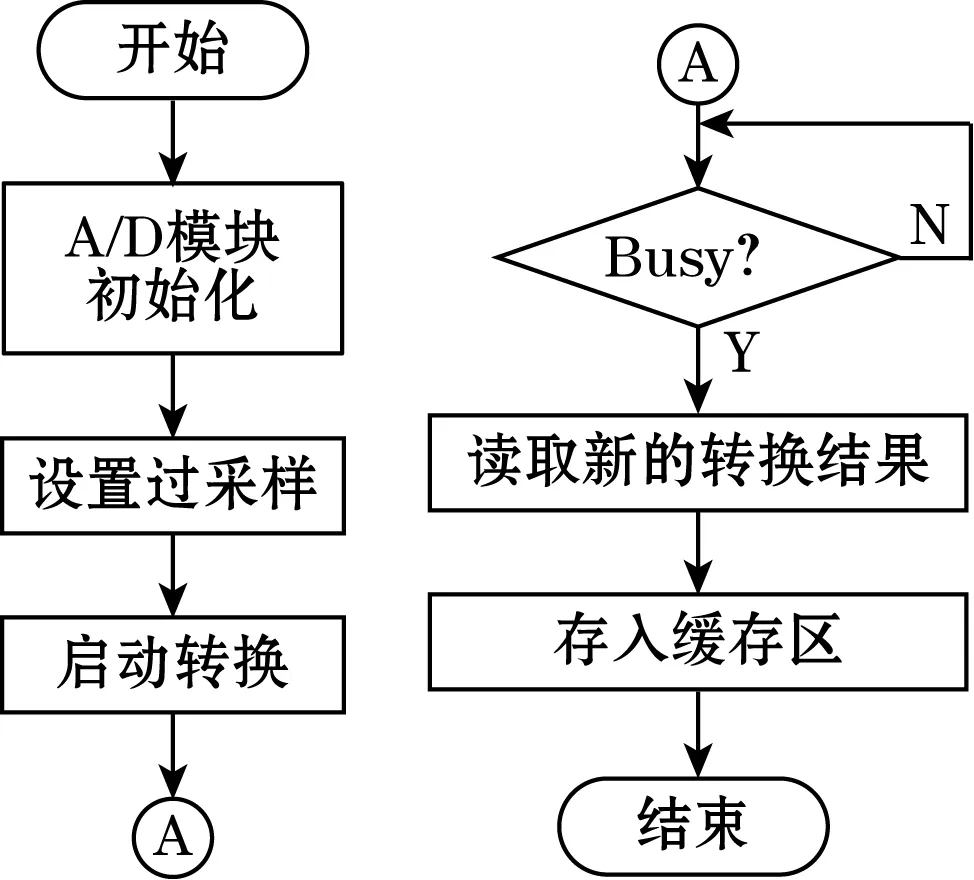

A/D控制模块首先进行AD7606初始化,OS信号接低电平设置为无过采样;RANG引脚接地用来设定模拟输入电压范围是±5 V;V1~V8共8路模拟输入信号为调理后的输出电压;PAR/SER/ BYTESEL引脚接地设置A/D为并行工作模式。其控制流程如图3所示,仿真结果如图4所示。

图3 AD7606控制流程图

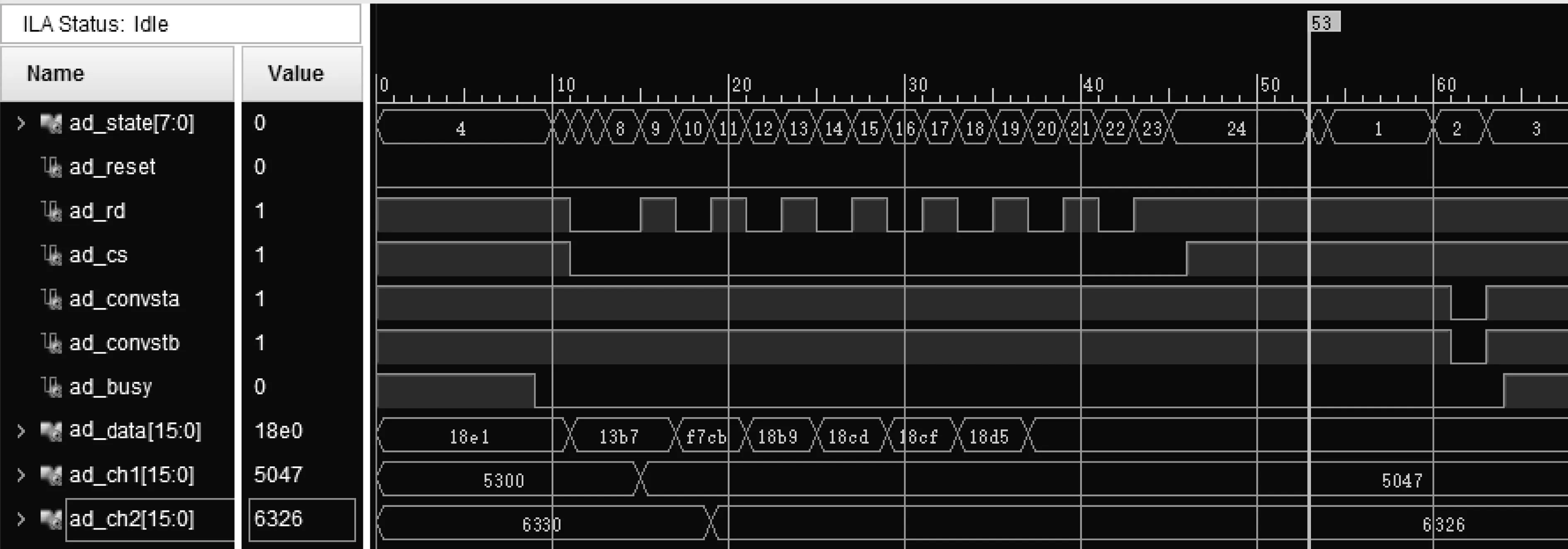

由图4可知,在转换开始信号ad_con- vsta/b的上升沿开始进行模数转换,随后转换忙碌标志ad_busy跳转为高电平,等待8个通道均完成转换再恢复低电平。此时等到片选信号ad_cs和读取使能ad_rd有效时,依次读出所有通道新的转换结果(图4列出了2个通道ad_ch1和ad_ch2)。或者可以在ad_busy为高电平时读取数据,此时读取的为上一次转换的旧数据。

图4 AD7606时序仿真波形

1.2 DMA传输

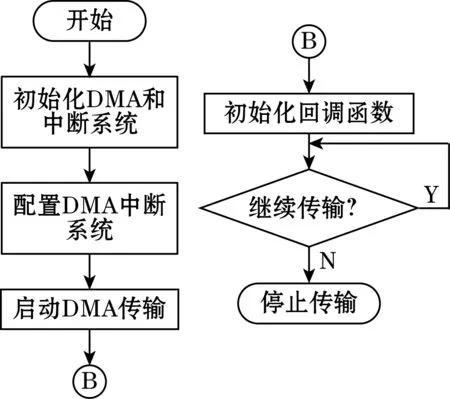

如何将PL端采集的数据传输到PS端是系统设计的关键部分。Zynq 内部 PS 和 PL 之间的接口包括AXI总线接口、EMIO接口、中断、DMA、时钟和调试接口[4]以及配置接口。其中,AXI 互联总线是 PS 与 PL进行数据传输的主要通道[5]。PS部分配置DMA中断系统,控制流程如图5所示。

为了方便PL与DDR进行高速数据交互,选择PS内部 AXI-HP接口以及DMA传输通道。DMA是一种快速数据交换技术,数据吞吐率达到1 200 MB/s,满足实时数据处理中高速传输的要求[6]。

图5 DMA传输流程

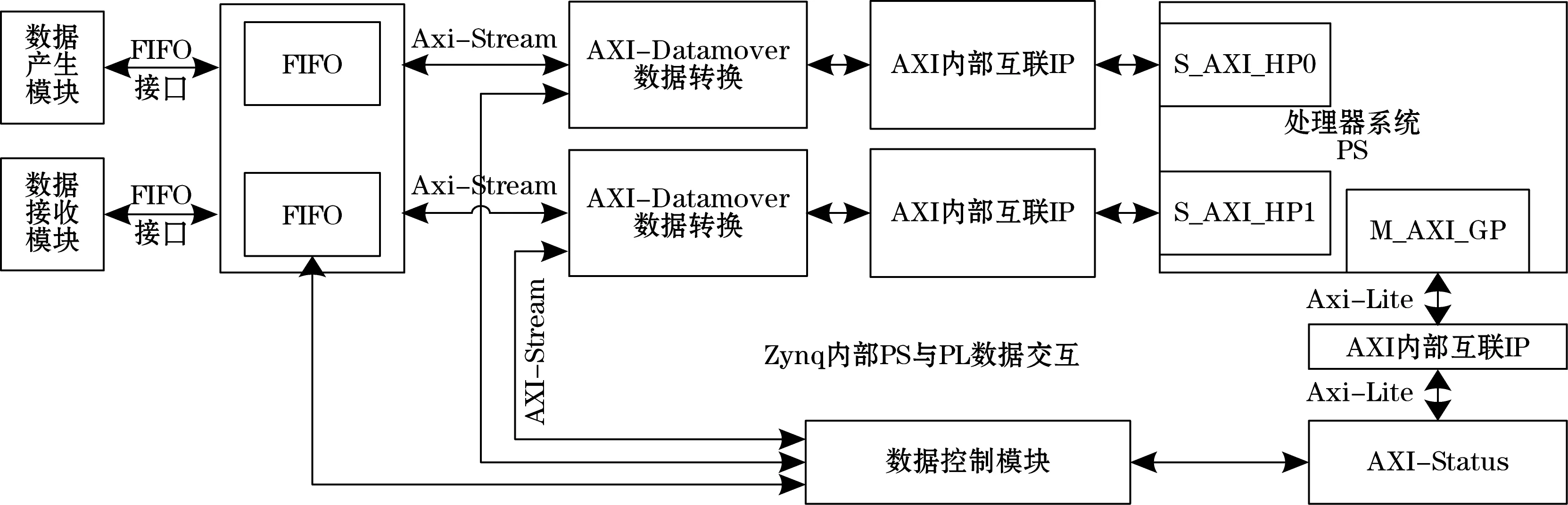

由于控制命令传输部分对数据量及数据吞吐率要求不高,所以选择AXI-GP 接口,通过 AXI-Lite总线连接到PL其他外设接口,由 PS 向外发送控制信息;AXI-HP0和AXI-HP1分别连接2个数据传输通路。这样能够将各模块的数据传输效率发挥到最大,保证PS与PL之间数据传输更加高效[7]。PS与PL数据交互框图如图6所示。

图6 PS与PL数据交互框图

1.3 FFT变换

FFT(快速傅里叶变换),是离散傅里叶变换的快速算法[8]。系统采用 FFT IP 核进行FFT变换,处理器负责接收DMA传输的数据并控制PL部分的FFT模块,FFT与DMA之间的数据传输符合AXI-Stream流传输。使用IP核可以选择占用不同的底层资源,提高可编程逻辑资源的利用率,使Zynq资源利用与速度达到最优。

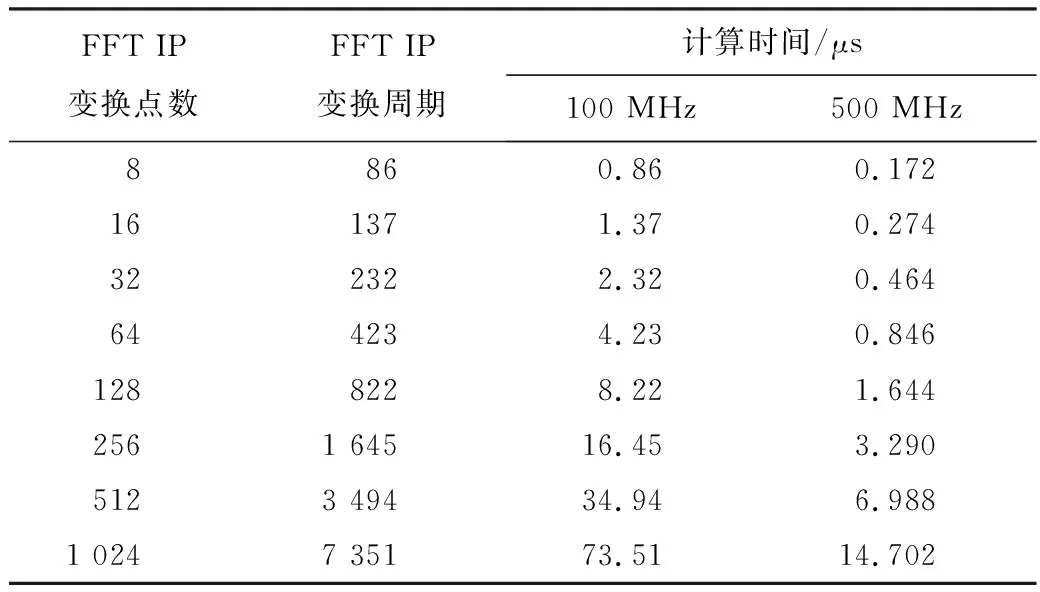

FFT IP核最大可工作在500 MHz频率下,100、500 MHz工作频率下不同点数对应的处理速度如表1所示。

表1 不同点数与延迟时间对比表

为了验证 FFT 这个模块的设计结果是否正确,首先对采样的位宽为16 bit 的1 024个数据点进行FFT变换。调用IP核,采用Radix-2,BurstI/O结构,输出数据精度由相位因子决定,相位因子选择16 bit,占用6个DSP48,5个块RAM。在100 MHz的工作频率下,变换周期为7 351,延迟时间为73 μs,数据吞吐率为50 Msps。

2 系统测试与结果分析

2.1 数据采集

采集到的振动波形近似正弦波,由于信号带来的杂波比较多,所以示波器测量的幅值和频率不准。数据采集模块对振动信号进行滤波、放大,把信号调理到AD7606的输入电压范围,再进行低通抗混叠滤波,如图7所示,波形频率为2 kHz,幅值为3 V。

图7 滤波放大后的振动信号

启动SDK,连接串口,设置网络IP地址,以及网络端口号,由网络调试助手发送启动传输命令,数据开始传输。信号通过数据采集板完成模数转换过程,再通过 FEP高速扩展接口连接至主控板,添加ILA(在线调试工具),以模拟波形的形式观察通道ad_ch1和ad_ch2,时域波形如图8所示。

图8 采集的2路振动信号

由图8可知,经过调理后的信号呈现正弦波,没有噪声干扰,并且未出现信号失真等问题,证明了A/D采集转换电路设计合理,芯片正常工作。

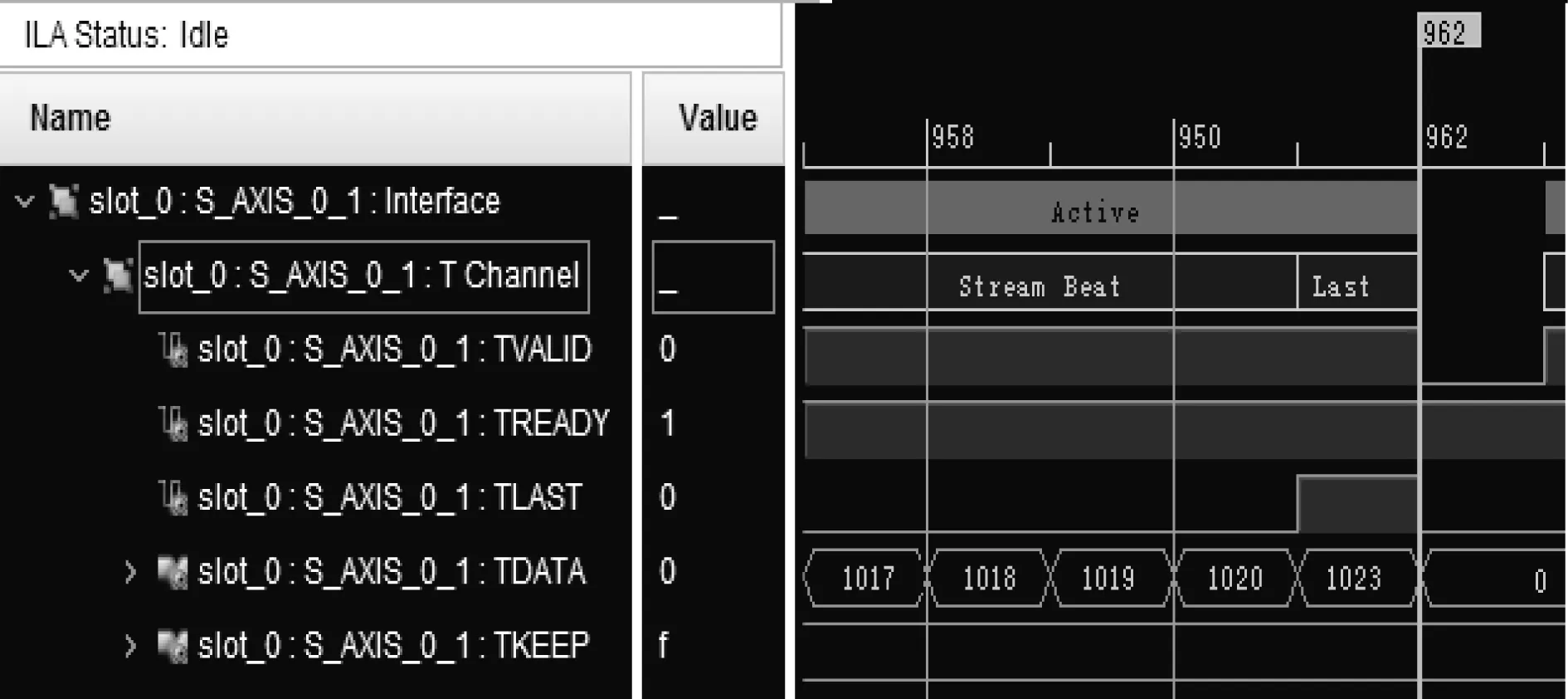

2.2 AXIS协议仿真

主控板PL部分利用一个异步FIFO完成跨时钟域的数据传输。通过在AXIS总线添加System ILA IP核,可以观测PL接收端AXIS-Stream流数据[9],仿真波形如图9所示。

图9 AXIS-Stream 流数据仿真

由图9可知,AXI4协议是通过数据发送端TVALID信号和数据接收端TREADY信号之间的握手协议来传输数据的。本设计中保持TVALID信号有效,当TREADY为高电平时(图9中TREADY一直为高电平)表示PL准备好接收数据,在二者均有效时主从设备之间进行数据通信[10]。

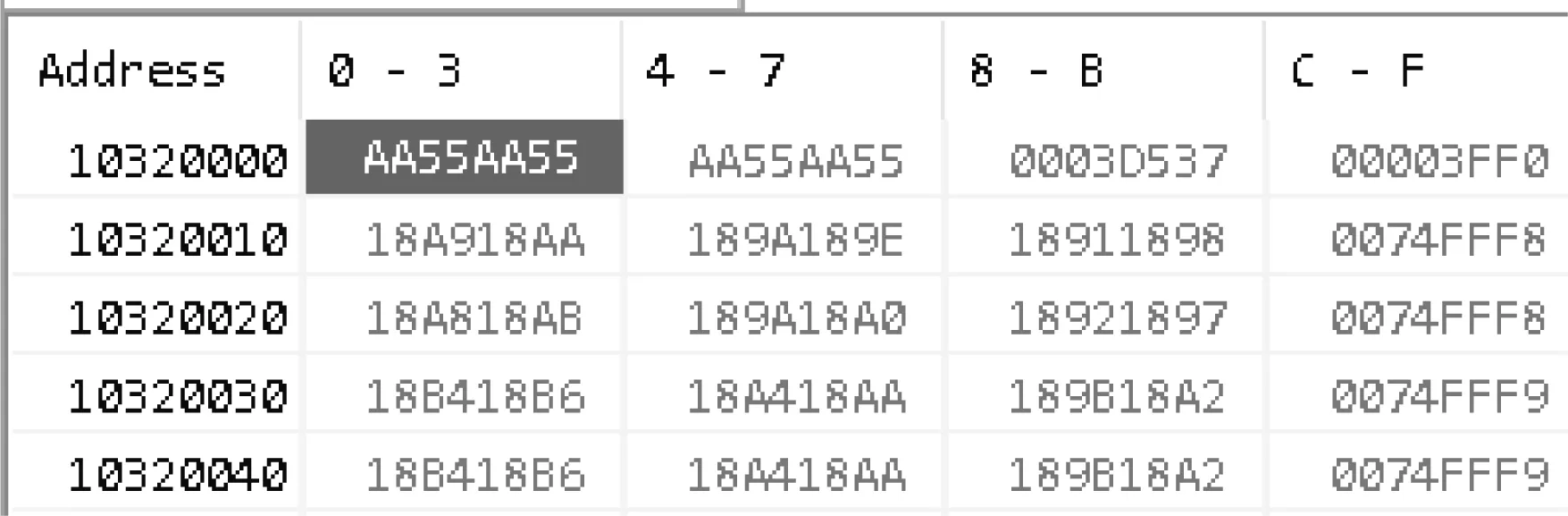

在SDK调试界面可以添加内存地址来查询相应地址处的数据。添加写(读)内存初始地址0x1032(0)0000,如图10和图11所示。写(读)内存地址0x1032(0)0000~0x1032(0)0007处8字节数据为包头,代表数据包开始。0x1032(0)0008~0x1032(0)000B处4字节为包序列号。0x1032(0)000C~0x1032(0)000F处4字节为本包数据长度。0x1032(0)0010之后为A/D转换后的数据。

图10 查询写内存数据

图11 查询读内存数据

2.3 FFT变换及分析

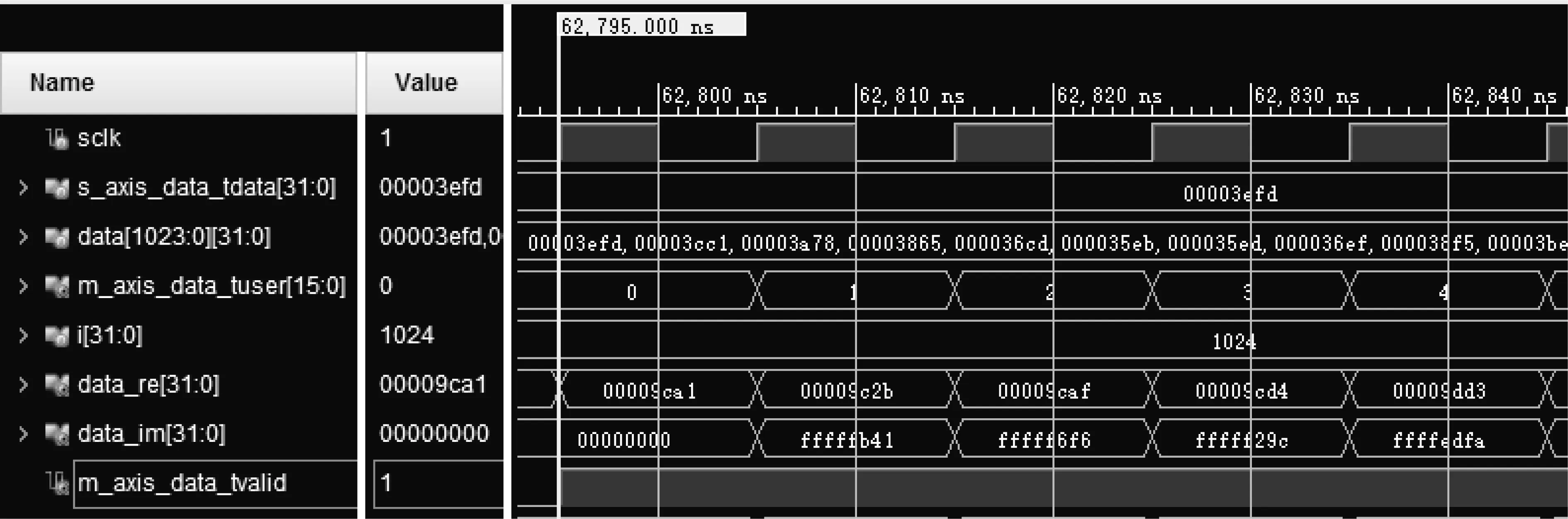

100 MHz工作频率下,对16 bit 数据进行1 024点FFT 变换,仿真结果如图12所示。IP核输入端口s_axis_data_tdata为原始数据,变量i表示1 024个数据;FFT核处理结果为复数,输出端口m_ax- is_data_tdata位宽为64 bit,其中高32位为虚部,低32位为实部,分别对应信号data_im、data_re。将复数实部虚部结果导入MATLAB进行频谱图绘制,并与MATLAB计算的FFT结果相比较,如图13所示。

图12 FFT IP核仿真波形

(b)MATLAB FFT处理结果

由图13可知,信号主要频率为2 kHz,幅度为3 V,2 kHz以外的信号基本没有。IP核处理结果与MATLAB处理结果一致,实际应用工程中,可根据需要对FFT变换点数进行调整。

3 结束语

设计了一种以Zynq-7000 SOC芯片为核心的数据采集及频谱分析系统,由振动传感器采集振动信号,进行信号调理后通过A/D转换芯片说明了振动信号采集的正确性,通过验证PL与PS之间的DMA通信、AXI4协议,设计达到了高的吞吐率,采用官方IP核进行了1 024点FFT变换,精度速度满足系统要求;根据频谱特征可得知机械振动并无故障。