多通道高速信号采集器

渐 欢,全大英,侯晓宇,范 威,金小萍

(中国计量大学信息工程学院,浙江省电磁波信息技术与计量检测重点实验室,浙江杭州 310018)

0 引言

在通信、雷达、导航、环境监测等信号处理的相关研发、生产和测试场合,除了直观查看信号的时域波形和频域频谱并测试基本的参数之外,通常需要记录信号的原始波形。部分高端的示波器和频谱仪具备这种能力,但是往往存在实时性不足造成需要对采集的信号降采样率后才能存储,并且存储空间有限,在采样率较高时,无法采样足够时长的数据。而专门为某一项目设计的采集模拟器往往功能比较复杂,并且针对项目设计,缺乏良好的通用性。

一般而言,多通道高速信号采集器主要指标有采样频率、采样精度、幅相一致性和有效存储容量等。采样频率和采样精度多与ADC芯片的架构、硬件设计、数据接口设计和软件算法有关[1]。近年来,ADC芯片性能随着设计技术和工艺水平的不断提升而得到长足发展,数Gsps采样率的高速高精度ADC不断得到商用。采样速率的提高造成了获得的数据速率不断提高。以往采样数据的传输方式多采用如低压差分信号(low-voltage differential signaling,LVDS)传输等并行方式,其接口速率最高只有2 Gbps左右,且容易出现时钟同步困难、串行干扰大、PCB布线复杂等问题[2],无法满足当前高速ADC发展需求。而采用基于JESD204B标准协议的高速串行接口能有效解决这些问题。JESD204B标准协议是JESD204协议的第三个版本,每通道采样速率最大12.5 Gbps,支持确定性延迟和谐波时钟,是单向点对点的高速串行协议[3-4]。该接口简化了系统设计,使得PCB布局布线更轻松,减少了芯片引脚数量,降低总体成本[5],且JESD204B可以实现转换器与FPGA之间的通道同步[6]。

幅相一致性是多通道采集器的另一个重要指标,也是设计难点之一,不仅需要硬件设计保证,软件设计也尤为重要。在高速大带宽信号采样中,幅相一致性显得更加重要。需要在设计中采用最新的信号和时钟缓冲器件,采取必要的校准措施,并且更加关注信号完整性设计。

此外,多通道采集器的实时存储设计多采用FPGA作高速缓存。在采样率较低且采样数据带宽较小情况下,许多信号采样系统都是将信号采集后直接发送至上位机,进行存储和计算[7],采集系统的有效存储空间与主机硬盘大小有关。这种设计方案有一定局限性,在高采样率情况下,采样数据带宽大,但是采集系统与上位机之间的数据传输速度较慢,无法将采集的数据实时传输至上位机。因此需要通过设计高速数据缓存模块,实现采集数据的实时存储,采集系统的有效存储空间通常与高速缓存模块存储空间大小有关。

针对传统信号采样系统的不足,本文采用基于JESD204B标准接口的高性能ADC器件完成高达2.5 GSps采样率的多通道信号采样,配合高性能的FPGA和DSP,实现了一种多通道同步采集系统,该系统能够实时记录高速模拟信号,记录的数据通过以太网接口传输到上位机完成进一步的测试和分析工作。

1 总体架构

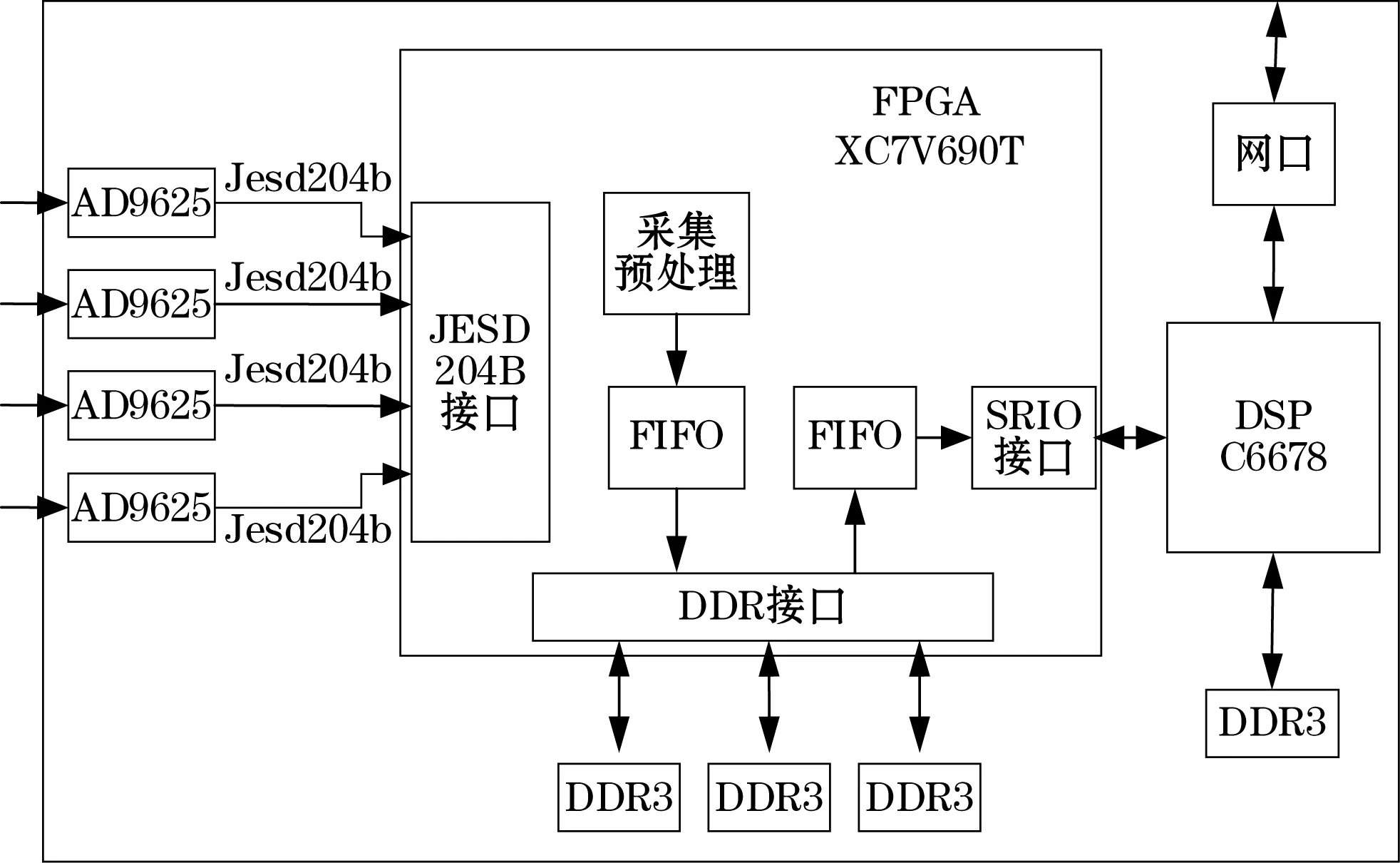

多通道高速信号采集器总体架构如图1所示。

图1 采集器总体架构

如图1所示的高速信号采集器由4部分组成,多通道高速ADC、数据预处理、实时存储、控制和数据导出。其中,高速ADC完成模拟数字转换,前级输入的信号可以是雷达和通信的射频信号或者中频信号,信号和采样率的关系应该满足Nyquist采样定理或者带通采样定理。ADC采集的数据完成串并转换以适合并行传输和处理,完成预处理的数据将被实时存储到DDR存储器。上述工作在控制和数据导出模块的控制下工作,一旦数据存储完毕,即可以通过千兆以太网导出到外部主机。

多通道ADC设计时,不仅对于ADC的ENOB(有效位数)、动态范围、输入信号带宽等性能有要求,而且还要提供良好的ADC的多通道一致性。数据预处理主要完成数据的打包以方便存储和传输。此外数据打包功能主要完成四通道数据的拼接,同时在采集数据起始端加入数据头标识,在一个数据脉冲结束时加入数据尾标识,以实现一个简单的传输协议。所设计多通道高速信号采集器作为便携式采集设备,不提供非易失性存储功能。最后采用DSP作为上位机命令的解析和采集的控制管理模块。数据导出时,DSP通过外挂DDR进行数据传输的暂存,最终数据通过千兆以太网传输到上位机。

2 硬件设计

基于所设计的总体架构,采用最新的ADC、FPGA、DSP等器件,设计多通道高速信号采集器硬件平台。

2.1 硬件实现总体框图

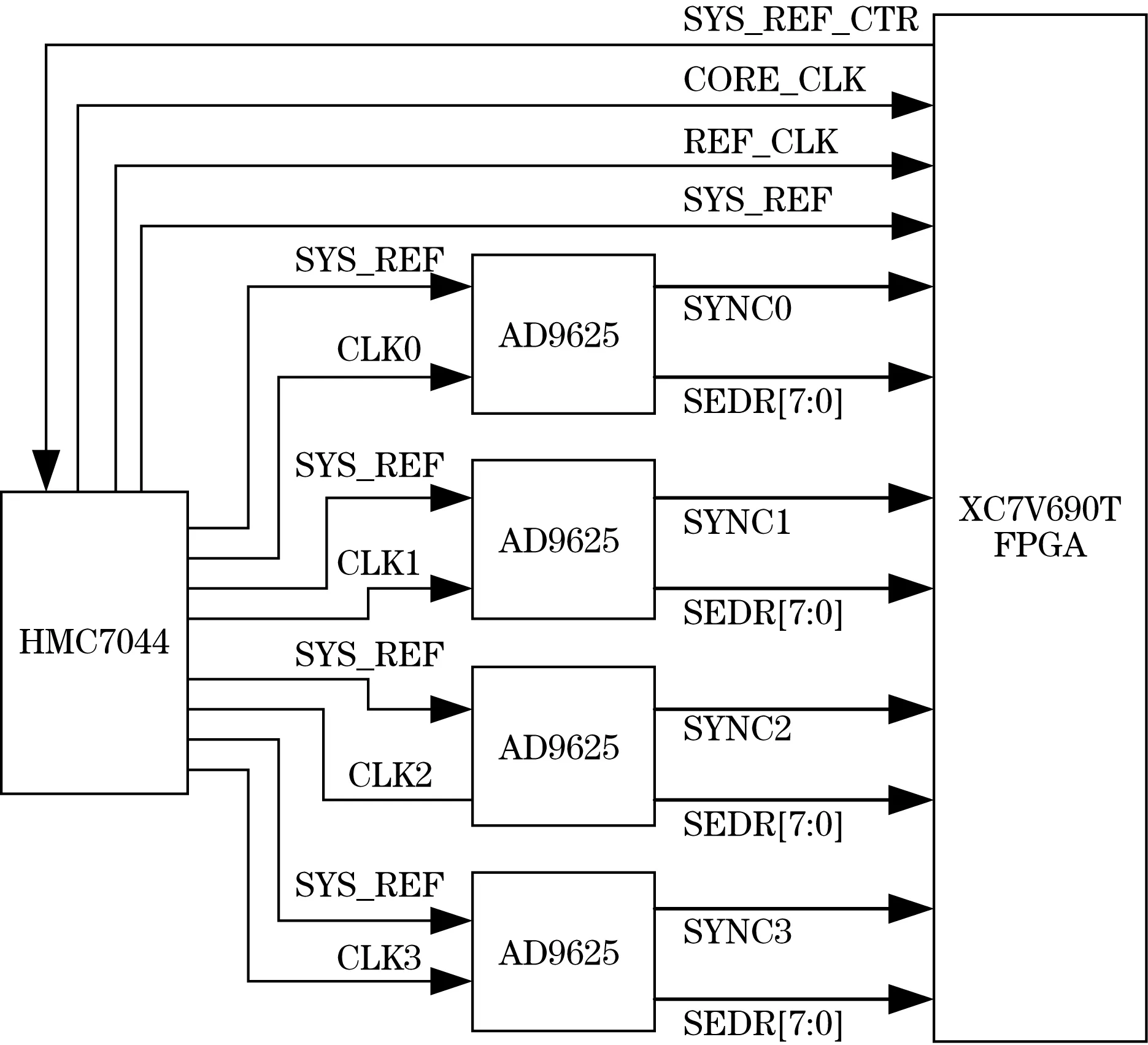

硬件实现总体框图如图2所示。

图2 硬件实现总体框图

所设计硬件主要包含3个部分,4片ADC芯片AD9625完成多通道采样、Virtex-7系列FPGA XC7V690T和TMS320C6678 DSP完成数据预处理、实时处理和传输。FPGA外挂3组DDR,每组DDR大小2 GByte;DSP外挂一组DDR,大小为2 GByte。DSP通过千兆以太网与上位机通信,完成控制命令和数据的交互。

采集器的工作流程为:四通道AD9625并行采集输入的信号,采集得到的数字信号通过JESD204B接口传输至FPGA,FPGA完成数据的预处理与数据缓存,最终经DSP通过网口将数据传输至主机。

2.2 多通道同步信号采集电路

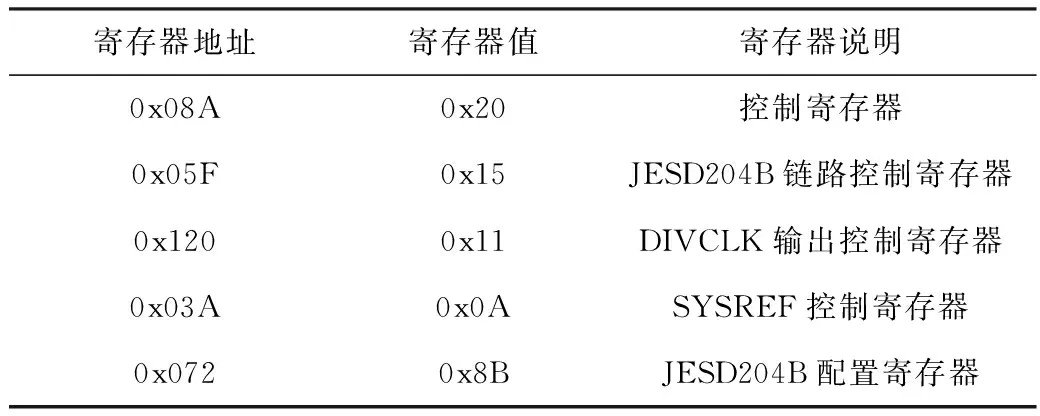

多通道同步信号采集采用4片AD9625实现。AD9625提供高性能模数转换器(ADC),该芯片量化位数12 bit,采样率高达2.5 Gbps,差分模拟输入电平为1.1 V,支持3.2 GHz全功率模拟输入带宽[8]。多通道同步采集电路设计框图如图3所示。

图3 多通道同步采集电路设计框图

AD9625采用符合JESD204B标准的数据接口,以节省FPGA的I/O资源并提高数据传输速率。

多通道同步设计基于JESD204B的多片同步机制。在设计中,通过HMC7044提供的时钟网络配合JESD204B接收器的确定性延时同步设计,实现多片同步:

(1)HMC7044输出4路时钟,时钟频率为2.5 GHz,分别送往4片AD9625实现器件时钟的相位对准,相位误差最大为30 ps;

(2)在FPGA内部的JESD204B接收器中选择适当的弹性缓冲器释放点(elastic buffer release points)以保证确定性延迟。确定性延迟指的是从串行数据发送端的并行帧数据输入至接收端并行解帧所需的时间[9]。AD9625和FPGA之间由SYNC信号和SYSREF信号共同完成并确定多帧时钟边沿。其中SYSREF信号由FPGA控制HMC7044产生,以保证多帧时钟边沿同步产生。

(3)通过电路走线等长设计,确保各AD9625到FPGA的SYNC信号满足定时要求,芯片间等长布线设计由硬件设计保证,布线误差小于2 mm,工程上PCB传输线上信号的传输速度按照光速的80%计算,则最大延迟误差小于8.3 ps。FPGA内部布线导致的延迟误差一般为时钟周期的整数倍,约为ns级延迟,其可以通过对相关时钟信号进行约束,以达到布线等长设计。

在该同步机制下,可保证四通道之间同步误差最大约38 ps。

2.3 数据实时存储电路

本文设计的采集器为了满足雷达和通信的信号采集需求,需要以最高2.5 Gsps采样率采集信号。实时数据带宽高达160 Gbps。采用3组共6 GByte的DDRIII SDRAM,在最高采样率下工作可以存储的数据长度为0.3 s。若采样率降至1 Gbps,则可以存储的数据长度为0.75 s,能够满足大部分的宽带通信和雷达研发、调试和测试的需求。

DDRIII工作在1 200 MHz的双沿采样,数据位宽为64位,因此其理论数据吞吐率最大为102.4 Gbps,3组DDR同时读写速度为307.2 Gbps,远高于实时采集的数据速率,因此能够实现数据原始采样率实时存储。

2.4 数据传输和导出电路

数据传输和数据导出电路架构如图4所示。

图4 数据传输和数据导出电路设计架构

在图4中,FPGA与DSP之间SRIO接口采用4X模式,链路速率5 Gbps,则SRIO接口理论传输速率为16 Gbps,以太网理论传输速率为1 000Mbps,均远小于ADC接口最大传输速率160 Gbps。综合上述据,由于FPGA与DSP、DSP与上位机之间数据传输速率较慢,无法将采集数据及时导出,因此该系统设计满足采集数据实时存储要求,但无法满足采集数据实时搬移要求。

3 软件设计

软件设计主要由上位机、DSP和FPGA 3个部分组成,上位机软件包括采集界面设计、采集参数寄存器配置、采集文件导出和设备工作状态显示。上位机每次采集开始前先发送软复位命令寄存器,用于清空FPGA端FIFO存储的数据,初始化数据传输控制状态机,最后进入设备工作就绪状态。上位机运行于PC机Windows环境,由于采用以太网通信,上位机对PC机硬件没有特殊要求。FPGA逻辑设计包含ADC接口设计、SRIO接口设计、DDR接口设计、数据预处理设计等,DSP软件设计主要包括控制命令转发和数据转发两部分。

3.1 ADC接口配置及同步设计

ADC接口采用JESD204B协议标准接口,设置JESD204B接口参数:链路通道数(L)为8,帧字节个数(F)为1,多帧帧数(M)为32,链路速率(line rate)为6.25 Gbps,参考时钟625 MHz,动态重配置端口(dynamic reconfiguration port,DRP)时钟为100 MHz。则核时钟(CORE_CLK)速率为

(1)

根据AD9625芯片手册,产生相关寄存器配置清单,主要寄存器配置列表如表1所示。

表1 AD9625主要寄存器配置列表

表1中,寄存器地址0x03A表示配置SYSREF信号为连续模式,下降沿有效;寄存器地址0x72表示配置JESD204B为8通道工作模式。

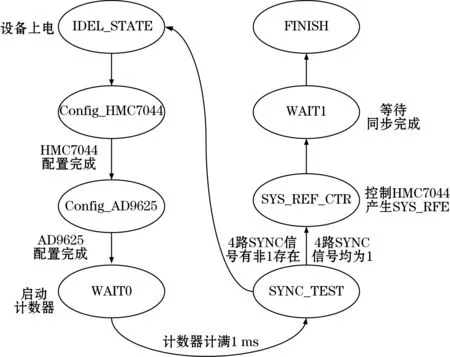

根据时钟设计需求,设计HMC7044相关寄存器列表。在设备上电后,通过HMC7044的SPI接口,完成时钟芯片配置。在HMC7044配置完成后,通过AD9625的SPI接口完成ADC芯片配置,然后开始同步校验。该配置过程状态机设计如图5所示。

图5 JESD204B配置同步状态机

图5中,在HMC7044配置完成之后,开始AD9625配置,配置完成后等待1 ms,然后跳入SYNC_TEST状态,检测4片AD9625的SYNC信号是否置高,若任意路未置高,则回到IDEL_STATE状态开始重新配置。

SNHB物流中心拥有自己研发先进的分拨超级系统完全脱离、独立,同时整个系统能够管理和检测到每个包裹从发货到包裹签收的整个流程,提供强大的决策支持。

3.2 数据预处理设计

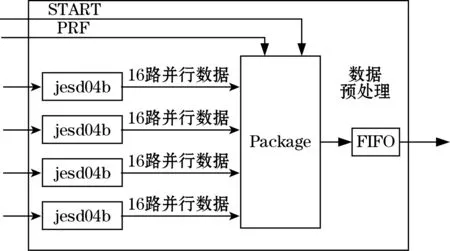

数据预处理主要完成数据的打包功能,具体设计框图如图6所示。

图6 数据预处理设计框图

图6中,每通道ADC有16路数据并行输入,根据PRF触发信号和START信号在Package模块中完成数据的打包,即在脉冲头和脉冲尾加入数据头标识和数据尾标识,以记录采集脉冲的脉宽和周期参数,在连续采集模式下则只需要加入数据头标识。其中PRF触发信号指脉冲信号采集模式时的采集触发信号,PRF上升沿指示当前脉冲采集的起始时刻,下降沿指示当前脉冲采集的结束时刻。最后将封装好的数据写入FIFO,方便DDR进行数据的存储。

3.3 实时存储设计

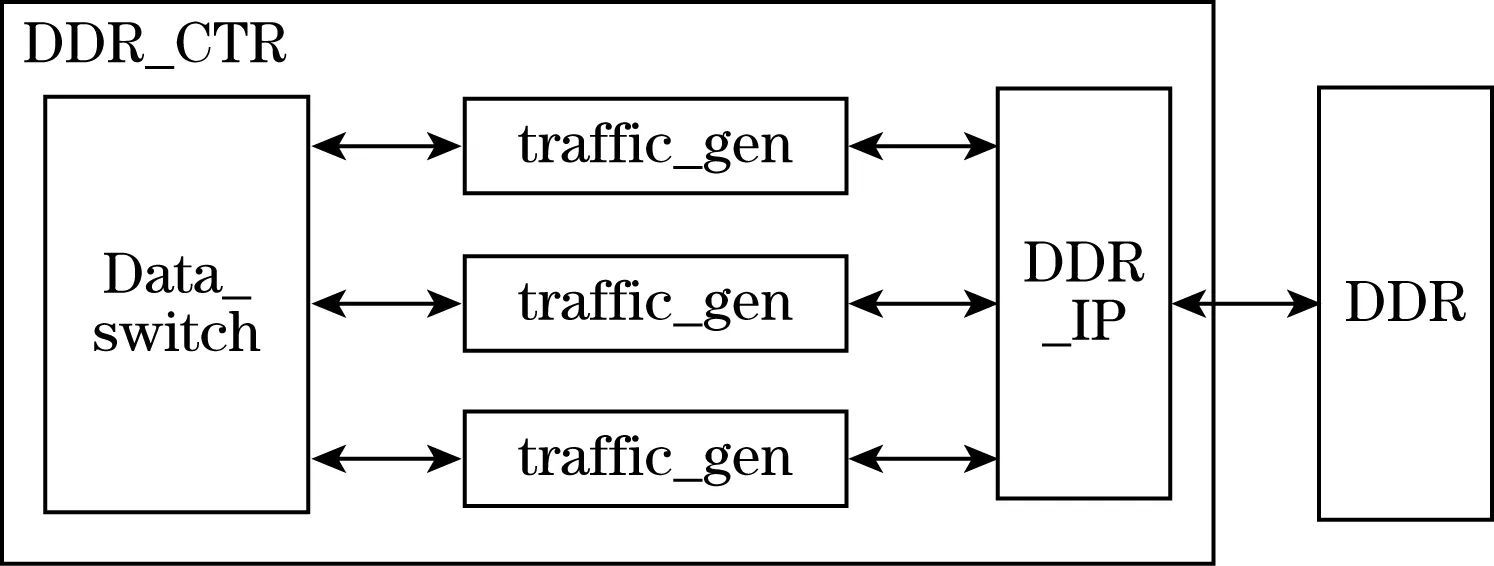

通过实际测试,所设计的单组DDR驱动写速度为81.9 Gbps,约为理论传输速度的80%。四通道采集数据传输速度最大为160 Gbps,若进行单组DDR写操作,则无法满足实时存储要求。由于四通道采集数据有效位宽为1 024 bit,DDR驱动接口用户位宽为512 bit,若3组DDR同时进行写操作,则数据无法同时均分至3组DDR,导致DDR存储空间浪费。因此通过FIFO缓存设计,进行分时写操作,可有效实现存储空间利用以及实时存储需求。其总体设计框图如图7所示。

图7 DDR接口软件设计

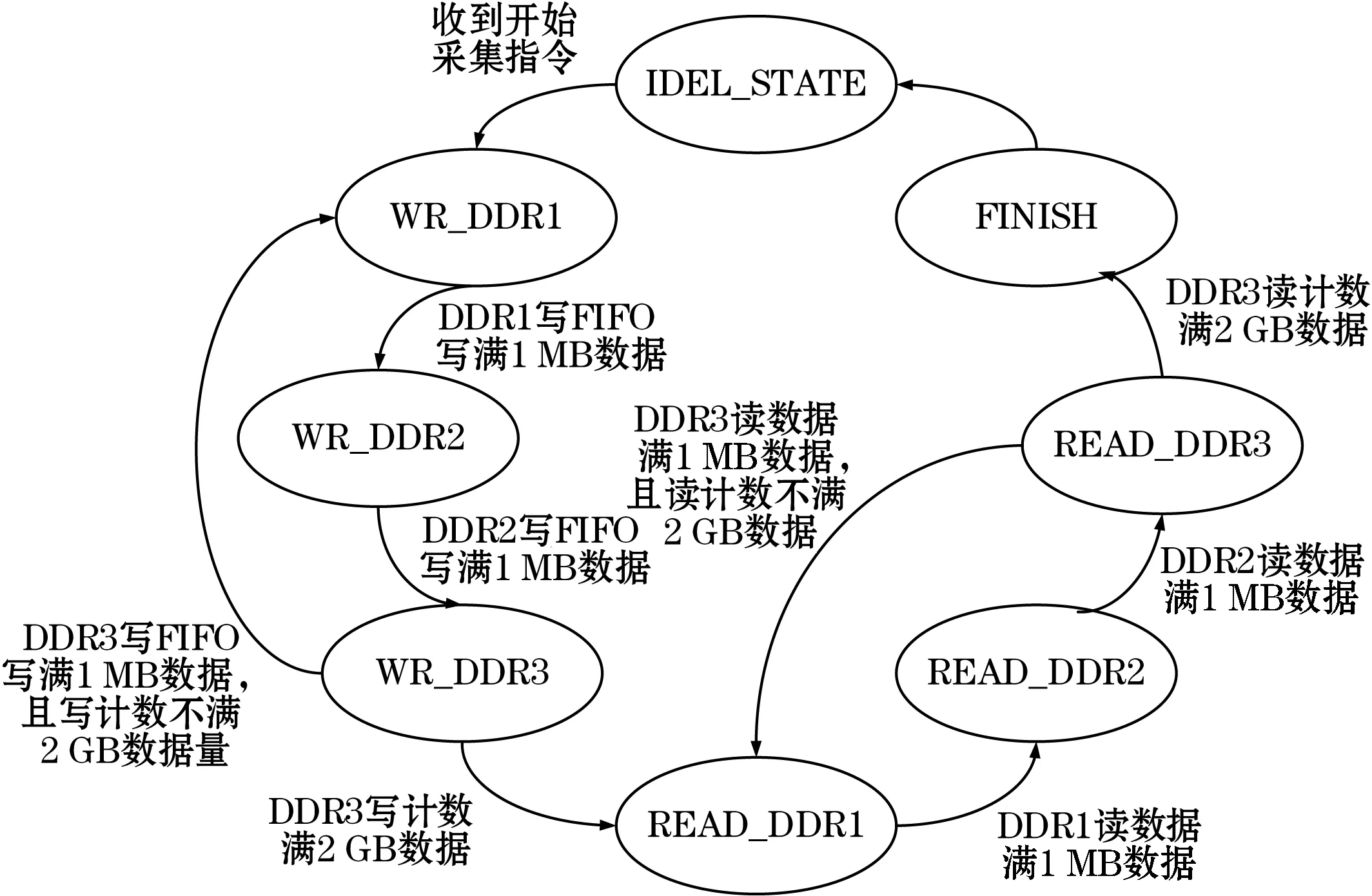

图7中,traffic_gen模块主要根据读写命令产生DDR读写时序进行读写操作。Data_switch模块主要进行数据传输控制,包括采集数据分发至3组DDR,以及控制从3组DDR中读取数据,其状态机设计如图8所示。

图8 DDR读写控制状态机

设计Nblock=1 MByte大小的数据分段轮流分发数据到各组DDR。假设以最大采样率fsmax=2.5 Gbps采集数据,则四通道采集1 MByte数据量耗时Ts,1M=Nblock/(fsmax×16×4)≈50 μs。由于采样速率比单组DDR写速率高,因此需要采用FIFO缓存数据。设计DDR写FIFO位宽为1 024 bit,则需要FIFO深度大小为

(2)

式中:LFIFO为FIFO深度;rddr_wr为DDR实际写速率, Gbps。

由于3组DDR轮流写入,因此每个FIFO写入间隔为3Ts,1M≈150 μs,远大于DDR写入1 MByte数据的时间Twr,1M=Nblock/rddr_wr≈98 μs。因此根据FIFO设置深度选项,设置3组DDR写FIFO深度为4 096,能够满足实时存储需求。由于DDR读取速率远大于SRIO数据传输速度,设计DDR读FIFO位宽为1 024 bit,深度64即可满足SRIO数据传输需求,其中DDR读控制由DDR读FIFO的几乎满标志控制,防止FIFO写满。

3.4 FPGA与DSP数据传输设计

图9 FPGA端SRIO接口数据传输流程

如图9所示,DSP每次请求数据前发送数据请求命令,FPGA收到数据请求后开始传输1 MByte数据量,数据每次传输完成后发送Doorbell(门铃)中断指令,通知DSP数据发送完成,FPGA然后等待下一次数据请求。

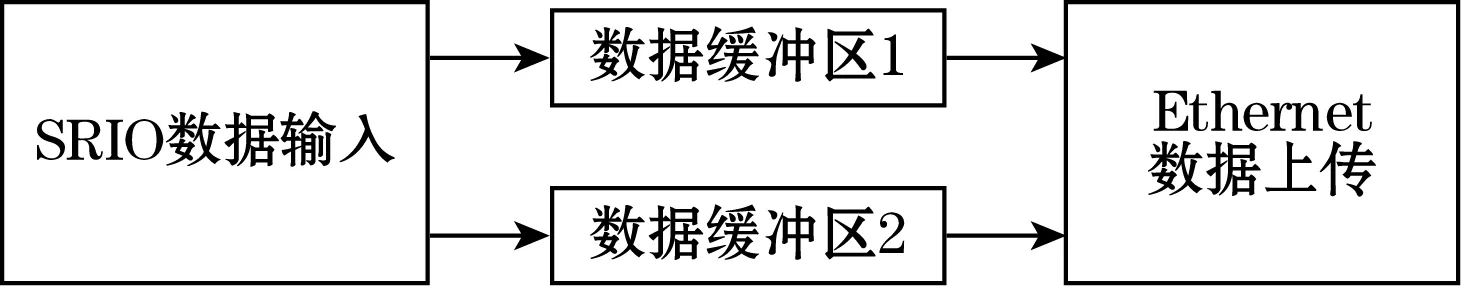

DSP软件设计由命令转发部分和数据转发部分组成,DSP和上位机之间通过千兆以太网通信。在运行状态下,DSP通过以太网接收来自上位机的控制指令,解析后将命令通过SRIO接口发送到FPGA。DSP端SRIO接口接收到采集数据后,通过乒乓方式将数据通过以太网转发给上位机。

乒乓转发如图10所示,首先SRIO将数据缓冲区1和数据缓冲区2填满,然后通过以太网将数据缓冲区1中的数据上传。接着,当SRIO将数据传入缓冲区1的同时以太网将数据缓冲区2中的数据上传。随后,当SRIO将数据传入缓冲区2的同时以太网将数据缓冲区1中的数据上传。如此往复,便可实现乒乓操作。

图10 DSP端SRIO乒乓缓存设计

4 实验和分析

所设计的多通道高速信号采集器板卡实物原型如图11所示。

图11 高通道信号采集器原型实物

该原型包含4个SMA输入信号接口以及必要的参考时钟和采样时钟输入接口,并且对外的控制和数据接口为千兆以太网。

4.1 采集功能测试

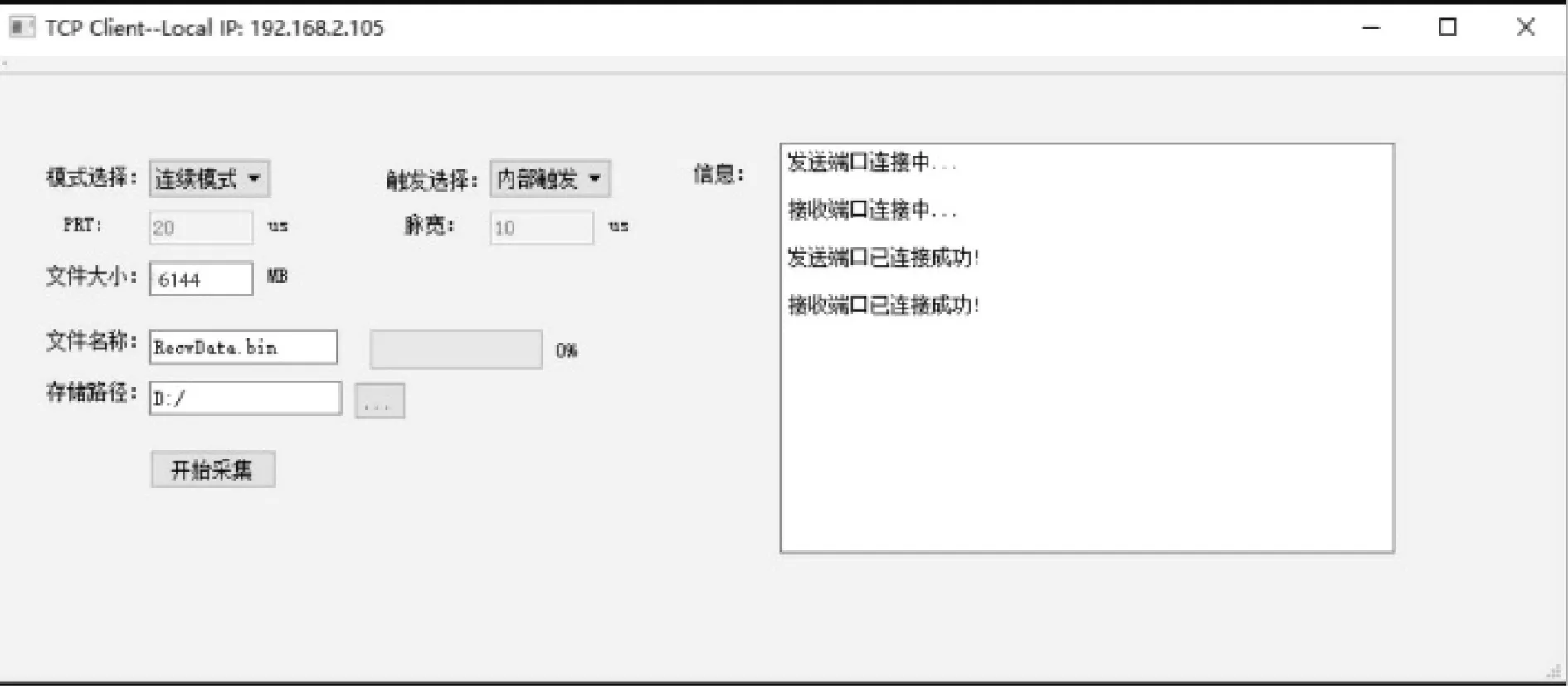

图11所示的信号采集器原型通过以太网连接到上位机,并且连接必要的时钟信号、触发信号和ADC输入信号。在如图12所示的上位机数据采集界面完成工作模式配置,并且配置文件为6 GByte。点击开始采集。

图12 上位机界面

测试结果显示,可连续采集6 GByte数据,采集数据通过MATLAB分析,采集波形正确。

4.2 多通道幅相一致性测试

使用信号源SMA100A,提供0~7 dBm的2.5 Gbps采样时钟,并依次设置频率为1 300、1 800、2 300 MHz的采集信号,使用功分器分四路并行输入,每个采样频率进行10组采集实验,计算每通道正弦波相位以换算成时域延时,并相互作差得到通道间延迟。其中以第一通道为基准,如第二通道与第一通道之间的时间延迟为ΔT2-1,以此类推,记录每通道间延迟最大值,其测试结果如表2所示。

表2 多通道幅相一致性测试

表2测试结果表明通道间最大延迟为12.35 ps,通道间一致性较好。

4.3 四通道平坦度、ENOB、SNR测试

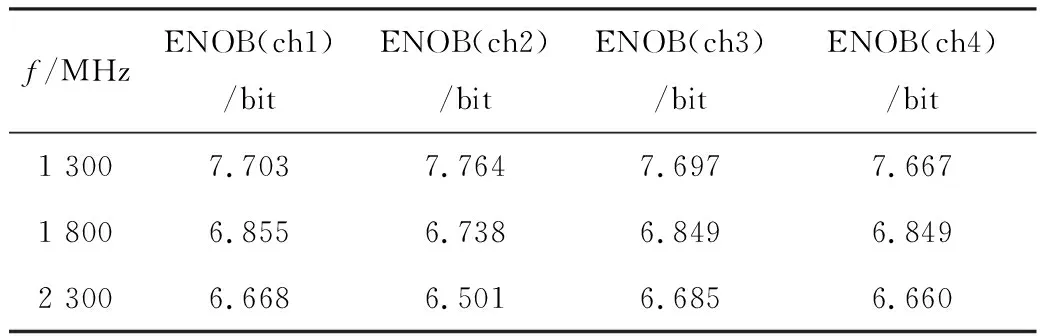

使用信号源SMA100A,提供0~7 dBm的2.5 Gbps采样时钟,并依次设置频率为1 300、1 800、2 300 MHz的采集信号,每个频点进行10次采集实验,计算每通道之间采集信号功率误差值、ENOB和SNR,其测试结果如表3、表4和表5所示。

表3 带内平坦度测试

表4 有效位(ENOB)测试

表5 信噪比(SNR)测试

由表3测试结果可以看出,通道4不同频点信号间最大功率误差值为1.295 dB,通道具有良好的带内平坦度。

由表4和表5可知,所设计的多通道采集器,随着采集频率的增加,数据有效位逐渐降低,在2 300 MHz采集频率下,有效位最小为6.501 bit,信噪比最小为41.05 dB。在对信噪比要求特别高的场合,需要针对电源和信号完整性做进一步优化。

5 结束语

本文采用新型的AD9625模数转换芯片实现了一种采样率高达2.5 Gsps的多通道信号采集器,借助FPGA的高速缓存特性,实现了最大6 GByte时域波形数据的实时存储。并通过实际测试,验证了多通道同步方案设计的可行性和良好的幅相一致性,以及数据采集的高可靠性。设备尺寸较小具备便携性等优点,同时其多通道同步设计方案具有较强的工程借鉴意义。