Camera Link图像数据接口的FPGA实现

甄国涌,何方城,单彦虎

(中北大学,仪器科学与动态测试教育部重点实验室,电子测试技术国家重点实验室,山西太原 030051 )

0 引言

随着工业相机等图像视频传输设备的不断发展,图像接口的传输效率与图像精度要求也越来越高,Camera Link标准接口可以为数字相机提供灵活可靠的连接,同时高速度和抗干扰的特点也使其在各个领域被广泛使用[1]。目前,图像传输接口在实际工程应用中通常会采用Camera Link专用转接芯片的形式,如DS90CR286等串并转换器,这样不仅传输速率会受到芯片限制,还会占用大量硬件空间和主控芯片的I/O口资源,不利于产品小型化和低成本的需求[2]。

本方案直接采用FPGA来实现Camera Link标准接口的图像数据接收,利用FPGA内部串并转换集成模块来替代专用转接芯片,使用FPGA原语,通过内部接口单元将LVDS图像数据解串为28位并行数据,数据编帧单元对有效信号进行编帧和处理后写入FIFO存储。传输速度可以达到110 MB/s,在提高了系统编码灵活性的同时,也有利于提升系统集成度[3]。

1 Camera Link接口原理与设计

1.1 Camera Link接口原理

Camera Link协议是针对数字相机的图像数据传输所提出的接口标准,总线接口包括图像、控制和串行通信信号,传输速度最高可达到2.386 Gbit/s,在工业领域中高速度应用、大数据量传输的背景下,Camera Link接口标准显得尤为重要。本设计中图像数据和时钟信号以低压差分(LVDS)的形式直接传输至FPGA内部进行解串,可以有效避免传输过程中的电磁干扰[4]。数据传输模式采用单倍速率传输的SDR模式,每个数据位的变化都在时钟高低电平变化时刻产生[5]。

1.2 FPGA的Camera Link接收端设计

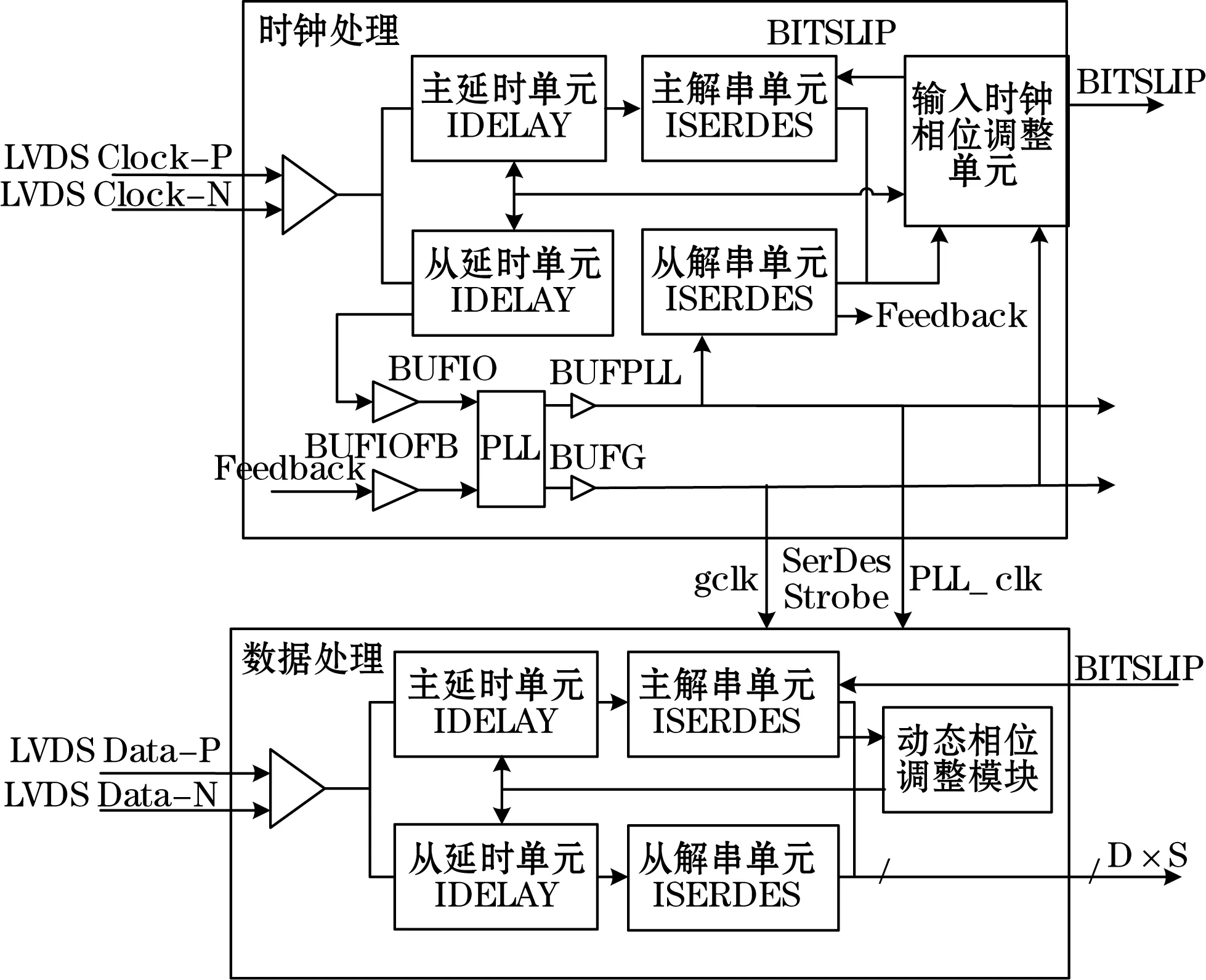

本方案采用Spartan-6系FPGA芯片,对IP核原语进行适当修改后,通过FPGA内部串并转换模块,实现了以Camera Link协议为标准的图像数据接收端口[6]。端口以4路LVDS图像数据和1路LVDS时钟信号进行接收,实现原理是通过FPGA内部的级联ISERDES(解串器)进行1∶7转换,得到28位并行信号。在LVDS数据接收时,为了提高传输效率,Camera Link接口的数据要进行相位对齐:输入延时单元IODELAY是通过对数据采样时钟PLL_clk进行一定频率的延迟,利用动态时钟、数据相位调整单元,来保证时钟采样点位于输入数据窗口的中间,以达到时钟与数据同步传输,从而确保了大批量数据可持续正确接收[7]。输入时钟信号通过IODELAY进行延时,经过相位调整模块,所产生的Bitslip子模块对ISERDES模块中的并行数据重新排序,以便将解串器所接收重复串行模式的每种组合都送至FPGA内部逻辑,可以有效避免数据丢失。其原理构架如图1所示。

图1 FPGA内部原理构架

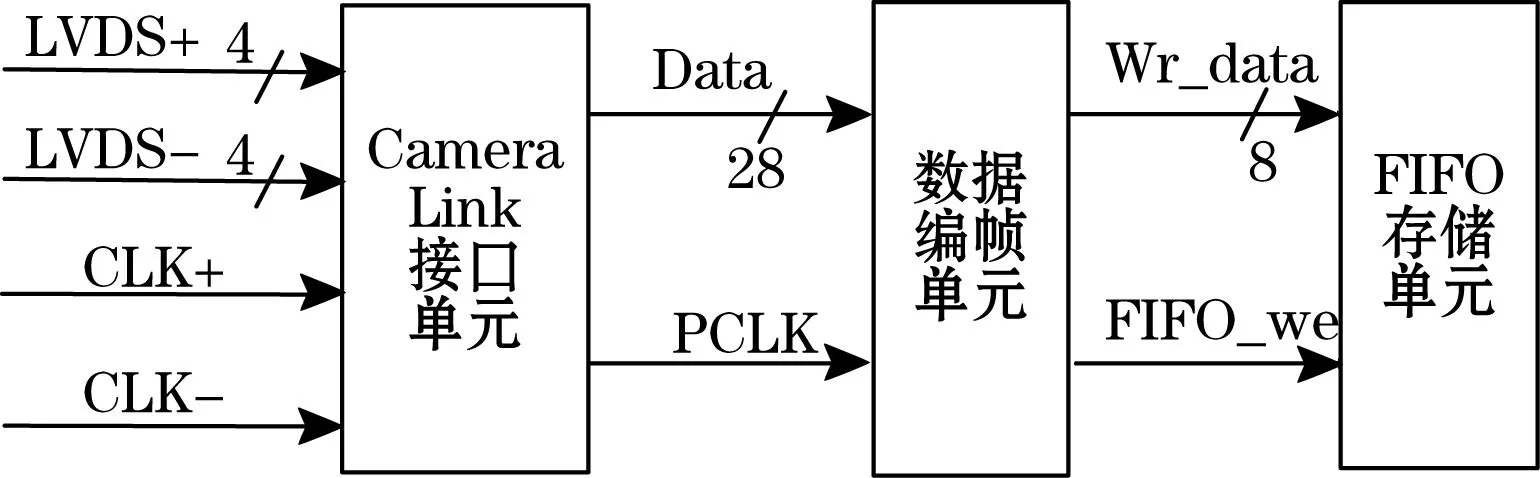

2 逻辑设计

在不使用专用转接芯片时,本方案的接收端逻辑设计如下:LVDS数据码流直接以FPGA I/O口进行输入,通过内部接口单元,转为28位并行数据和时钟信号PCLK,在经过数据编帧单元处理后,以FIFO使能信号FIFO_we为控制,将8位有效数据以固定帧结构写入FIFO缓存。具体实现流程框图如图2所示。

图2 总流程框图

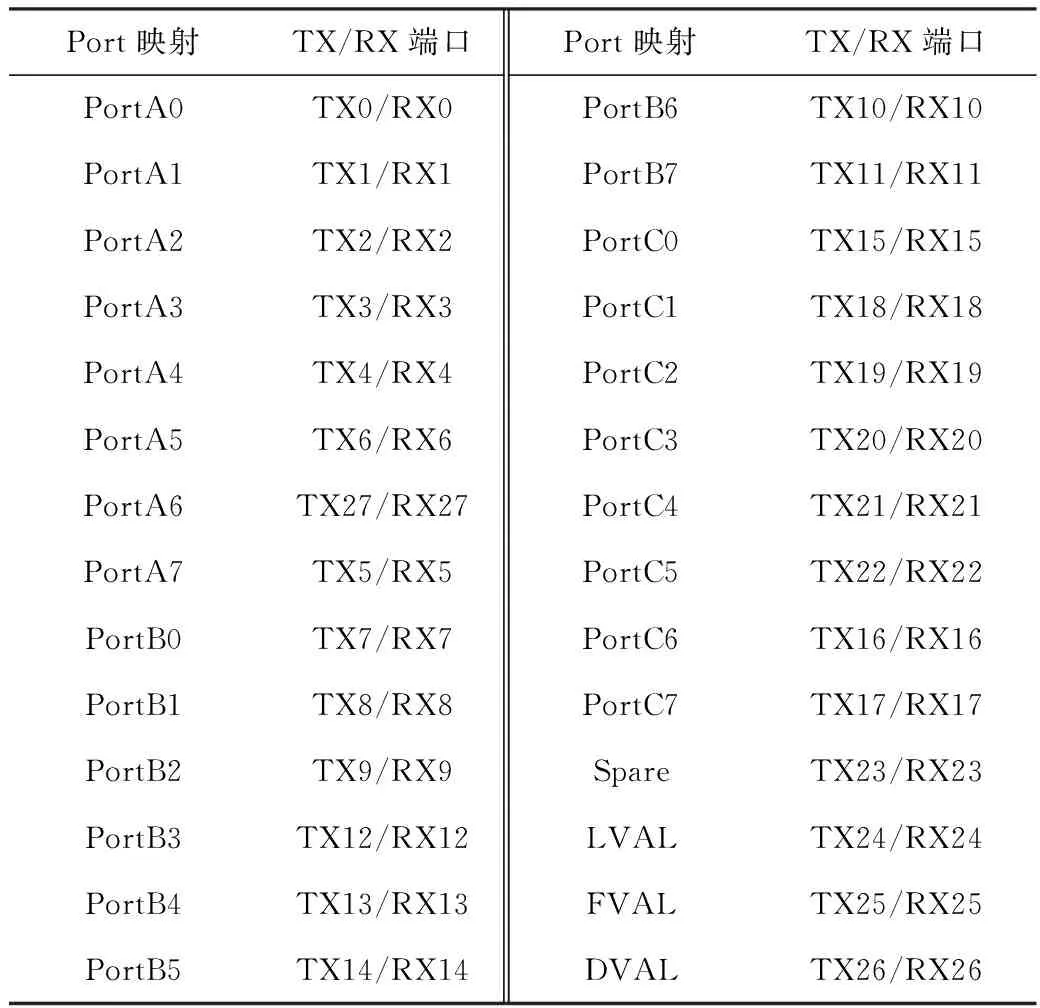

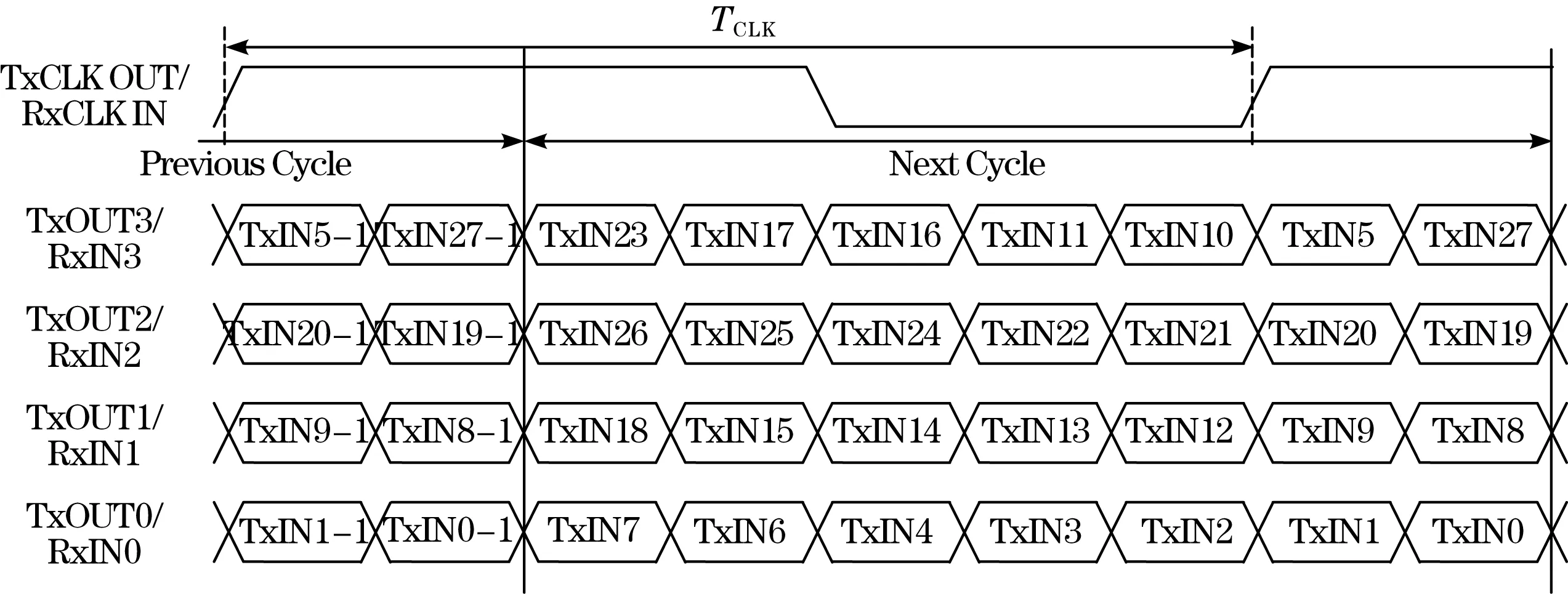

2.1 Camera Link端口映射

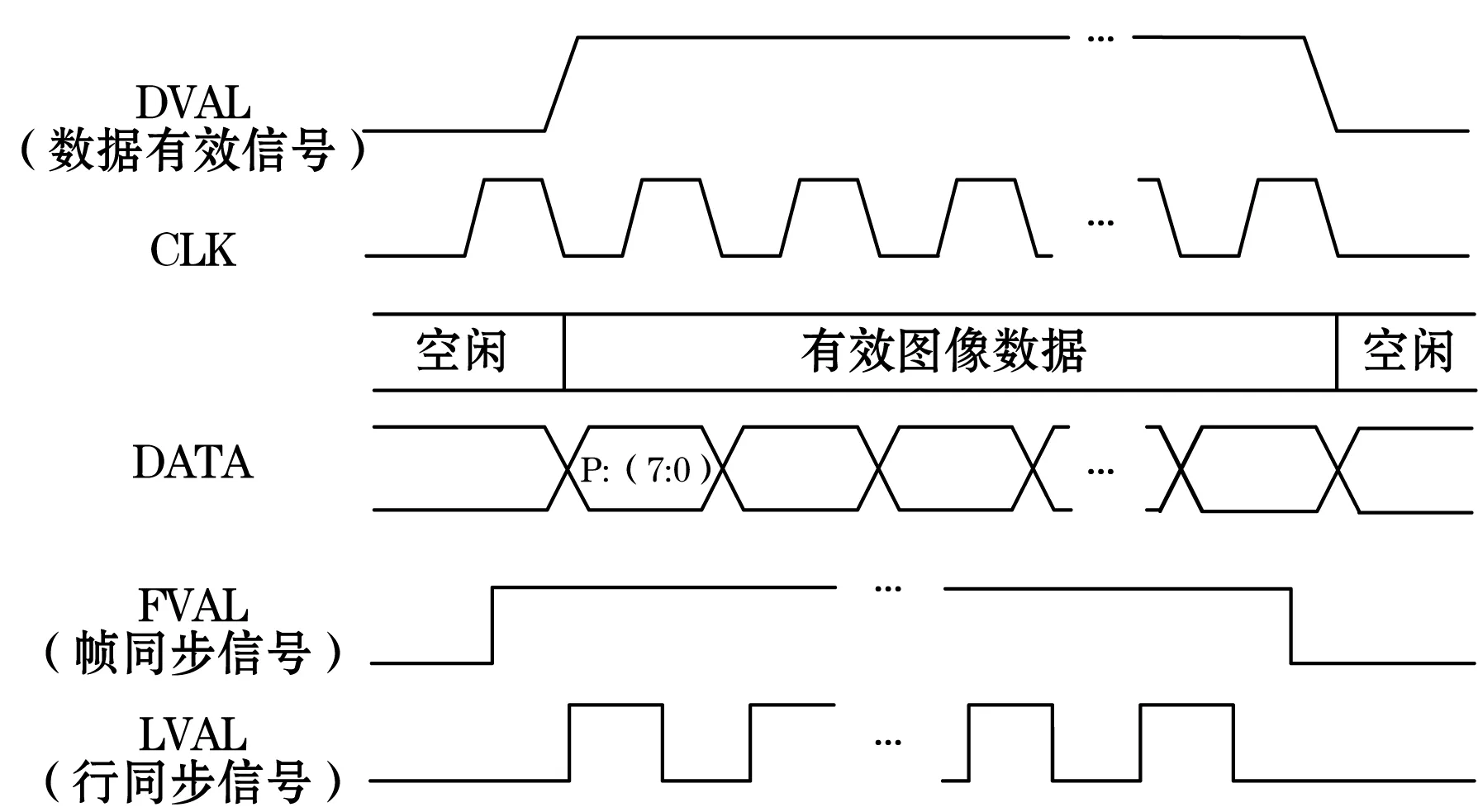

Camera Link标准中的28位图像数据信号是接收端的关键,其中FVAL(帧同步信号)、LVAL(行同步信号)和DVAL(数据有效信号)控制图像数据的接收[8]。FPGA作为接收端可以将外部输入的4对差分图像数据信号,解串为28位并行信号。本方案采用Base型图像传输模式,有效图像数据为8位。根据Camera Link协议对TX/RX端口的28位数据信号以抽象化形式分为PortA/B/C,由于设计中约定每幅图像数据格式为1 920×1 080,数据大小为4.147 Mbyte,每2个字节表示1个像素点,所以只采用PortA的8位数据为图像有效数据,可以达到在1 s内连续发送并接收10幅图像。Camera Link Port端口映射表和信号时序图分别如表1、图3所示。

表1 Camera Link Port端口映射表

图3 Camera Link端口映射时序

2.2 数据接收端逻辑实现

当帧同步信号为“1”时表示相机即将发送新一帧图像数据,行同步信号由“0”变为“1”瞬间即预发送新一行数据。若相机开始发送图像数据,则数据有效信号置为“1”。在时钟信号的同步下,图像数据可进行有效传输。具体时序如图4所示。

图4 Camera Link信号接收时序

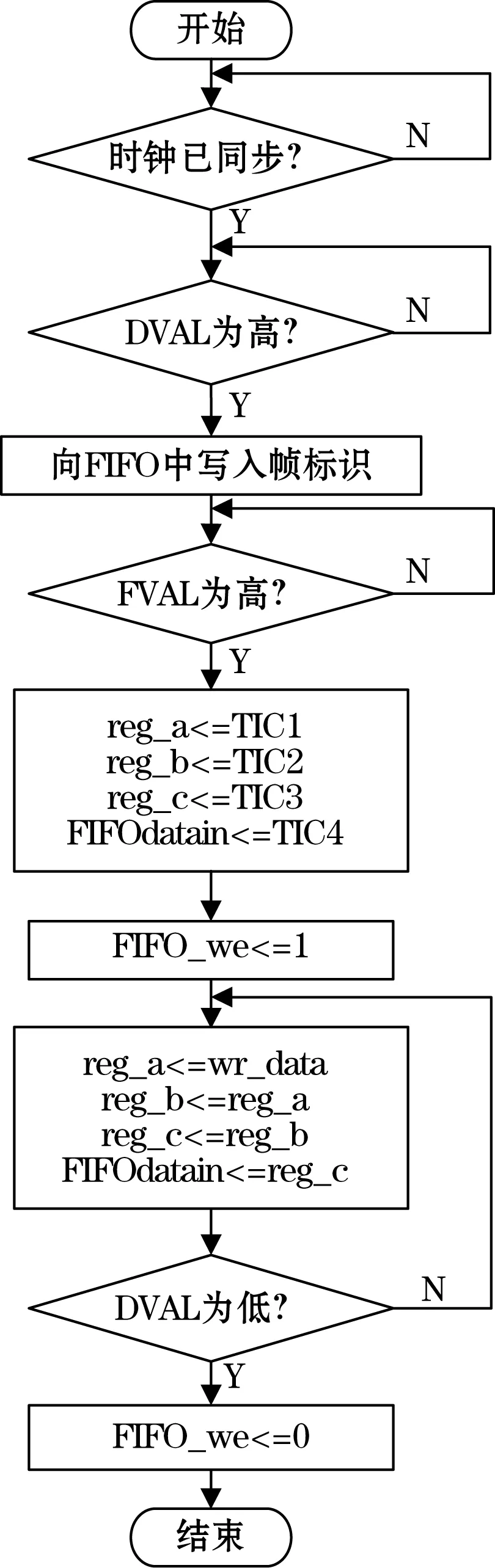

本设计中图像传输时钟频率为54 MHz,所以接收端经接口单元时钟模块的输出时钟频率也为54 MHz。为防止传输过程中数据丢失,只有当控制逻辑检测到接收端与发送端的时钟同步后,再对各控制信号进行判断,并开始接收数据。编帧单元将经过解串后的28位并行数据进行编帧,在保留8位有效数据的同时去除无效数据。在数据写入FIFO时,要对有效图像数据加入帧标识、帧计数、TIC(时间)计数等信息,统一形成记录数据帧。由于每帧的数据为连续发送且数据量约为150 KB,为避免在数据帧中加入帧标识的时间过于紧凑,逻辑设计在DVAL信号为高时先将帧标识写入,等待FVAL信号为高后再将每一位TIC计数依次写入reg_a/b/c寄存器,最后移位寄存器写入后级缓存,以此进行循环。当检测到DVAL为低时,FIFO使能信号FIFO_we关闭,停止数据写入。具体数据接收端逻辑流程框图如图5所示。

图5 接收端逻辑流程框图

3 测试结果与分析

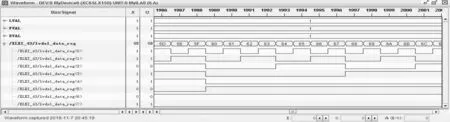

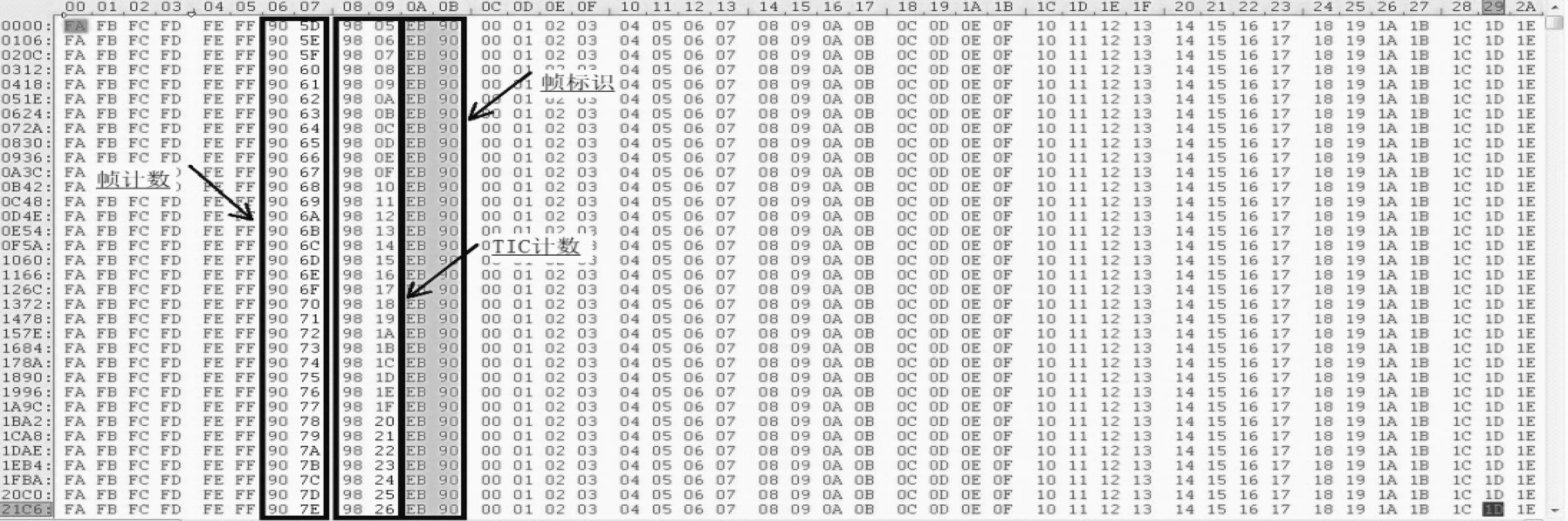

为验证以FPGA实现Camera Link图像接口设计的正确性和可靠性,搭建了模拟图像发送测试平台,可完成控制指令发送及状态监测、数据预处理与丢帧检测功能,并在软件界面显示。图像信号发生板卡采用Camera Link专用转接芯片DS90CR285,用来模拟相机通过Camera Link发送图像数据,所发送模拟数据为自递增数,接口频率为54 MHz。最后使用ChipScope软件对Camera Link接口接收端进行逻辑仿真,所抓信号为8位图像数据和控制信号,其中DVAL为数据有效信号,在保持高电平时有效数据开始发送。接口接收到数据后进行编帧,然后上传至上位机进行分解、校验。经多次测试验证与校验并无误码显示,测试结果符合设计要求。仿真结果和图像数据分解结果分别如图6、图7所示。

图6 接收端信号仿真

图7 图像数据分解结果

4 结束语

通过FPGA内部IP核原语直接实现Camera Link标准接口的图像数据接收,经接口仿真试验和配套测试台测试,验证了本设计在图像接收过程中的高效性和高可靠性[9]。相比传统使用Camera Link转接芯片的方法,本方案显著减少了硬件布局空间和主控芯片I/O口资源占有率,进一步提升了系统集成度,利于产品小型化发展,具有高可靠性和实际利用价值[10]。