用于AlGaN基DUV LED封装的高反射镀铝DPC陶瓷基板

杨宇铭, 李 燕, 郑怀文, 于 飞, 杨 华*, 伊晓燕, 王军喜*, 李晋闽

(1. 中国科学院 半导体研究所 半导体照明研发中心, 北京 100083;2. 中国科学院大学 材料科学与光电技术学院, 北京 100049)

1 引 言

与汞灯相比,基于AlGaN材料的紫外发光二极管(UV LED)具有体积小、高效率、低能耗、安全环保、波长可调节等优势[1-2],在杀菌消毒、除臭净水、UV固化、光医疗、光催化、全光谱照明、新型显示与健康照明等领域有着广泛的应用[3-5],并被寄希望以在未来完全替代汞灯。然而,目前大多数UV LED的外量子效率(EQE)仍低于6%,仅有少数报道获得了高于10%的EQE[6-8]。UV LED极差的EQE很大程度上源于封装工艺的限制带来的低光提取效率(LEE)。在传统白光LED封装中大量使用的有机材料在UV波段表现出极差的透射率与可靠性,很难直接在UV LED,尤其是深紫外(DUV,λ≤300 nm)LED封装中使用[9-10]。同时,DUV LED的自发热现象也十分严重。这些因素使封装后的DUV LED器件大多表现出极差的提取效率与可靠性,这极大地制约了DUV LED的发展。

直接镀铜(DPC)陶瓷基板具有高导热性和高图形精度,可以提供与LED间的良好电接触,可直接用于倒装LED封装[11]。目前Al2O3与AlN基DPC陶瓷基板已经广泛用于商业LED封装。最近也有很多研究致力于通过改进DPC基板来提升UV LED的光效。Xu等人[12]通过增加基板内部的Cu金属通孔数量降低了基板的热阻。Pai等人[13]制作了高反射的Al金属围坝并将其粘合在陶瓷基板上。Sun等人[14]提出利用高岭土悬浮液直接油墨书写在平面DPC基板上构建坝。Yang等人[11]通过电镀在DPC基板上制作了Ni金属围坝,形成了3DPC基板。但是现在还很少见到关于在DPC基板的焊盘表面金属镀层上进行改进的报道,而焊盘表面的金属会对UV LED的光性能产生很大的影响。

当下常见的用于商业UV LED封装的DPC陶瓷基板的Cu焊盘表面都镀了Ni/Au金属覆盖层,以提高其可焊性和抗氧化性[15]。然而Au金属在UV波段反射率极低,大部分的UV光都被吸收,这将极大地影响器件的光提取。而Al是常见金属中在UV波段反射率最高的一种,在整个UV波段反射率始终超过80%,是UV光的理想反射器。有许多研究者已经致力于将Al运用到UV LED芯片的电极中。Maeda等人[16]通过使用透明p-AlGaN接触层和Ni/Al电极替代p-GaN接触层和Ni/Au电极。Lobo等人[17]设计了一种p型电极结构,包括一个Pd欧姆接触像素阵列和覆盖在该阵列之上的Al反射层。还有许多研究组将Al金属运用在全向反射器中[18-20]。然而,商业倒装UV LED中使用的p-GaN层对DUV波段的光有强烈的吸收作用,只有极少的DUV光能够达到电极反射镜处。因此,这些芯片层级上的电极改进必须在使用了透明p-AlGaN接触层的LED上才能产生显著效果,而现在高质量的p-AlGaN是难以得到的,这限制了这条技术路线在DUV波段的发展和应用。

Al金属及其合金也已经被用于UV LED封装中。例如,铝合金在UV波段内可以提供比Au更高的反射率,因而已被用作UV LED封装围坝。此外,由Al制成的金属基板已用于UV封装多年,但由于金属基板中存在有机物层,其相比陶瓷基板在稳定性方面存在较多不足。在这种情况下,找到在DPC陶瓷基板封装技术中利用Al金属的优秀光学性能的途径志在必行。最直接的想法是使用Al金属镀层代替Ni/Au金属镀层。但是由于Al金属表面覆盖的氧化膜的影响,导致其与锡膏等焊料浸润性极差,也不兼容共晶焊接工艺,无法直接与倒装UV LED芯片实现电接触。因此这种方案也是不可行的,需要进行进一步的研究,探索能够兼顾光学性能和倒装焊接工艺的基板焊盘设计方案。

在这项工作中,我们设计了一种镀有双层金属覆盖层的DPC陶瓷基板焊盘结构,它在Cu焊盘之上拥有一层完全覆盖它的Ni/Au金属覆盖层和一层局部覆盖Ni/Au金属层的图形化Al金属覆盖层,下层的Au在图形化Al金属层的窗口中暴露出来。在封装过程中通过窗口中暴露出的Au金属部分实现电接触,而大面积的表面Al金属则可以提供良好的漫反射。实验结果表明,与传统结构相比,这种新型的基板可以使DUV LED的光输出功率(LOP)得到较大的提升,从而提升了芯片的功率效率(WPE)和EQE,同时还能保证芯片的热学性能和可靠性不因结构的改变而下降。

2 实 验

通过传统DPC工艺制备出Cu焊盘表面镀有Ni/Au金属覆盖层的AlN陶瓷基板。制备的基板为3535型号,即其尺寸为3.5 mm×3.5 mm。基板陶瓷厚0.5 mm,其上表面焊盘的直径为2.6 mm。其制备过程如下:首先,在裸露的AlN陶瓷板上钻两个腔,每个空腔的直径为90 μm。通过溅射将Ti/Cu种子层镀在陶瓷基板表面和空腔内壁上。然后,将干膜光刻胶粘附在基板表面并进行曝光、显影以形成电路图案。随后进行电镀铜来填充空腔以获得导电通路,并且将基板的表面电路加厚至70 μm从而形成Cu金属焊盘。接下来,在Cu焊盘上蒸镀Ni/Au覆盖层,Au层的厚度为0.05 μm。最后,剥离干膜并蚀刻去除金属籽晶层。制备得到的DPC陶瓷基板的结构如图1 (b)所示。

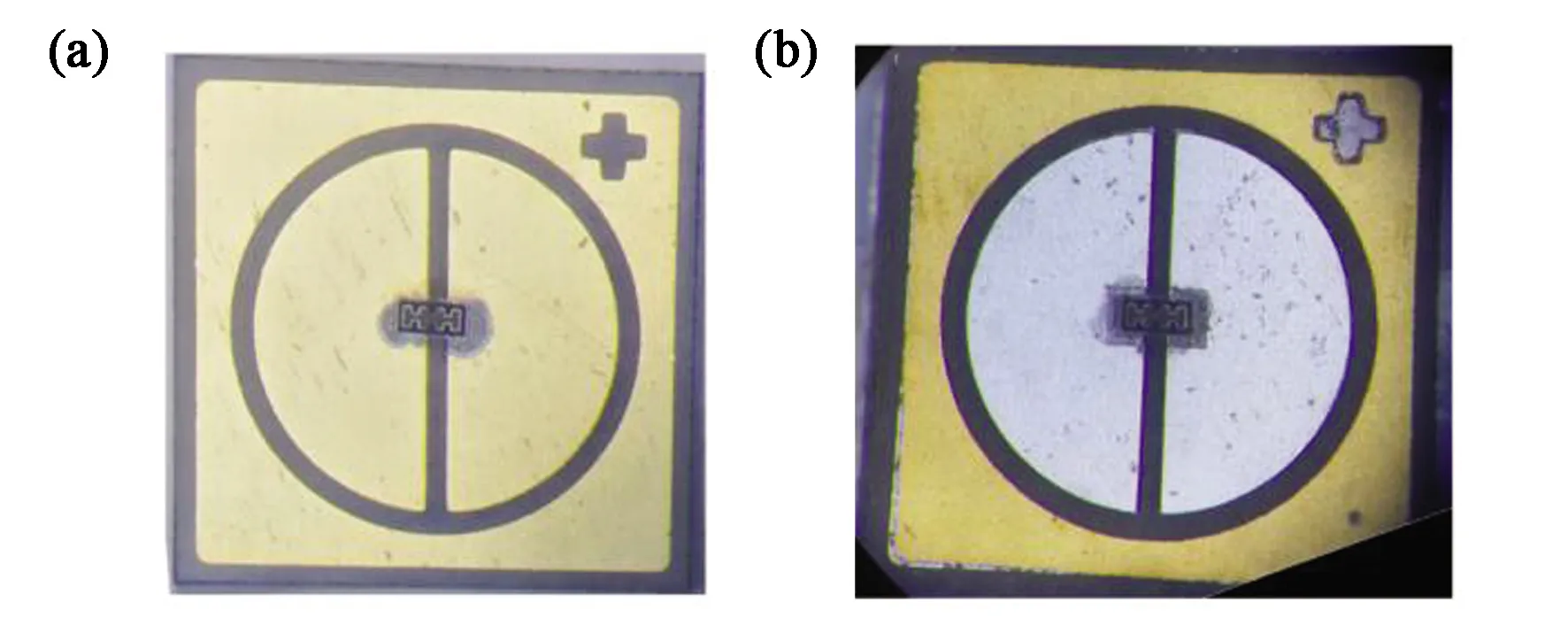

图1 (a)双层金属镀层DPC陶瓷基板俯视图;(b)传统的DPC陶瓷基板;(c)蒸镀图形化的Al金属层得到双层金属镀层DPC陶瓷基板;(d)将LED芯片焊接在基板上;(e)将围坝粘贴在基板上;(f)将石英玻璃粘贴在围坝上。Fig.1 (a) Top view of the Al-plated DPC ceramic substrate; (b) Traditional DPC ceramic substrate; (c) Al-plated DPC ceramic substrate; (d) LED was soldered on the substrate; (e) Dam was pasted on the substrate; (f) Quartz glass was pasted on the dam.

图1(b)~(f)显示了增镀了Al镀层的双层金属镀层DPC陶瓷基板的制备和封装流程。实验中所使用的LED为Photon Wave公司的280 nm DUV LED,LED的额定电流为20 mA,尺寸为530 μm×270 μm,其电极的尺寸为180 μm ×200 μm。首先在制备好的DPC AlN陶瓷基板的焊盘表面通过光刻与电子束蒸镀(EB)的方法得到一层0.5 μm厚的图形化的Al金属层,Al层的表面粗糙,照射到Al表面的DUV光可以发生良好的漫反射。在Al金属层的中心部分留有一个680 μm×400 μm大的窗口,该窗口略大于芯片尺寸,窗口中暴露出下层的Au金属。接下来在这一窗口上点涂锡膏,将芯片的电极通过锡膏贴在焊盘上面,通过回流焊工艺进行固化。锡膏与Au金属之间有极佳的可焊性,可以将芯片牢牢焊在基板上。然后,以相同的方式将陶瓷基板和六角形Al散热器焊接在一起,以实现电互连和实验过程中的散热。在焊盘外围使用固晶胶粘接高反射的Al合金围坝,再在围坝上沿粘接平面石英玻璃透镜。最后,将带有坝和透镜的基板在130 ℃高温下烘烤固化30 min,得到封装好的LED器件。对没有蒸镀Al金属层的商业DPC基板进行同样的锡焊固晶、粘接围坝、粘接石英透镜步骤,作为对照组。图2展示了焊接在这两种基板上的LED的照片。用作表面镀层的金属Au、金属Al和用作围坝的Al合金在UV-可见光波段的反射率如图3所示,Au金属在280 nm处的反射率仅为约30%,而金属Al在该波段反射率高达约90%,其合金材料在280 nm处反射率也有约50%。对两组样品分别进行光电性能和热阻测试,从而分析镀Al的DPC陶瓷基板对封装器件的效率和可靠性带来的影响。

图2 将LED分别焊接在(a)传统和(b)双层金属镀层DPC陶瓷基板上Fig.2 LEDs soldered on (a) traditional DPC ceramic substrate and (b) Al-plated DPC ceramic substrate

图3 金属Au、金属Al和Al合金在UV-可见光波段的反射率。Fig.3 UV-visible reflectance of Au, Al and Al alloy.

实验中使用的锡膏是Earlysun的ES-1000 SnAgCu锡膏。回流焊工艺使用了TORCH的T200C回流焊机。封装器件的光电性能测试结果由EVERFINE的HAAS-2000积分球提供。热学测试结果由Mentor Graphics的T3Ster提供,实验中使用的加热电流和测试电流分别为40 mA和1 mA,通过T3Ster Master软件分析热阻测试数据。图3中的反射率测试结果由Hitachi的UH4150分光光度计提供。

3 结果与讨论

3.1 光学性能

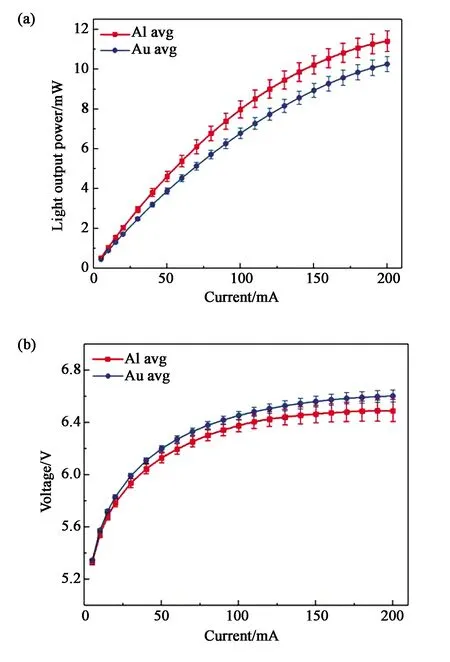

两组样品在5~200 mA的正向输入电流下的光电测试结果如图4所示,实验组和对照组分别标记为Group Al和Group Au,每组包含7个样品,对每组样品的测试结果取平均值并添加误差棒。图4 (a)展示了两组样品的I-P曲线,实验组的平均LOP相比对照组得到了极大的提升。在20 mA正向输入电流下,平均LOP由1.71 mW提升到2.03 mW,提升了18.7%;在40 mA正向输入电流下,平均LOP达到最大提升,由3.20 mW提升到3.81 mW,提升了高达19.2%。当测试电流大于100 mA后,LOP的提升程度开始缓慢下降,但在200 mA的大电流下,LOP仍存在11.3%的提升,由10.26 mW提升到11.42 mW。随着测试电流从20 mA增加到200 mA,实验组中所有样品的LOP都始终比对照组样品更高,且两组之间的差距始终大于组内偏差。因此可以断定,LOP的提升是由DPC基板的改进带来的。

图4 分别使用传统(Au)和双层金属镀层(Al)DPC陶瓷基板封装的两组LED样品的(a) I-P与(b) I-V曲线Fig.4 (a) I-P characteristics and (b) I-V characteristics of LEDs packaged by Al-plated DPC ceramic substrates (Group Al) and traditional DPC ceramic substrates (Group Au).

图4 (b)展示了样品的I-V曲线,所有样品的电压均在约150 mA处达到饱和。在相同的电流下,实验组的平均电压略低于对照组,但其差距始终保持在1.5%以内,且两组之间的差距小于组内偏差。因此可以认为这是芯片质量造成的误差,且不会对LED的光学及热学性能产生足够的影响。

通过以上数据计算了每个样品的WPE与EQE,来表征两组样品的效率。LED的WPE定义为LED的LOP与输入功率之比,即

ηpower=P/IV,

(1)

式中:P表示LED的LOP,I和V分别表示LED的驱动电流和工作电压。

EQE定义为单位时间内发射到LED外部的光子数与单位时间内注入LED的电子-空穴对数之比,为内量子效率(IQE)和LEE的乘积,即

ηext=ηintηextraction=(P/hν)/(I/e),

(2)

式中:h、ν和e分别表示普朗克常数、LED发射的光的频率以及基本电荷。

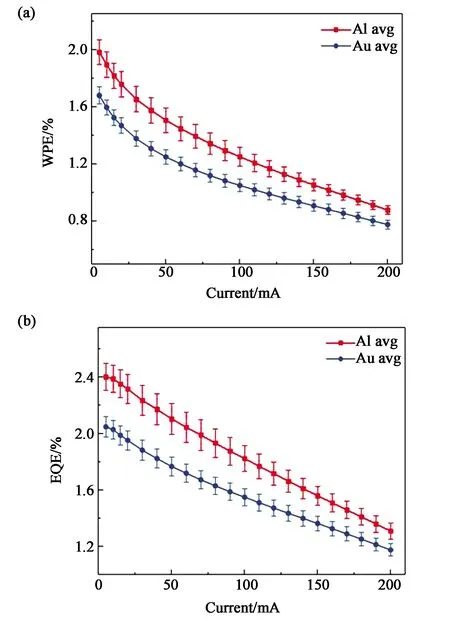

实验用的芯片具有相同的IQE,因此可以用EQE的提升来表示LEE的提升,EQE增强系数等于LEE增强系数。两组样品的平均WPE和EQE分别表示在图5 (a)和(b)中。由于较高的LOP,实验组器件的WPE得到了较大的提升。在20 mA的正向输入电流下,相比对照组样品,实验组样品的平均WPE从1.47%提升至1.76%,WPE增强系数达到了1.20。同时,20 mA下的平均EQE从对照组的1.95%提升至实验组的2.32%,EQE增强系数达到了1.19。在200 mA的大电流下,EQE增强系数仍高达1.11。显然,通过使用双层金属镀层DPC陶瓷基板可以提高DUV LED的效率,这归因于光学性能的极大提升。

图5 分别使用传统(Au)和双层金属镀层(Al)DPC陶瓷基板封装的两组LED样品的(a) WPE与(b) EQE曲线Fig.5 (a) WPE and (b) EQE of LEDs packaged by Al-plated DPC ceramic substrates (Group Al) and traditional DPC ceramic substrates (Group Au)

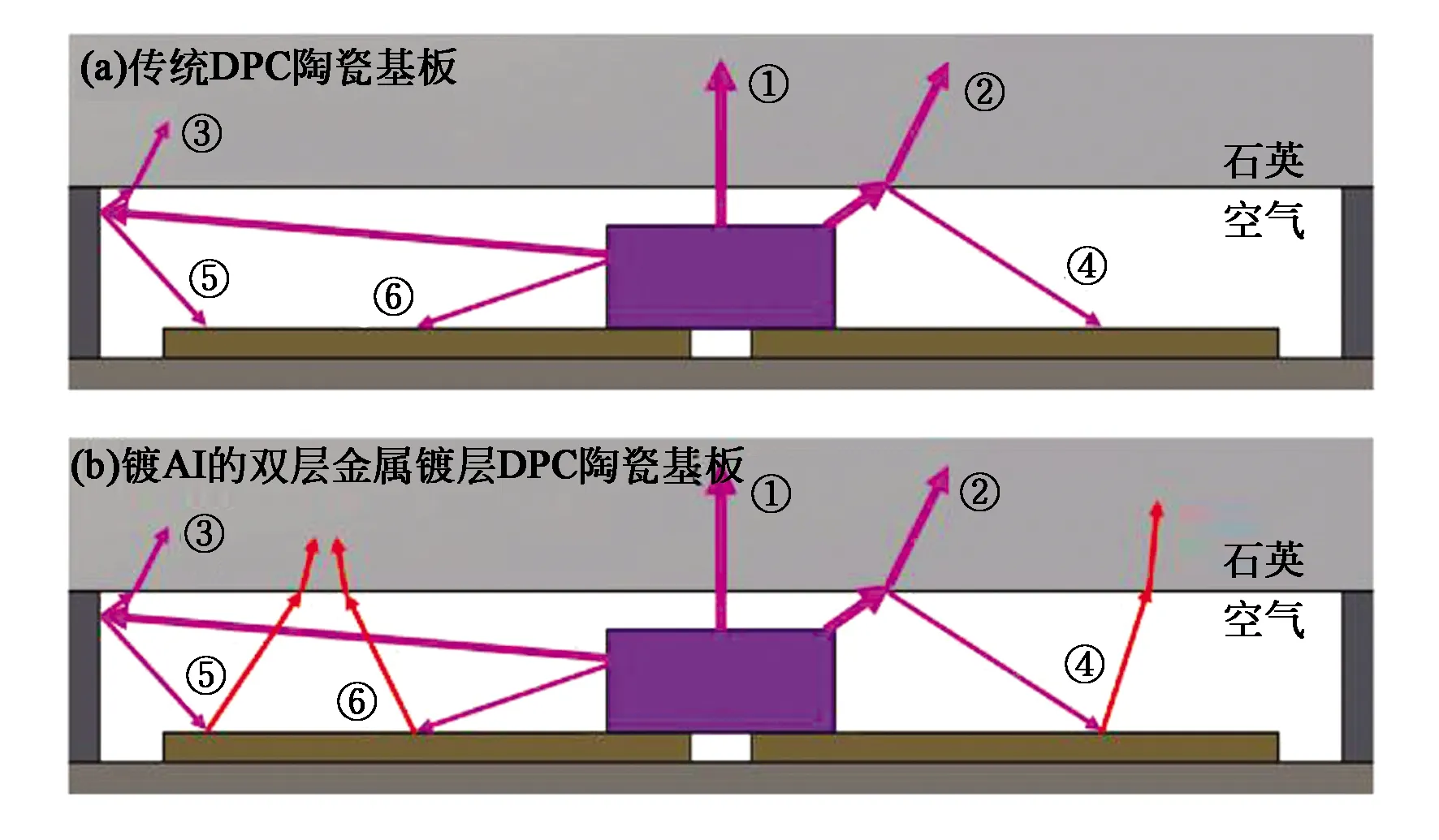

图6显示了使用DPC陶瓷基板封装后的LED器件的几种典型光路。对于使用传统DPC陶瓷基板封装的样品,只有向上方发射或散射的光线①~③能够提取出样品。而由于Au层对UV光的严重吸收,在石英玻璃表面产生的反射光线④,在围坝表面发生漫反射而向下方反射的光线⑤,以及大量的直接出射到基板焊盘上的光线⑥等向其他方向发射或散射的光线,都会被焊盘表面的Au金属吸收而无法提取出样品。但是,在镀了Al金属层后,这些光线在Al金属层表面将会发生漫反射,从而得以出射至样品外部,成功得到收集利用。这解释了实验组器件LOP得到极大提升的原因。

图6 分别使用(a)传统和(b)镀Al的双层金属镀层DPC陶瓷基板封装的LED的典型光路Fig.6 Several typical optical paths of LEDs packaged with (a) traditional DPC ceramic substrates and (b) Al-plated DPC ceramic substrates.

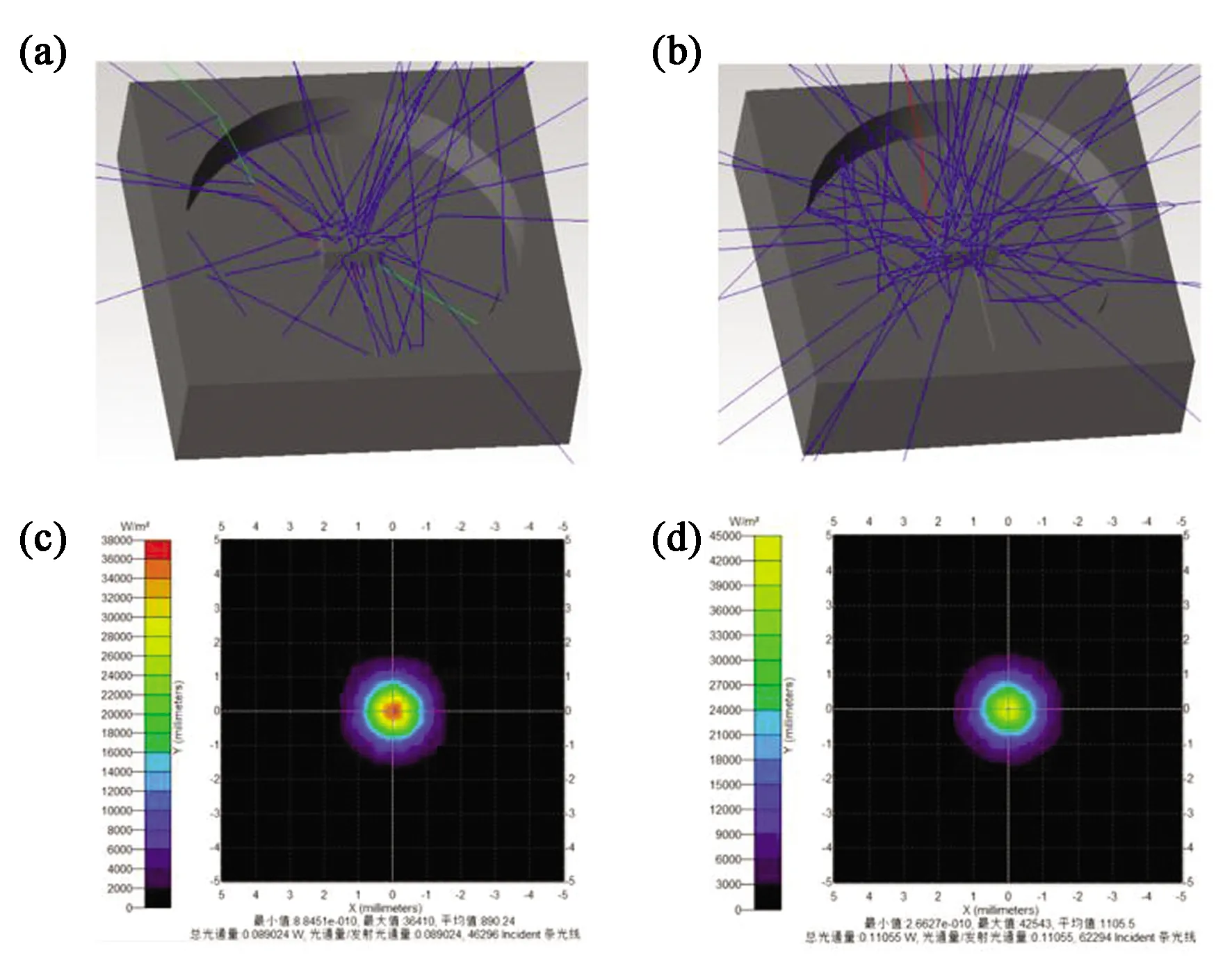

建立了使用这两种基板封装的LED封装体的模型,使用光学射线追迹仿真软件进行仿真,两模型唯一的差别是基板焊盘表面是否具有Al反射层。仿真得到的光路图如图7 (a)和(b)所示,图中显示的光线数为实际仿真光线的1‰。可以看到,图7 (a)所示的传统DPC陶瓷基板中大部分入射到基板焊盘上的光都终止在焊盘表面的Au层上,而图7 (b)所示的镀Al DPC陶瓷基板中入射到焊盘表面Al层上的光却几乎全部被反射。两种基板封装的LED出光面处的光分布如图7(c)和(d)所示,传统基板封装的LED提取效率较低且光线在中心部分较为集中,而镀Al基板封装的LED提取效率相比传统基板有较大提升,LEE增强系数达到1.24,与实验结果有较好的一致性,可以作为实验结果的良好验证。

图7 光学射线追迹仿真结果。(a)传统DPC陶瓷基板封装LED的仿真光路图;(b)镀Al DPC陶瓷基板封装LED的仿真光路图;(c)传统DPC陶瓷基板封装LED出光面处的光分布;(d)镀Al DPC陶瓷基板封装LED出光面处的光分布。Fig.7 Simulation results of optical ray-tracing. (a) Light path diagram of traditional DPC ceramic substrate package LED; (b) Light path diagram of Al-plated DPC ceramic substrate package LED; (c) Light distribution of traditional DPC ceramic substrate package LED; (d) Light distribution of Al-plated DPC ceramic substrate package LED.

3.2 热模型与热阻

在大于100 mA的电流下,随着电流的增加,平均LOP和EQE的提升幅度有所减小,这很可能是受到了热效应的影响。DUV LED封装的热损耗功率约为总功率的98%,这会对LED的光学特性产生极大的影响[12]。

图8显示了样品的热模型与其主要散热途径。进行测试时的总热阻为:

Rth=Rth-chip+Rth-solder1+Rth-ceramic+

Rth-solder2+Rth-Al plate,

(3)

图8 DPC陶瓷基板封装的倒装UV LED的热模型与主要散热途径Fig.8 Thermal model and main heat transfer path of flip-chip LED packaged by DPC ceramic substrate.

式中:Rth-chip、Rth-solder1、Rth-ceramic、Rth-solder2和Rth-Al plate分别表示热源到芯片电极的热阻、芯片焊接点的热阻、DPC陶瓷基板的热阻、基板和Al散热器间焊接点的热阻以及六角Al散热器的热阻。

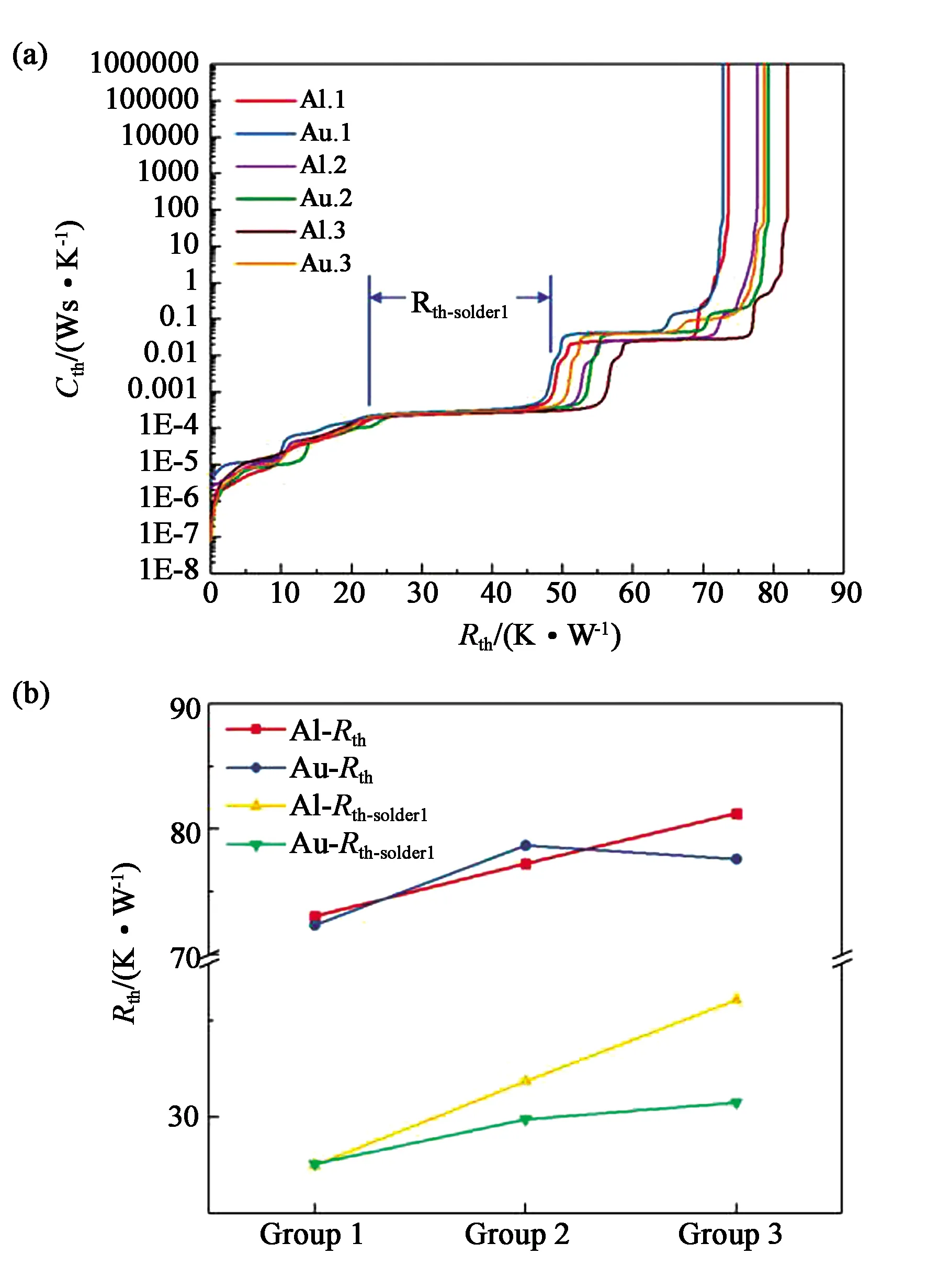

我们选取了一些样品进行瞬态热阻测试,将所挑选的典型样品按照封装时固晶步骤中所点涂的锡膏的量依次分成3组,锡膏量最少的记为Group 1,最多的记为Group 3,余下的一组则为Group 2。每组有2个样品,分别由镀Al的DPC陶瓷基板和传统的DPC陶瓷基板封装。这6个样本分别记录为Al.1、Au.1、Al.2、Au.2、Al.3和Au.3,对每组样品进行瞬态热阻测试和分析。测得的积分结构函数曲线如图9 (a)所示,可以看出芯片焊接点热阻Rth-solder1是影响总热阻Rth的主要因素。通过图9 (a)读取出每个样品的Rth和Rth-solder1,样品Al.1、Au.1、Al.2、Au.2、Al.3和Au.3的Rth分别约为73,72,77,78,81,77 K/W,而它们的Rth-solder1则分别约为27,27,32,30,36,31 K/W,结果如图9(b)所示。

图9 (a)被测样品的积分结构函数图; (b)样品的总热阻Rth与芯片焊接处热阻Rth-solder1。Fig.9 (a) Integral structure functions; (b) Total thermal resistance Rth and thermal resistance of die attach Rth-solder1 of the 6 samples.

数据表明,Group 1和2中实验组与对照组的Rth和Rth-solder1都相差不大,而且Group 2中两样品的Rth和Rth-solder1均比Group 1大4 K/W。因此可以判断,Rth-solder1几乎完全提供了Rth的增加。然而,Group 3相对于Group 2,Au.3的Rth和Rth-solder1均不再增加,但Al.3的Rth-solder1却增加了4 K/W,导致其Rth也随之增加了4 K/W。由此看出,锡膏的量对样品的热阻产生直接影响,且锡膏的量越多,实验组与对照组之间的热阻差越大。这是因为Al金属表面与锡膏的不浸润,导致固化后的锡膏被局限在Al金属层的窗口中,无法向覆盖了Al金属的部分扩展,从而使焊接层的厚度随着锡膏的增多而增加,其热阻Rth-solder1也就随之增大。而对于没有镀Al层的对照组基板,其上的锡膏可以在Au金属层上扩散平铺,如图2 (a)所示,因此固化后的锡膏厚度在增加到一定程度之后不再增加,取而代之的是其固化后锡膏的表面积会随锡膏的量增大。由于Al.3的热阻较大,导致了其在高电流下EQE下降较快,相比对照组的提升幅度减小。

由热测试结果可知,实验组样品的热阻上升是由封装工艺过程中锡膏的量过多而引入的。只要在封装工艺中控制锡膏的量在一定的范围内,就可以消除这一影响,得到和对照组热阻相近的样品(如样品Al.1)。

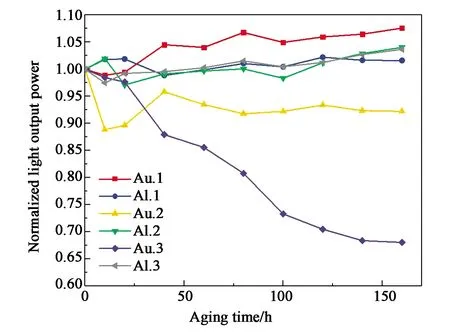

3.3 可靠性

使用EVERFINE的DJ5000 LED Aging Tester对上述的6个样品进行老化试验,在20 mA的驱动电流下老化了160 h。老化过程中各组样品LOP的变化如图10所示,对结果进行了归一化处理。在120 h时Au.3的LOP就已经衰减到了初始的70%,Au.2的LOP也在160 h后衰减到了初始值的92%。Au.3可以被认为已经失效,推测失效可能是由于电极的退化所致,而电极的退化则可能是由于在较高的结温下电极中的Au和焊料中的Sn之间的热膨胀系数差异较大所造成的[21]。因此认为Au.3的失效主要是由于热阻引起的结温过高。这说明对于对照组来说,焊接点热阻Rth-solder1对器件的寿命有直接的影响,器件的Rth-solder1越大,寿命越短。而Au.1不仅没有衰减,LOP反而有所上升,在160 h老化后达到了初始值的107%。这可能与掺杂剂Mg的激活引起的p-GaN中空穴浓度的增加有关[22],而不是封装方面的影响。然而,与对照组不同,实验组的3个样品虽然热阻差别较大,但其归一化LOP却始终非常接近,与初始值相比都没有产生较明显的变化,在老化期间内始终保持稳定。老化160 h后,样品Al.1、Al.2和Al.3的归一化LOP分别为102%、104%和104%。因此,与样品Au.2和Au.3相比,样品Al.2和Al.3的Rth-solder1更大,却具有更好的可靠性。这一现象一般认为是反常规的。这很可能是由于实验组在相同电流下的WPE较大,因此在工作电压下工作时,实验组器件产生的总热量比对照组小很多,即使散热能力较差,其作用在LED芯片上的热能仍小于对照组。因此,在工作电流下,使用双层金属镀层DPC陶瓷基板封装的LED样品虽然平均热阻较高,反而却获得了更好的可靠性和更长的寿命。

图10 六组LED样品在老化期间的归一化LOPFig.10 Normalized LOP of the 6 samples during the aging period

4 结 论

本文设计并制备了一种带有高反射Al金属镀层的双层金属镀层DPC陶瓷基板,用于DUV LED的封装。实验结果显示,使用了这种封装基板的LED器件的LOP提升了19.2%,其WPE增强系数达1.20,EQE增强系数达1.19,均得到了极大的提升。此外,在焊接层较薄时,器件的热阻并不会明显增加,同时产生的热量却减少,从而使其工作电流下的可靠性得到提升。这些结果为通过封装来提升DUV LED的出光效率提出了一种新的可行的途径。