一种应用于便携式陀螺仪的ZOOM结构ADC

梅金硕 崔天宝

摘 要:设计了一种用于微机电系统(MEMS)陀螺传感器中的高精度ZOOM型模数转换器(ADC)。该结构由逐次逼近型(SAR)ADC和Sigma Delta调制器构成,通过SAR ADC的粗略转换缩小了Sigma Delta调制器的参考范围,提高了整体的转换精度。基于0.35um BCD工艺对该结构进行电路设计,并进行指标仿真。仿真结果表明,该ZOOM ADC对中心频率10KHz、带宽100Hz的信号转换动态范围达到120dB,满足MEMS陀螺接口电路中ADC的性能要求。

关键词:MEMS接口电路;ZOOM ADC;缩放型;高精度

DOI:10.15938/j.jhust.2020.03.004

中图分类号: TB303;TN431.1

文献标志码: A

文章编号: 1007-2683(2020)03-0018-07

Abstract:This design is a high precision ZOOM analog-to-digital converter (ADC) presented for using in microelectromechanical systems (MEMS) gyroscope sensors. The structure consists of a successive approximation (SAR) ADC and a Sigma Delta modulator. The coarse conversion of the SAR ADC reduces the reference range of the Sigma Delta modulator and improves the overall conversion accuracy. The structure was designed with 0.35um BCD process, and simulated. The simulation results show that the ZOOM ADC has a dynamic range of 120dB for the center frequency of 10KHz and a bandwidth of 100Hz, which satisfies the performance requirements of the ADC in the MEMS gyroscope interface circuit.

Keywords:MEMS interface circuit; ZOOM ADC; zoom type; high precision

0 引 言

随着高速信号处理、精确制导等方面需求的不断增加,对传感器及接口电路的精度要求和功耗要求也随之提高[1-2],尤其在MEMS领域便携式陀螺中更为突出。因此原本应用于此的多种中等精度低功耗的模数转换器(ADC)不再适用,而传统的高精度ADC功耗较高,并不适合应用在电池驱动的便携设备中,因此高精度低功耗ADC的研究顯得日益重要。2013年,韩国延世大学Chae等[3]提出一种应用于直流信号检测的ZOOM结构ADC,该结构将传统低功耗中低精度的逐次逼近型(SAR)ADC与高精度Sigma Delta型ADC结合,相比传统高精度ADC,该ADC能够显著提高能量效率;2017年荷兰代尔夫特大学Gnen等[4]提出了应用于音频领域的改进型动态ZOOM 结构ADC,相比上一种结构提高了所处理信号的带宽,使ZOOM型结构的应用范围变得更为广泛。

基于ZOOM型结构,本文设计一款应用于MEMS陀螺仪接口领域的ADC。利用SAR ADC与Sigma Delta调制器并行工作,在保证高精度的前提下提高能量效率,因此更适用于电池驱动的便携检测设备中。由于所采用陀螺结构谐振频率为10kHz,所以基于信号带宽的考量本设计采用改进型的动态ZOOM结构。该ADC性能指标设计为:差分输入信号幅度大于1.6Vfull,scale,信号中心频率为10kHz,信号带宽为100Hz,动态范围大于120dB。

1 原 理

动态ZOOM ADC的结构框图如图1所示。模拟输入信号并行进入SAR ADC和Sigma Delta调制器两条路径。

在SAR ADC通路,输入信号经过比较器和数字逻辑完成一次比较,比较得到的数字结果通过N位数模转换器(DAC)还原回模拟信号与输入作差,对差值再进行比较得到下一位数字输出结果。比较次数越多得到的数字输出信号越能精确地还原模拟输入信号。经过N个周期的逐次比较得到N位数字输出信号D,其最小有效位(LSB)為Vfull,scale/2N;

该N位数字输出信号经过运算逻辑部分处理后将一个确定的数字信号转换为一对参考信号,数字信号处在参考信号中间,该参考信号进入Sigma Delta调制器通过N位DAC转换为一对高低参考电压:

由式(1)和(2)可知调制器的参考范围由满摆幅电压Vfull,scale大大缩减至原来的1/2N;

在Sigma Delta调制器通路,输入信号经过环路滤波器和一位比较器后得到一位数字输出,在过采样时钟频率下,每个转换周期即可产生一组一位的数字码流,其中,D·Vfull,scale/2N作为码流中低位输出,(D+1)·Vfull,scale/2N作为码流中高位输出,完成输入的模拟信号的脉冲宽度调制(PWM)。但由于采用的参考电压范围大幅缩小并且随着SAR ADC的转换结果而不断更新,所以实际转换中得到的比较结果体现为多位的数字码流[5]。

与传统结构Sigma Delta调制器相比,在相同输入信号、相同过采样频率条件下,该结构中的Sigma Delta调制器能显著降低调制器的量化噪声,提高信噪比(SNR)[6-7]。量化噪声幅度减小后更接近于白噪声,有利于噪声整形能力的提高和弦音现象的避免。

在系统的一个转换周期内两条通路分别完成转换后, Sigma Delta调制器产生的一位数字码流进入后端的降采样抽取滤波器转换为K位数字信号,该信号与SAR ADC产生的N位数字信号共同进入权重计算电路进行权重相加,得到最终(N+K)位数字信号,完成系统整体的一次模数转换。

值得注意的是,由于SAR ADC的转换过程会使调制器参考电压的刷新存在N个时钟周期的延迟[8],当输入信号变化速度过快或幅度过大时,输入信号可能过于靠近一侧参考电压或超出参考电压范围,导致调制器出现过载(OL)无法正常工作,这一现象在高阶调制器中更为明显。同时非理想SAR ADC由于电容失配等问题可能导致转换结果出现误差,更增加了过载的可能性[9]。为了解决这一问题,可人为将已经显著减小的调制器参考电压范围适当地放大,参考电压范围的变化如图2所示。

引入放大系数M,将原来的参考电压范围放大至:

由式(3)和(4)可知调制器参考电压范围扩大了M倍,通过调节放大系数M,可以保证信号在所有情况下都能处于参考电压范围内。此方法使得系统对SAR ADC匹配性的要求降低并保证Sigma Delta调制器能够稳定工作。在电路结构中引入该放大系数M可通过较为简单的数字电路实现,不会额外增加电路设计难度。但参考电压范围的再次扩大又会导致量化噪声的增加,因此放大系数M的确定需要依据ZOOM ADC的转换精度和工艺失配等情况进行折中考量。

在整体输出结果中,SAR ADC的输出为高位,提供参考电压范围;Sigma Delta调制器的输出为低位,保证模数转换的精确度。因此ZOOM ADC整体的线性度只与Sigma Delta调制器的线性度有关。对于调制器来说,输入信号幅度越小越容易达到更高的线性度,SAR ADC的存在恰好降低了Sigma Delta调制器的等效输入信号幅度,因此使得系统对Sigma Delta调制器线性程度的要求得以下降。

2 电路设计

由ZOOM ADC的原理可知,SAR ADC的分辨率越高,Sigma Delta调制器的参考电压范围越小,取得的分辨率越高。但SAR ADC的转换时间与分辨率成正比,一味地提高SAR ADC的分辨率会导致Sigma Delta调制器的参考范围变化缓慢无法跟上输入信号变化的速度,导致过载[10]。为了避免该问题,设计过程中需保证在确定输入频率fin下输入信号始终处于参考范围内。对于一正弦波输入,信号变化最快的情况发生在信号与X轴交点处,此处正弦波信号斜率最大。对于在电源电压Vfull,scale内的满摆幅正弦信号来说,在采样率为fsample,SAR的N位SAR ADC的转换周期内,电压变化量为:

参考电压范围为:

需保证输入信号变化量需小于参考范围,利用式(5)和(6)两式,得到:

根据Burak Gnen 等[11]提出的输入信号频率fin与SAR ADC的转换位数N和放大系数M的关系,本设计选取N=5、M=3即可符合设计要求。

本系统采用的SAR ADC实际电路结构如图3所示。采用电荷重分配式全差分结构,采样部分与DAC共用二进制电容阵列[12-13],为保证粗量化过程中的噪声和失配小于1LSB,单位电容取值66fF。SAR ADC每次转换周期内先后完成采样、逐次比较和输出数字结果,在每次转换完成后输出的转换结果用来更新Sigma Delta调制器的参考电压范围。

ZOOM ADC的整体转换精度由SAR ADC 的转换位数N、放大系数M和Sigma Delta调制器的调制精度共同决定,在前两者已经确定的情况下Sigma Delta调制器的调制精度取决于环路滤波器阶数L、量化器位数和过采样率OSR。由于缩放操作减小Sigma Delta调制器输入范围已经大幅降低量化噪声,量化器位数选择一位即可满足要求。为保证调制器达到最佳的噪声整形效果,需要保证信号带宽内的量化噪声小于电路热噪声[14],通过系统级仿真,确定Sigma Delta调制器选取三阶CIFF结构,OSR为100,可满足系统指标要求。

Sigma Delta调制器的实际电路结构如图4所示,其中采样电路和DAC电路复用电容阵列,输入端采样电容值的选取直接决定了KT/C噪声的大小和电容失配带来的误差大小[15]。ZOOM ADC没有作差计算的过程,它的热噪声水平直接依赖于Sigma Delta调制器的调制精度和KT/C噪声。依据所知的工艺参数本设计采样电路中单位电容值选取为0.5pF,总的采样电容值为16pF,满足了噪声与失配的设计要求。由于调制器具有噪声整形作用,第二级、第三级积分器的采样电容选取并不严苛,本设计中分别选取为0.6pF和0.2pF。

调制器输入信号范围的缩小,使得其中积分器所采用运放的增益和摆率等性能指标得以降低[16]。为了进一步提高ZOOM ADC的能量效率,采用一种高能量效率的全差分运放结构来实现环路滤波器[17],如图5所示。该运放基于反相器结构,电流源MOS管决定了OTA的静态电流;共源共栅MOS管用来提高增益;共模反馈电路用来稳定输出共模电平。考虑调制器的噪声整形作用,第一级积分器中运放性能指标对系统影响最大,系统仿真确定第一级运放增益需大于60dB,信号带宽需大于35MHz,即可满足设计要求。由于调制器对第二级和第三级积分器的噪声整形作用,降低了对第二级和第三级运放的性能要求,本设计中三级运放采用同种结构,降低后两级运放的静态电流以进一步降低功耗。

ZOOM ADC的缩放操作使得比较器输入端的信号幅度显著减小,因此需要提高比较器的分辨率。本设计采用了具有预放大功能的动态锁存比较器[18,19],其中锁存比较器电路结构如图6所示。输入信号首先被预放大器放大,其输出再经过锁存放大器完成对输入信号的比较,通过SR锁存器锁存当前周期比较结果。该结构将负指数特性的预放大器和正指数特性的锁存比较器结合,具有更小的响应时间,使得整个比较器的延迟降到最低,能够在系统时钟下完成对输入信号的高速比较。

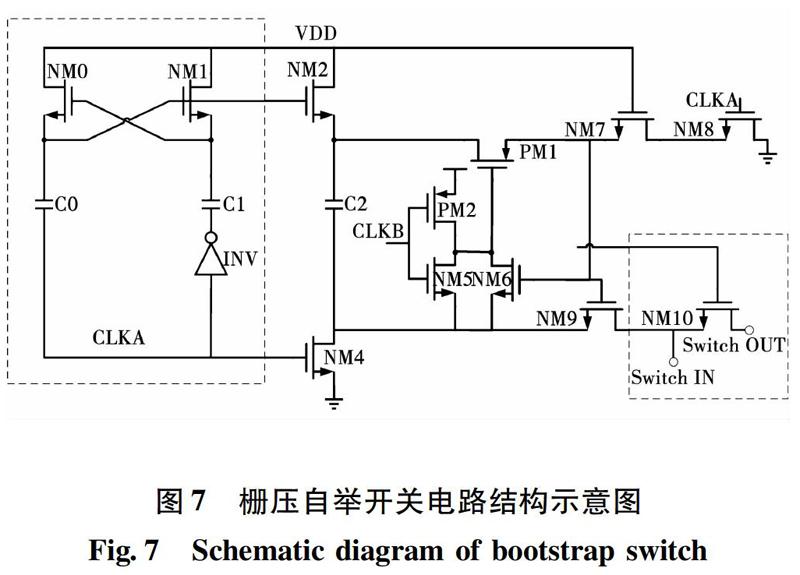

为了提高采样保持电路的线性度,本设计的采样开关使用栅压自举开关结构[20-21],电路结构如图7所示,电荷泵结构用于产生倍增电压,在时钟切换下,保持开关管的栅源电压约等于VDD,使导通电阻几乎与输入信号无关,从而抑制开关电路引入与输入信号有关的谐波失真。电路设计中需要注意开关管的尺寸选取要在导通电阻的数值与寄生电容间进行折中。

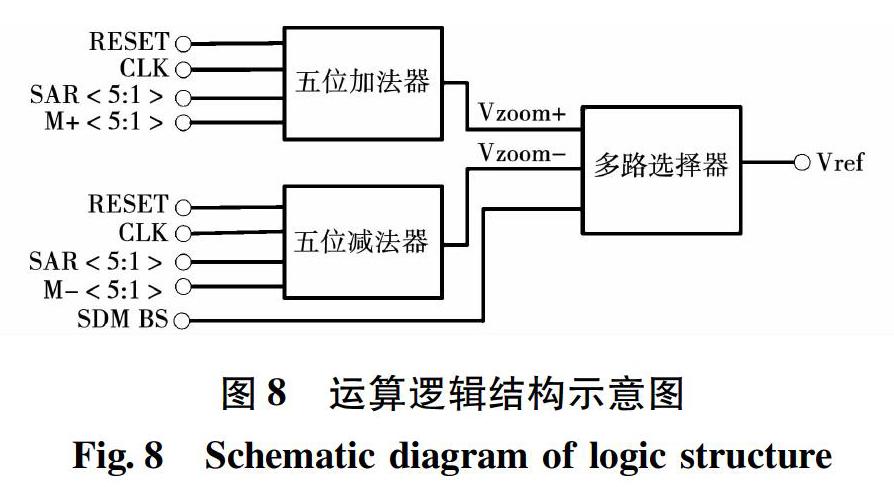

系统中的运算逻辑结构如图8所示。SAR ADC产生的五位数字输出与五位的放大系数M同时进入五位加法器、五位减法器,分别得到处理后的参考电压Vzoom+和Vzoom- 。这两个参考电压进入二选一多路选择器,由Sigma Delta调制器输出的数字码流作为多路选择器控制信号,高位码流选择Vzoom+,低位码流选择Vzoom-,完成Sigma Delta调制器参考电压范围的缩放操作。其中,RESET和CLK分别作为复位信号和时钟信号。

3 仿真结果

通过系统级仿真确定各单元电路的性能指标后,采用0.35μm工艺,对上述ZOOM ADC的电路结构进行设计,采用5V单电源供电,并添加频率为10KHz,峰峰值为4V的差分正弦输入信号,进行指标仿真。

首先对SAR ADC进行瞬态仿真,仿真结果如图9所示,图中连续曲线为SAR ADC的输入模拟信号,阶梯状曲线为模数转换得到的数字信号还原后的模拟电平。对输出模拟电平信号按照SAR ADC的采样频率取点做频谱分析可得到SAR ADC的频率响应如图10所示,计算得到该SAR ADC的输出有效位数为4.26位,能够完成对输入信号的五位粗略转换,为后面的Sigma Delta调制器提供准确的参考电压范围。

其次,对固定参考电压范围的Sigma Delta调制器进行电路仿真,对瞬态仿真得到的数字码流进行FFT变换,得到输出结果的频率响应如图11所示。在采样点间隔10Hz的条件下,噪底约为-110dB,100Hz带宽范围内信噪比约为96dB,符合设计预期。

最终将以上两部分与逻辑运算电路结合,对ZOOM ADC进行整体仿真。逻辑运算电路处理后的仿真结果如图12所示,可以看出逻辑运算电路输出为多位码流,这与上文的分析结果相一致。该多位码流的频率响应如图13所示,对于10kHz中心频率的模拟输入信号,在采样点间隔10Hz的条件下,整体噪底在-140dB附近,经过计算在9950Hz到10050Hz的100Hz信号带宽范围内动态范围达到124dB,满足动态范围大于120dB的指标要求。在5V的单电源供电电压下,核心电路平均电流功耗仅为3.7mA,满足高能量效率要求。

4 结 论

为了更好的将MEMS陀螺传感器应用于便携式设备中,本论文设计了MEMS陀螺仪接口电路中ZOOM型复合结构ADC。利用SAR ADC产生远小于电源电压的参考电压范围辅助Sigma Delta 调制器进行模数转换,在实现对陀螺仪检测信号高精度转换的同时,相比传统高精度ADC显著提升能量效率。本设计基于0.35umBCD工艺,完成了电路的设计与仿真。结果表明电路性能满足设计要求,适用于便携式高精度陀螺传感器应用。

参 考 文 献:

[1] 卞金洪, 王吉林, 周锋, 高精度压力传感器中温度补偿技術研究[J]. 哈尔滨理工大学学报, 2011, 13, (6):55.

BIAN Jin-hong, WANG Ji-lin, ZHOU Feng. Research of Temperature Compensation on High Accuracy Pressure Sensors [J]. Journal of Harbin University of Science and Technology, 2011, (6): 55.

[2] 李巍, 满春涛, 孙晓波, 等.基于D-最优的半球谐振陀螺仪误差参数辨识研究[J], 哈尔滨理工大学学报, 2017, 22(2):34.

LI Wei, MAN Chun-tao, SUN Xiao-bo, et al. Research on Test Plan of Hemispherical Resonator Gyros ErrorModel Coefficients based on D-optimal Criterion [J]. Journal of Harbin University of Science and Technology, 2017(2):34.

[3] CHAE Y, SOURI K, MAKINWA K A A. A 6.3 μW 20 Bit Incremental Zoom ADC with 6 ppm INL and 1 μV Offset[J], IEEE J. Solid-State Circuits, vol. 48, no. Dec. 2013, 12:3019.

[4] GNEN B, SEBASTIANO F, vELDHOVEN R. van, et al. A 1.65 mW 0.16 mm2 Dynamic Zoom ADC with 107.5 dB DR in 20 kHz BW[C]// Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, San Francisco, CA, USA, 2016: 282.

[5] 趙小松. 基于多位量化Sigma-Delta调制器的设计与性能优化[D].哈尔滨:哈尔滨工业大学, 2018.

[6] OH S, JUNG W, YANG K, et al. 15.4 b Incremental Sigma-delta Capacitance-to-digital Converter with Zoom-in 9 b Asynchronous SAR[C]// IEEE Symp. VLSI Circuits Dig, 2014:1.

[7] AGAH A , VLEUGELS K , GRIFFIN P B , et al. A High-Resolution Low-Power Incremental Sigma-Delta ADC With Extended Range for Biosensor Arrays[J]. IEEE Journal of Solid-State Circuits, 2010, 45(6):1099.

[8] 卢宇潇. 髙速低功耗逐次逼近式ADC研究与实现[D]. 上海:上海交通大学, 2014.

[9] 宋孝立. 16位1MS/s CMOS SAR A/D转换器设计及校准技术[D]. 上海:西安电子科技大学, 2014.

[10]闫冬. 数字陀螺Sigma-Delta调制器的设计[D].哈尔滨:哈尔滨工业大学, 2016.

[11]GNEN B, et al. A Dynamic Zoom ADC with 109-dB DR for AudioApplications[J]. IEEE J. Solid-State Circuits, 2017,52(6):1542.

[12]PROMITZERG. 12-bit Low-Power Fully Differential Noncalibrating Successive Approximation ADC with 1MS/s[J]. IEEE J. Solid-State Circuits, 2001,36(7):1138.

[13]NAVEEN Verma, Anantha P. Chandrakasan. A 25μW 100kS/s 12b ADC for Wireless Micro-Sensor Applications[C]// IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig, 2006:222.

[14]蔡俊,徐美华,冉峰. 10 位逐次逼近型 A/D转换器的芯片设计[J]. 半导体技术, 2004, 29(4): 73.

CAI Jun, XU Mei-hua, RAN Feng. Design of a 10Bit Successive Approximation A/D Converter[J]. Semiconductor Technology, 2004, 29(4): 73.

[15]PHILLIP E. Allen,DOUGLAS R. HOLBERG. CMOS模拟集成电路设计[M]. 2版. 北京:北京电子工业出版社, 2005.

[16]曹一江, 王振群, 陈建春, 等. 用于低功耗 A/D 转换器的运算跨导放大器设计[J]. 哈尔滨理工大学学报, 2010, 15(2):84.

CAO Yi-jiang, WANG Zhen-qun, CHEN Jian-chun, et al. Design of an OTA in a Low Power A/D Converter[J]. Journal of Harbin University of Science and Technology, 2010, 15(2): 83.

[17]CHAE Y, HAN G. Low Voltage, Low Power, Inverter-based Switched Capacitor Delta-sigma Modulator[J] IEEE J. Solid-State Circuits, 2009,44(2):458.

[18]冯奕翔, 李哲英. 高速高精度比较器的设计[J]. 北京联合大学学报(自然科学版), 2011, 25(3): 25.

FENG Yi-xiang, LI Zhe-ying. Design of High Speed and High Precision Comparator [J]. Journal of Beijing UnionUniversity(Natural Science Editon), 2011, 25(3): 25.

[19]吳蓉, 严晓浪. 一种高精度动态CMOS比较器的设计与研制[J]. 电路与系统学报, 2007 (4): 119.

WU Rong, YAN Xiao-lang. A Precise Dynamic CMOS Comparator [J].Journal of Circuits and Systems, 2007 (4): 119.

[20]WEGMANN G, VITTOZ E A, Rahali F. Charge Injection in Analog MOS Switches[J]. IEEE Journal of Solid-State Circuits, 1987, 22(6): 1091.

[21]SHEU B, SHIEH J H, Patil M. Modeling Charge Injection in MOS Analog Switches[J]. IEEE Transactions ON Circuits and Systems. 87, 34(2): 214.

(编辑:温泽宇)