基于DSP的中断冲突避免机制的研究与实现*

刘 蓓,郑 林,蒙 瑰,徐 暠,郗洪柱

基于DSP的中断冲突避免机制的研究与实现*

刘 蓓,郑 林,蒙 瑰,徐 暠,郗洪柱

(航天长征火箭技术有限公司 北京 100076)

针对基于DSP芯片TMS320C6701的嵌入式软件系统设计过程中常见的中断冲突问题,提出相应的解决方法和简单有效的避免机制。通过将周期性中断改为主循环查询模式、将DSP系统计时由定时器中断改为FPGA同步计时等方式,使系统中多个中断设计简化为一个中断,避免中断间的冲突。针对中断和主程序间的访问冲突,通过在主程序中关中断等方式,避免共享资源访问冲突。针对DSP系统和外部总线的访问冲突,通过约定接口的通信协议,避免时序冲突。通过静态分析和动态长周期测试验证,方法有效避免了中断冲突,实现简单;针对不同冲突机制,措施灵活。设计已应用于星载相关设备,也可推广至其他嵌入式软件系统使用。

DSP;FPGA;1553B总线;中断冲突

引 言

DSP芯片TMS320C6701具有很好的抗辐照特性,适用于深空探测和长时间在轨飞行,在运载火箭上面级领域和星载领域得到广泛应用[1]。基于DSP的星载嵌入式软件多为中断驱动型,即主程序加中断的程序结构,属于非常典型的实时并发软件,要求能够实时处理各种随机任务并完成多种计算活动[2]。而在DSP中断系统的设计和实现过程中很容易引入诸如中断嵌套错误、现场保护错误、开关中断时机错误等软件错误;一旦由于中断造成了程序错误,则会导致一系列不易追踪的严重软件故障,且大多问题对系统来说常常是致命的,严重时可导致系统或软件失效[3,4]。由于航天型号软件对可靠性和安全性有很高的要求,提出针对中断冲突的解决方法和避免机制对于提高整个软件的安全性具有重要意义[5]。

多数文献对中断冲突的研究集中在检测方法上,主要侧重于对软件中存在的中断冲突的测试和发现。本文对基于DSP的嵌入式软件系统中常见的中断冲突,从软件设计和编码角度出发,提出有效改进措施,避免冲突发生。

1 系统架构

基于DSP的嵌入式软件系统采用DSP+FPGA控制方式。FPGA周期性采集传感器原始测量数据和电压遥测数据,并通过HPI(Host-Port Interface)接口发送给DSP;DSP完成传感器数据处理和测量结果计算,并根据1553B总线命令完成与上级总线控制器BC(Bus Controller)的原始测量数据和遥测信息传输,实现系统代码在线升级等功能。

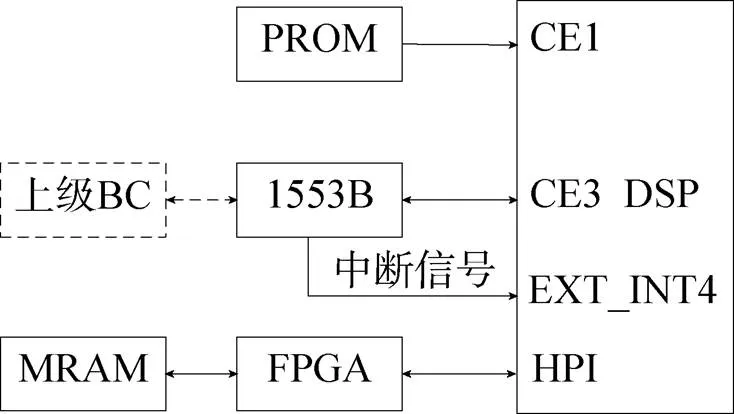

DSP系统的外部接口图如图1所示,接口功能如下:

图1 DSP外部接口

① DSP通过EMIF(External Memory Interface)接口的CE1口与可编程只读存储器PROM相连,PROM用于存放程序代码。

② DSP通过EMIF接口的CE3口与1553B总线芯片B65170相连。DSP芯片可通过1553B总线接收上级总线控制器BC发送的总线指令和更新代码;也可通过1553B总线向上级BC发送设备的数据和状态信息。

③ DSP通过HPI接口与FPGA相连,由FPGA完成对磁阻式掉电非易失存储器MRAM的读写访问,实现对设备更新程序、更新标识及复位标识的保存工作。FPGA通过HPI接口周期性发送原始测量数据给DSP。

2 中断冲突

基于DSP的嵌入式软件系统在设计过程中,常见的中断有:

① FPGA周期性发送的传感器原始测量数据中断和电压遥测数据中断。其中,传感器原始测量数据中断0.2s一次,电压遥测数据中断1s一次。

② 定时器中断,用于系统计时,定时周期25μs。

③ 接收1553B总线命令中断,为随机中断。

由于中断触发的随机性和不确定性,中断与中断间、中断与主程序之间都有可能发生时序冲突。对于不受DSP控制的外部触发中断,在中断初始化过程中,若初始化流程不当,可能会导致系统始终无法响应外部触发中断,造成系统功能的失效。

系统中的中断冲突可分为时序冲突和共享资源冲突。其中,时序冲突有初始化冲突、中断间冲突、DSP与1553B总线访问冲突;共享资源冲突又可细分为全局变量访问冲突、内存地址访问冲突和外部接口访问冲突等。

2.1 时序冲突

2.1.1 初始化冲突

DSP系统中三个中断的启动机制如下:

① FPGA由DSP发送控制信号以开启原始测量数据和电压遥测数据采集,然后周期性发送原始测量数据、电压遥测数据和中断信号给DSP。

② 定时器中断的开启、暂停和停止都由DSP软件进行控制。

③ 1553B中断由上级BC触发,对于DSP系统而言属于随机信号。上级BC通过1553B总线发送总线命令给1553B芯片B65170,芯片B65170在完成与上级BC的信息交互后,发送1553B中断信号(低电平信号)给DSP的外部中断接口。DSP的外部中断由下降沿触发。DSP通过外部中断接口接收到1553B中断后,需通过读B65170的中断状态寄存器以清除1553B中断信号。若在DSP对外部中断接口进行初始化使能过程中,接收到1553B中断信号,由于DSP的外部中断接口尚未使能,且初始化过程中有对DSP的外部中断标识进行清零,就会使1553B中断信号的状态与DSP的外部中断标识不一致,导致1553B中断信号始终保持低电平,无法进行下降沿触发,后续整个系统将始终无法收到1553B中断,与上级BC无法进行正常通信。

FPGA中断和定时器中断都由DSP开启,初始化过程中不存在时序冲突。而1553B中断由外部设备触发,具有随机性,在初始化过程中存在冲突的可能。为避免冲突造成系统功能失效,在1553B中断初始化过程中,需对1553B总线进行清中断,具体初始化流程如图2所示。在开全局中断后,进行清1553B中断操作,可使系统在能够响应和处理1553B中断时,1553B中断处于可触发状态。同时,由于上级BC只有在轮询到有效的自检测字后,才会发送有效中断指令给DSP系统,不会存在先开全局中断,再清除1553B中断后,造成有效中断指令丢失的情况。

因此,在对外部中断进行初始化时,要注意时序冲突问题,保证外部中断的随机触发,不会使中断信号被锁死,造成系统功能失效。

图2 1553B中断初始化流程

2.1.2 中断间冲突

DSP芯片TMS320C6701接收到中断,在进行中断处理时,硬件会先关闭全局中断,禁用其他可屏蔽中断。

基于DSP的嵌入式软件系统有三个可屏蔽中断,在运行过程中可能会出现如下情况:

在FPGA中断或1553B中断处理过程中,若定时器中断被触发,则会被屏蔽掉;定时器周期为25μs,而其他中断处理时间若大于25μs,就会造成漏中断的现象,造成系统计时误差。

为避免出现定时器漏中断的情况,需进行中断嵌套。在进入其他中断服务程序时,需开全局中断,使能定时器中断,允许定时器中断打断其他中断服务程序。在中断嵌套时,一次中断时间可能是两个中断或三个中断服务程序运行时间的累加和,在进行程序时域分析时应注意。同时,在允许被打断的中断服务程序中,需做好对中断返回地址和全局中断使能状态的保存,防止中断被打断后中断返回地址和全局中断使能状态丢失,造成程序运行错误。

由于系统存在三个可屏蔽中断,FPGA中断与1553B中断间、嵌套后的FPGA中断与1553B中断间都可能存在时域冲突,且由于加入中断嵌套后,对时域冲突的分析更加复杂。为简化系统设计,避免中断冲突,利用三个中断的特性,将三个中断简化为一个中断。具体如下:

① FPGA中断的最短周期为0.2s,主程序循环一次的时间小于50ms。通过在主循环中对FPGA中断信号进行轮询,可满足FPGA中断的时序要求,且FPGA周期发送的传感器原始测量数据采用乒乓缓存的方式,不会出现发送给DSP的原始数据由于DSP处理不及时被FPGA实时采集的数据覆盖的现象。利用乒乓缓存模式,还可提高FPGA的采样速率,保持数据的连续性和周期性。

② 定时器中断主要用于系统计时,系统的时间分辨率为25μs;因此,定时周期也为25μs。系统采用DSP+FPGA控制方式,为避免定时器频繁中断,影响测量数据处理周期,且为避免中断嵌套可能带来的时序冲突,利用FPGA并行进程的优势,采用FPGA进行系统时间的计时;DSP提供系统时间的定期更新数据;在需要对原始测量数据、遥测数据进行打时间标时,从FPGA实时读取系统时间。

由于系统时间采用6字节进行存储,DSP在向FPGA发送更新时间和读取时间时,应注意读写时序被打断的情况。为避免时间信号在读写过程中被打断,造成系统计时错误,在DSP向FPGA发送更新时间时,FPGA接收到完整的6字节数据后,才对时间数据进行锁存和使用;在DSP从FPGA读取系统时间时,FPGA在接收到第一个读信号后,即锁存整个6字节的时间数据,避免由于中断影响造成读取时间错位的情况发生。

③ 1553B中断为外部中断,由上级总线控制器BC启动,对于DSP系统而言属于随机中断。1553B中断主要用于完成设备与上级系统间的通信;设备通过1553B总线发送原始测量数据、测量结果、设备健康状态给上级系统;上级系统通过1553B总线发送总线指令给DSP,完成设备复位、恢复出厂设置、程序在线更新等功能。由于1553B中断为随机中断,发送周期不确定,若出现漏中断或中断无响应情况,会对系统造成较大影响。因此,1553B中断仍采用中断触发方式,对接收到的中断进行实时处理。

通过将FPGA中断改为由主程序进行周期性轮询,将定时器计时中断改为由FPGA进行系统计时,简化为只有一个外部1553B中断,系统不再有FPGA中断和定时器中断,使系统不存在中断与中断间冲突的可能。

针对1553B中断,若前后两次中断的触发时间小于中断服务程序的执行时间,则会出现漏中断或中断处理不及时情况。为避免该情况,中断服务程序的执行时间应尽可能短。本系统中最短的总线消息为发送方式代码矢量字,理论最短时间为68μs(方式指令+状态字+数据字+响应时间+消息间隔=20μs+20μs+20μs+4μs+4μs)。1553B中断服务程序的执行时间目前设置为20μs左右,可避免由于中断服务程序运行时间过长,造成漏中断的情况发生。

2.1.3 DSP与1553B总线访问冲突

1553B芯片B65170内部RAM的数据区可由DSP系统和1553B总线共同进行读写访问。接收、发送和广播查询表可由DSP进行读写访问;1553B总线通过访问数据区可对设置为循环缓存区的接收、发送和广播查询表中的地址指针进行修改。因此,DSP系统和1553B总线在对芯片B65170内部RAM的数据区和查询表进行访问时,可能存在时序冲突;由时序冲突引发的问题最终可表现为内部RAM区的数据冲突,具体表现如下:

① 在1553B总线对芯片B65170内部RAM数据循环缓存区进行读写访问时,对应查询表的地址指针会随之更改;此时若DSP系统对查询表中的地址指针进行初始化,就会造成1553B总线读取数据重复、错位,写数据被覆盖、丢失等现象的出现。

② 在1553B总线对芯片内部RAM数据区进行读原始测量数据、遥测数据等操作时,若DSP系统进行对应数据区的写入,就会造成1553B总线读取的数据为新旧数据包的组合,造成数据丢帧现象的出现。

③ 在1553B总线对芯片内部RAM数据区进行写更新代码等操作时,若DSP系统读取不及时,就会造成接收数据新旧结合、接收数据校验不正确或接收数据丢帧等现象的出现。

由于DSP对芯片B65170内部RAM区的操作和1553B总线的读写访问由不同的CPU系统控制,可通过约定接口的通信协议,避免DSP和1553B总线间的访问冲突。具体措施如下:

① 针对查询表中循环缓存区地址指针写冲突问题,通过约定同一总线命令发送的最小间隔时间,可解决该问题。如:1553B总线读原始数据周期为0.2s,读遥测数据周期为1s,写更新代码的周期大于1s;而DSP系统是在1553B总线完成相应读写操作、发送中断后,才对循环缓存区地址指针进行写操作,完成指针初始化。DSP在接收到中断后,在中断服务程序中完成指针初始化,执行时间约需20μs,远小于总线命令的发送周期,不会与下一周期发送的总线命令产生读写冲突。

通过约定1553B总线命令的访问周期以及DSP系统的访问时机和访问时间,即可避免两者之间的访问冲突。

② 针对1553B总线读操作和DSP系统写操作冲突,可通过增加握手标识解决该问题。如:将方式代码矢量字设置为握手信号,1553B总线在读取到矢量字有效标识后,开启对原始测量数据、遥测数据的读操作,读完成后,发送中断给DSP,DSP接收中断后,在中断服务程序中清矢量字有效标识。DSP只有在矢量字标识无效且有原始数据满足发送条件时,才会对总线芯片内部RAM区进行写数据操作。

通过设置握手信号,以及将1553B总线和DSP系统访问的条件设置为互斥状态,避免两者一读、一写产生访问冲突。

③ 针对1553B总线写操作和DSP系统读操作冲突,可通过约定总线指令的发送周期,以及DSP系统的处理周期来避免两者之间的读写冲突。如:1553B总线发送程序更新代码的周期大于1s,而DSP系统接收到一次总线数据并完成处理的时间小于50ms,这样就可避免由于DSP系统处理超时造成DSP在进行总线数据接收处理时又有新的总线数据发送,导致出现数据被覆盖及丢失的情况。

1553B总线指令的接收和保存在中断服务程序中进行,执行和处理在DSP主程序中进行。DSP系统通过保证主程序循环一次的运行时间小于总线指令的最小发送间隔时间,如此可避免总线指令处理超时等情况的发生。

通过约定接口的通信协议,可避免由不同CPU控制的DSP芯片和1553B总线对同一内存区访问的冲突。

2.2 共享资源冲突

系统经简化设计后,只有一个外部1553B中断,因此,系统产生中断冲突的风险就存在于1553B中断和主程序之间。

为减少中断服务程序的执行时间,避免执行时间过长,造成漏中断的现象,通常中断服务程序只对1553B总线发送的命令进行简单的校验和记录。总线命令的处理在主程序中进行。主程序循环一次的时间小于50ms,而所有需处理的1553B总线命令周期均大于50ms。通过主程序处理能保证1553B总线命令处理和接收的及时性,避免出现漏中断情况。

1553B中断和主程序之间可能存在共享资源冲突,常见的共享资源冲突有全局变量访问冲突、内存地址访问冲突和外部接口访问冲突。

2.2.1 全局变量访问冲突

系统中主程序和1553B中断服务程序都进行写操作的全局变量有接收1553B总线命令计数和接收广播时间码标识。

① 1553B中断服务程序在接收到总线命令后,会对接收1553B总线命令计数进行加1操作;主程序在完成总线命令处理后,若已处理和接收总线命令个数不小于缓存区最大数,则对已处理和接收总线命令计数减去缓存区最大数,防止数据溢出。

为避免主程序和1553B中断服务程序对接收1553B总线命令计数的修改冲突,在主程序对接收1553B总线命令计数进行修改时需进行关中断操作。

② 1553B中断服务程序在第一次接收到上级BC发送的广播时间码后,将接收广播时间码标识置为有效;主程序在检测到接收广播时间码标识有效后,初始化时间标识,开启对程序周期性检测;为防止标识被打翻,主程序对接收广播时间码标识进行大数判决,将被打翻的标识进行修正。

为避免主程序和1553B中断服务程序对接收广播时间码标识的修改冲突,增加一个全局变量标识,该标识在中断服务程序中,只要接收到广播时间码,即置为有效;在主程序中,对该标识进行判别,若该标识有效且接收广播时间码标识为无效,置接收广播时间码标识为有效,且周期性对接收广播时间码标识进行大数判决。通过该方法,可解决主程序和1553B中断服务程序间的写冲突。

2.2.2 内存地址访问冲突

方式代码矢量字对应的数据字保存在芯片B65170内部RAM 0x120地址中,主程序和1553B中断服务程序对该内存地址都有写操作。方式代码矢量字用于标识原始测量数据、遥测数据是否准备好;上级读取到方式代码矢量字有效标识后,对数据进行读取,读取结束,发送中断,DSP接收中断后,在中断服务程序中将方式代码矢量字置为无效;主程序在得到有效数据后,会重新将方式代码矢量字置为有效。由于方式代码矢量字包含对原始测量数据、遥测数据和接收注入数据等数据的标识,因此主程序和1553B中断服务程序间存在写冲突。

内存地址访问冲突和全局变量访问冲突性质一致,也可通过在主程序中关中断的方式,解决两者间的写冲突。

在主程序中进行关中断操作,应注意关中断的时间,防止出现由于关中断而造成漏中断的现象出现。本系统中关中断时间都在μs量级,可避免关中断超时情况。

2.2.3 外部接口访问冲突

由于系统由FPGA进行时间计时,DSP在1553B中断服务程序中接收到广播时间码后,将广播时间码转发给FPGA,由FPGA进行时间修正。在主程序中,DSP完成初始化后,会发送时间码给FPGA,以开启FPGA的数采功能。由于主程序和1553B中断服务程序都对FPGA接口进行写操作,因此可能存在冲突。

由于主程序只对FPGA接口进行一次写时间码操作,为避免主程序和中断服务程序间的冲突,将主程序中写时间码操作放在1553B中断使能之前进行。由于中断使能所需的时间为μs级,在写时间码启动FPGA数采功能后,FPGA至少需要0.2s发送测量数据,不影响DSP对FPGA发送数据的及时接收。因此,将主程序中写时间码操作放在中断使能之前,可避免中断引起的访问冲突,还可保证FPGA发送数据的正常接收。

根据存在中断冲突的共享资源本身的特性,可通过增加全局变量、在主程序中关中断以及改变写操作的时机等方式避免中断和主程序间的共享资源冲突。

3 未用中断处理

基于DSP的嵌入式软件系统通过查询中断向量表进行中断的处理。中断向量表包含16条中断,有复位中断、不可屏蔽中断、可屏蔽中断及保留位。在本系统中,复位中断跳转到二次加载程序中,使用可屏蔽的外部中断4作为1553B中断(示于图1);其他未用中断若不作处理,则在程序指针误跳入中断向量表未用中断进程时,程序运行状态将不可控,可能出现异常情况,造成系统混乱。

为增加程序可靠性,保证程序在误入未用中断后仍能正常跳出中断,不影响系统的正常运行,在未用中断的中断服务程序中,禁止未用中断的中断使能并清除对应的中断标识,使程序能正常退出中断服务程序的同时,保证下次不再进入未用中断。

4 结束语

针对基于DSP的嵌入式软件系统中常见中断冲突,从时序冲突和共享资源冲突两方面进行研究和分析,根据产生机理不同,提出了灵活有效的中断冲突避免机制。对于系统未用中断,提出相应保护机制。经验证,针对不同冲突机制,该方案实现简单、措施灵活,目前已应用于星载相关设备,也可推广至其他嵌入式软件系统使用。

[1] 霍宏, 李兰兰, 刘卫东, 等. 基于TMS320C6701的飞行软件加载模式研究[J]. 航天控制, 2014, 32(1): 85–88. HUO Hong, LI Lanlan, LIU Weidong, et al. Research of three-level loading mode based on TMS320C6701 for the flight software[J]. Aerospace Control, 2014, 32(1): 85–88.

[2] 黄晨, 董燕, 王小丽, 等. 基于表格的中断数据冲突静态分析方法[J]. 空间控制技术与应用, 2016, 42(5): 57–62. HUANG Chen, DONG Yan, WANG Xiaoli, et al. Static analysis method for table-based interruption data conflictions[J]. Aerospace Control and Application, 2016, 42(5): 57–62.

[3] 杨芳, 齐璇, 董丽, 等. 嵌入式软件中断系统资源冲突检测技术研究[J]. 计算机工程与设计, 2010, 31(23): 5036–5059. YANG Fang, QI Xuan, DONG Li, et al. Research of interrupt system resource conflict detection technology for embedded software[J]. Computer Engineering and Design, 2010, 31(23): 5036–5059.

[4] 陈睿, 杨孟飞. 基于编码规则的中断数据访问冲突检测方法[J]. 空间控制技术与应用, 2017, 43(3): 59–65. CHEN Rui, YANG Mengfei. Coding rule based interrupt data race detection method[J]. Aerospace Control and Application, 2017, 43(3): 59–65.

[5] 侯成杰. 航天器C51语言软件中断资源冲突分析方法[J]. 空间控制技术与应用, 2015, 41(4): 58–62. HOU Chengjie. Interrupt resource conflict analysis for spacecraft C51 language software[J]. Aerospace Control and Application, 2015, 41(4): 58–62.

Research and implementation of interrupt conflict avoidance mechanism based on DSP

LIU Bei, ZHENG Lin, MENG Gui, XU Hao, XI Hongzhu

(Aerospace Long March Lauch Vehicle Technology Co. Ltd., Beijing 100076, China)

To solve the interrupt conflict problems in the program based on the TMS320C6701 DSP embedded software system, the solution and valid avoidance mechanism are proposed. To avoid the conflict between the interrupts, there are some methods by which the system can be configured with just one interrupt instead of multiple interrupts, such as using polling mode replaced the periodic interrupt, the system time counting by FPGA instead of DSP timer counting interrupt. The interrupt conflict between the interrupt service routine and the main program could be avoided by disabling the interrupt in the main program. By ensuring reliable interface communication protocol logic to avoid the access conflict between the DSP system and the 1553B Bus. It is verified the validity of the interrupt conflict avoidance mechanism by static analysis and dynamic long-periodic test. The design has provided the ultimate flexibility and simplification for a variety of conflicts in the space devices, which could also be applied in other areas.

DSP; FPGA; 1553B Bus; Interrupt conflict

TP311

A

CN11-1780(2020)02-0049-06

载人航天预研(20184112043);民用航天预研(B0104);中国科协青年人才托举工程(2018QNRC001)

2020-03-03

Email:ycyk704@163.com

TEL:010-68382327 010-68382557

刘 蓓 1991年生,硕士,工程师,主要研究方向为嵌入式软件设计。

郑 林 1987年生,硕士,工程师,主要研究方向为光学气体检测。

蒙 瑰 1985年生,硕士,高级工程师,主要研究方向为光学气体检测。

徐 暠 1990年生,硕士,工程师,主要研究方向为传感器软件设计。

郗洪柱 1988年生,博士在读,工程师,主要研究方向为传感器硬件设计。