基于指令逻辑控制的安全CPU架构设计

张助玲,刘 敏,秦焕青,马刘杰

(1.上海航天计算机技术研究所,上海 201109;2.中远海运科技股份有限公司,上海 200135;3.中天安泰(北京)信息技术有限公司,北京 100040)

0 引 言

随着计算机技术和信息技术的快速发展,信息安全越来越受重视,信息安全技术得到不断提升。然而,当前计算机恶意程序数量不断增多,对重要行业关键信息基础设施的威胁不断加剧,信息安全形势较为严峻[1]。中央处理器(Central Processing Unit,CPU)作为计算机的运算核心和控制核心,是保证计算机正常运行和处理相关程序及数据的核心设备。长期以来,尽管CPU的性能得到了很大提升,但其一直只具有对接收的指令进行运算和控制的功能,不能对指令是否有效和安全作出任何判断,并阻止其执行。因此,研制具有自主产权的具有指令逻辑实时控制和安全判断功能的CPU,对于构建安全可靠的计算机信息系统和信息网络而言具有重要意义。

1 当前的CPU安全架构

当有的CPU架构设计加入了安全机制,主要采用分层设计思想和可信设计思想,其中:

1)分层设计思想即将CPU分为ring 0、ring 1、ring 2和ring 3(Intel X86架构)等4种特权级别[2],或用户态和核心态2种安全级别(ARM架构),本质上是实现对指令调度权限的管理和控制;

2)可信设计思想即在CPU的架构设计、测试、量产、封装和执行阶段构建可信计算环境,本质上是构建一个认证体系和动态可信链,与CPU的逻辑实现无关。

1.1 X86 CPU安全架构

Intel和AMD等CPU厂商为配合虚拟技术的应用,都在其CPU中加入硬件虚拟化支持。硬件虚拟化技术不仅能为虚拟技术提供直接支持,而且能提高虚拟效率,提供一种安全CPU机制。VMM(Virtual Machine Monitor)[3]被称为Hypervisor,专指在采用硬件虚拟化技术时创建出的特权层,将其提供给虚拟机开发者,用来实现虚拟硬件与真实硬件的通信和事件处理,其权限的级别高于操作系统权限的级别。图1为Intel CPU架构权限分层,在Intel VT-x虚拟化技术架构中,VMM的权限可视为ring 1级。

由于新增了特权级别“ring 1”,需要有新的指令、寄存器和标志位来实现其功能。因此,硬件虚拟化技术也是一种基于指令调度权限管理和控制的安全机制。

为抵御恶意软件的攻击,Intel TXT(Intel Trusted Execution Technology)技术提供了一系列基于硬件的安全解决方案,支持计算机系统基于TXT的静态可信根和动态可信根,采用静态度量和动态度量技术构建安全可信的软件执行环境,在与硬件虚拟化技术配合应用时,发挥出更强的保护能力。

当Intel TXT技术与Intel VT-x技术相结合时,TXT的静态可信根能实现对Hypervisor的身份验证、数据和参数度量,保证其完整性和授权访问;动态可信根技术可动态地将信任链向后续启动的虚拟机操作系统和应用程序传递,构建动态可信链。

1.2 ARM TrustZone安全技术

ARM TrustZone技术的核心思想是从CPU内核设计开始,将增强系统安全性的措施集成到系统的整体设计中,保证产品不受外部因素的恶意攻击[4]。ARM系统一般基于TrustZone技术构建安全平台。在ARM体系架构中,TrustZone为用户模式和特权模式引入了安全状态标识和判断机制,以决定系统是运行在非安全的“普通”执行环境中,还是运行在安全可信任的“安全”执行环境中。安全监控器控制着“安全”环境与“普通”环境之间的转换。图2为TrustZone模式下2种并行安全环境示意。

1.3 其他安全架构

日本投入大量资金开发了具有过滤功能的安全CPU,并在总线上开发了逻辑分析器。由于技术架构设计存在缺陷,其未能形成有效的CPU安全技术体系。

龙芯、飞腾和申威等国产CPU基本上能满足自主可控要求,但在安全性上采用的是与X86和ARM架构类似的权限管理机制,虽然能实现对指令调度权限的管理和控制,但未能在指令调度和执行过程层面建立CPU逻辑安全机制,尚未开展CPU逻辑控制机制研究。

综上所述,目前的CPU安全设计技术主要是在CPU架构的基础上进行加固和权限管理,或引入部分可信计算技术,虽然能为计算机系统的安全运行提供一定的保障,但尚未实现对CPU指令逻辑的控制。因此,需在CPU内部构建指令逻辑控制单元,将信息安全防御技术从操作系统下沉到CPU内部,为计算机和信息系统提供基础安全平台支撑,抵御恶意攻击。

2 指令逻辑实时控制

在研究CPU指令逻辑控制技术时,需构建CPU指令逻辑控制平台,建立指令安全性判断机制,获取指令安全性判断方法,以实现对CPU指令逻辑实现过程的控制。

2.1 构建CPU指令逻辑控制平台

当前的CPU通常将流水线划分为取指、译码、调度、发射、执行和提交等阶段,其中发射和执行是乱序的,直到提交阶段才能确定指令的顺序和预测结果。提交阶段是指令生效与未生效的临界点,一旦提交成功,指令就会对内存、寄存器和CPU状态等进行改变。要实现对CPU的逻辑控制,需构建CPU流水线逻辑控制平台,实现对上述阶段逻辑实现过程的干预和控制,在提交阶段识别并阻止恶意指令,即通过对流水线进行控制,使CPU的逻辑可控。

2.2 指令安全性判断机制

CPU是开放的系统,所有符合其编码规范的指令,不管是否为恶意指令,都能进入CPU并被执行。由于所有攻击本质上都是用当前的指令逻辑改变后续指令逻辑的过程,因此需建立指令安全性判断机制,在提交之前判断当前的指令是否安全。由于指令提交之后不能更改,需在执行阶段与提交阶段之间增加预提交程序,在提交之前判断该指令是否为恶意指令。

2.3 指令安全性判断方法

计算机运行过程是用代码逻辑处理数据的过程。在此过程中,代码会在CPU执行返回确认之前经过多次重组。对CPU的运行逻辑进行控制的核心是保证代码逻辑重组过程不会被修改,即保护堆栈、内存和逻辑结构等数据不会被篡改。因此,需通过判断当前的指令是否对堆栈、内存和逻辑结构等数据进行修改来判断当前的指令是否安全。

3 CPU安全架构设计

3.1 CPU安全架构总体设计方案

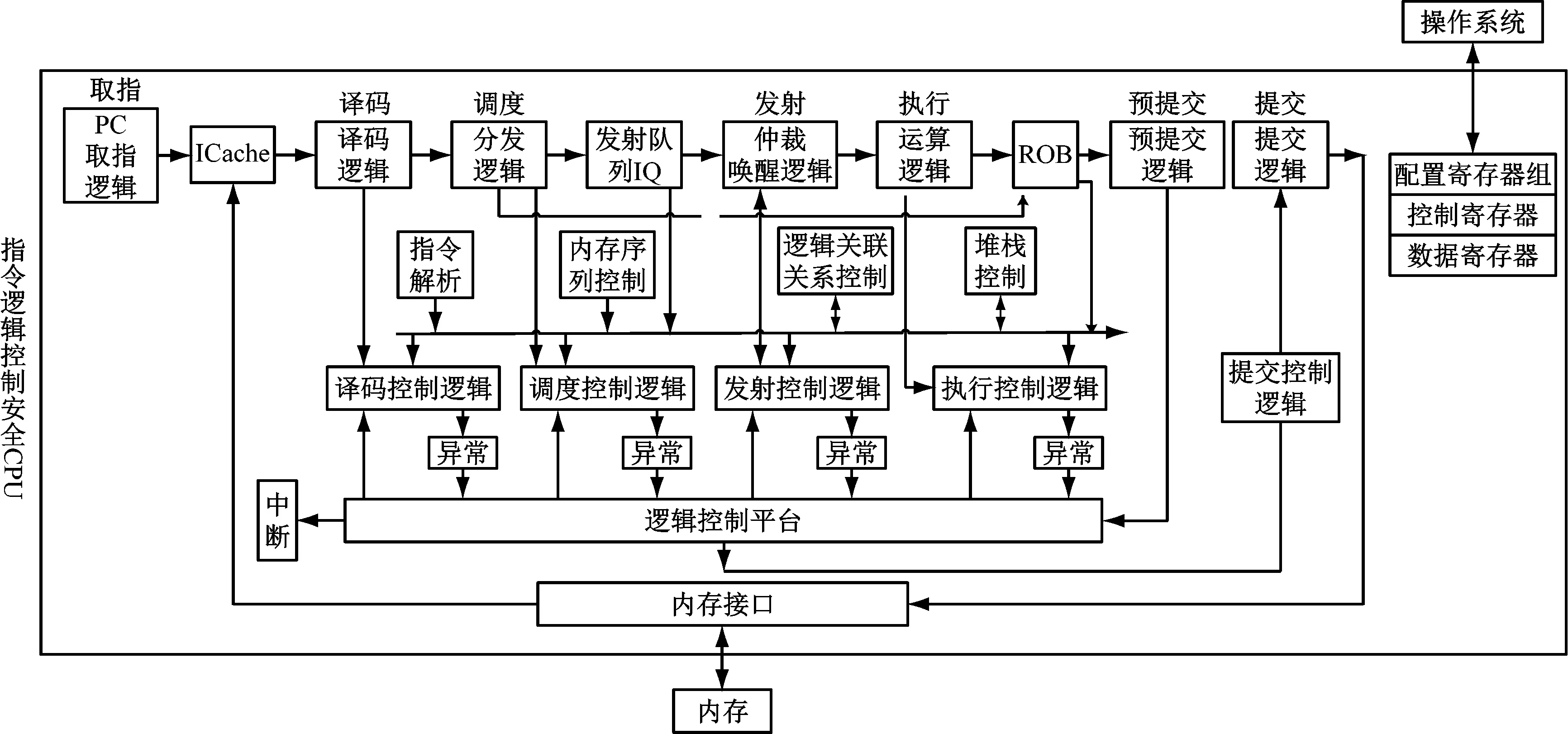

指令逻辑控制CPU安全架构总体设计方案见图3,其中:取指、译码、调度、发射、执行、提交、ICache、发射队列IQ、ROB和内存接口属于基本CPU流水线及部件;预提交、提交控制逻辑、译码控制逻辑、调度控制逻辑、发射控制逻辑、执行控制逻辑、逻辑控制平台、配置寄存器组、控制寄存器、数据寄存器、异常单元和中断单元共同构成指令逻辑控制安全CPU的运行控制平台。

图3 指令逻辑控制CPU安全架构总体设计方案

在CPU中执行指令过程中,指令解析单元、内存序列控制单元、逻辑关联关系控制单元和堆栈控制单元不断更新指令、堆栈、内存和逻辑关联信息。在预提交阶段,指令传输到逻辑控制平台,由其分发给译码控制逻辑、调度控制逻辑、发射控制逻辑和执行控制逻辑,这些逻辑根据指令、堆栈、内存和逻辑关联信息对指令的安全性进行分析判断。若该指令是恶意指令,则相应的控制逻辑向逻辑控制平台报告异常,逻辑控制平台通知提交控制逻辑,阻断该恶意指令的提交,并向操作系统上报中断;若发生了篡改行为,则向逻辑控制平台上报中断,由逻辑控制平台向操作系统上报中断。在判断指令的安全性时,操作系统通过操作配置寄存器组、控制寄存器和数据寄存器,实现对安全CPU的配置及其状态的读取。

3.1.1 译码和调度控制逻辑

CPU首先从指令缓存中获取将要执行的指令,经过译码得到其类型、操作数和地址等信息。译码控制逻辑与指令解析单元一起对该指令信息进行协同分析,判定其是否被非法使用,并作标记。在预提交阶段,逻辑控制平台根据指令标记对该指令进行判断处理,若其被非法使用,则逻辑控制平台通知提交控制逻辑,阻止其提交,并上报中断;否则,逻辑控制平台通知提交控制逻辑正常提交。

在指令调度阶段,分发逻辑将指令写入发射队列IQ和ROB,调度控制逻辑对当前的指令和逻辑关联关系控制单元中的指令进行分析,并生成新的逻辑关联关系。在预提交阶段,调度控制逻辑根据该指令的类型和操作数判断其是否对现有的逻辑关联关系造成破坏,若造成破坏,则逻辑控制平台通知提交控制逻辑阻止其提交,并上报中断。

3.1.2 发射和执行控制逻辑

发射控制逻辑保证在发射阶段,同一个逻辑关联节点指令组中的所有指令都准备就绪之后再送入执行功能部件,使同一个逻辑节点上的指令在一个时间段内执行,减少后续逻辑判断的工作量。

对于访存操作,执行控制逻辑将操作数与内存序列控制单元中的数据相比对,判断保护内存是否被篡改,若被篡改,则通知提交控制逻辑阻止其提交,并触发中断,通知操作系统。

3.1.3 逻辑和提交阶段控制平台

逻辑控制平台是安全CPU运行控制平台的中枢,负责在预提交阶段对指令进行解析,并向其他逻辑分发;接收其他逻辑的反馈结果,并向提交控制逻辑发送指令安全性反馈结果;同时,在出现异常时触发中断。

提交控制逻辑负责接收逻辑控制平台发送的指令安全性返馈结果,若是安全指令,则直接提交,否则阻止提交。

基于上述逻辑控制过程,实现对指令逻辑控制安全CPU每条指令的控制,从而发现并阻止恶意指令的执行,达到防止恶意代码攻击的效果。

3.2 逻辑控制平台技术途径

逻辑控制平台技术实现示意见图4。指令解析单元负责解析预提交指令,分析其携带的指令码和操作数对应的数值;指令分发逻辑负责根据指令码,将指令分为特殊指令和其他指令2类。特殊指令由译码控制逻辑进行分析处理,其他指令由调度控制逻辑、发射控制逻辑和执行控制逻辑进行分析处理。若指令为恶意指令,则将异常信息反馈给逻辑控制平台,由其统一报告给操作系统。指令裁决单元负责对各站台控制单元反馈的结果进行汇总,并将其发送给提交控制逻辑,由其决定该指令是否提交。

图4 逻辑控制平台技术实现示意

4 结 语

本文介绍了现有的CPU安全机制和在CPU内部对指令及其逻辑进行判断的安全CPU设计方法和主要技术实现途径,使得CPU不仅具有执行指令的功能,而且具有防范恶意指令和恶意代码的功能。通过将信息安全技术下沉到CPU内部,不仅能防范恶意代码破坏信息防御技术,而且能最大程度地利用硬件的性能提升信息安全防御能力。

本文介绍的安全架构设计思路和方法已在龙芯3A4000CPU中得到应用和有效性验证。通过研究信息安全技术,并将其融入到CPU的设计和实现中,能大大提升我国CPU的自主控制能力和信息安全防范能力。