用于低成本光声成像的纳秒激光驱动器设计

高铁成,李新新,远桂民,王 昊,薛峰军

(1.天津工业大学 天津市光电检测与系统重点实验室,天津 300387;2.武汉奔跑吧教育研究院,武汉 430000)

光声成像是指脉冲激光照射到生物组织中,组织的光吸收域产生超声信号,这种由光激发产生的超声信号称为光声信号,光声信号携带了组织的光吸收特征信息,通过探测光声信号能重建出组织中的光吸收分布图像。光声成像结合了光学高对比度和声学高分辨率的优点[1-3],当组织的不同部分吸收系数和散射系数差别很大的时候,能够取得更加理想的效果。组织中的血红蛋白散射特性好,所以光声成像对血管的成像效果特别好,无论是对血管疾病的直接诊断,还是对血管周围的病变组织进行成像,都有很好的效果。

光声成像通常使用纳秒宽度的光脉冲[4-5],纳秒超短脉冲可以实现最大化信噪比(SNR)和成像分辨率;高的脉冲重复频率可以通过信号平均来提高信噪比(SNR),从而降低成像的扫描时间;特定的单脉冲能量可以满足不同应用对象的能量要求。在临床宏观成像中,成像深度在几毫米到几厘米之间时,需要的脉冲能量较高,约10~100 mJ/pulse,这种大能量脉冲由固体激光器提供,比如Nd:YAG 和染料激光器,脉冲重复率小于20 Hz,脉宽约为10 ns,这种激光器价格昂贵、操作复杂。光声显微成像的深度为微米到毫米时,目前使用脉冲光参量振荡器(OPO)或者染料激光器,相比宏观成像其脉冲能量要求较低,所以成本有所降低,但是脉冲OPO 和染料激光技术不适合小型化和大幅降低成本,而且由光学参量振荡器和染料决定输出的波长,增加了光源的成本和复杂性。

针对以上问题,本文采用高速大功率场效应管作为开关,以激光二极管代替上述大功率固体激光器,设计了一种纳秒级激光脉冲驱动器,以提高成像速度,降低激光器的使用复杂度,使得驱动器的整体结构更加紧凑,同时大幅降低光声显微成像成本。

1 纳秒激光驱动器的元器件选择

1.1 纳秒短脉冲的获取

利用现场可编程逻辑门阵列(FPGA)产生脉冲宽度调制(PWM)信号,采用Verilog 语言编写产生脉冲宽度可调节的信号。Altera 公司Cyclone IV 的PLL 具有时钟倍频和分频、相位偏移、可编程占空比和外部时钟输出等功能,本文采用该PLL 功能,进行系统级的时钟管理和偏移控制[6-7],对50 MHz 晶振进行分频,产生频率可控制、占空比可调节的PWM 信号。

图1 所示为利用FPGA、采用Altera 公司Cyclone IV 的PLL 功能产生的PWM 信号,此信号的重复频率为50 kHz,占空比为0.2%,脉宽为40 ns,上升、下降时间为5 ns,电压为3.3 V。在实际使用中可以根据需要,利用Verilog 产生满足要求的TTL 信号。

图1 可调节的PWM 信号图Fig.1 Adjustable PWM signal diagram

1.2 栅极驱动器的选择

利用FPGA 产生的PWM 信号通常为3.3 V 逻辑信号,不能有效打开功率MOSFET。将PWM 信号升至MOSFET 的栅极驱动电压过程中需要一个栅极驱动器,通过高瞬变电流对栅极电容进行快速充电和放电,减少导通损耗。栅极驱动器的主要特点如下:

(1)栅极驱动器执行电平转换任务,相比微控制器I/O 引脚,能提供更高的驱动电流;

(2)栅极驱动器有更高的驱动能力,支持快速切换,信号上升、下降时间只有几纳秒。

栅极驱动器的开关切换时间越短,提供给MOSFET 的有效电流时间越长,其驱动的晶体管的开关损耗也更低,系统效率更高。此外,驱动电流也是选择栅极驱动器的重要指标。基于此,本文选择了UCC27532栅极驱动器。

1.3 FET的选择

功率MOSFET 的性能对于整个驱动器是否能产生符合预期的脉冲非常重要。符合要求的功率MOSFET必须具备以下特点:

(1)为了确保纳秒延迟时间内达到高电流,FET必须快速完全导通,因此,FET 的高导电特性非常重要。

(2)FET 的峰值电流表示通道的饱和,并且Rds(on)快速增加超过额定电流,这意味着系统中可能的最高电流最终受到FET 峰值电流的限制。

(3)由于极高的di/dt,如果栅极电流回路的信号地和电源电流回路的电源地连接在一起,电源地上的大电流会在信号地上产生电压差,原因是导线存在阻抗,流过的大电流会在导线上产生电位差,称之为共阻抗干扰。信号地的真实电位高于0 V,栅极会检测到其Vgs相对电压的降低,可能会将原本是高电平的信号误判为低电平,从而将栅极截断,导致负反馈,进而减慢FET 的开启过程。因此,需要有两条单独的接地回路,通过提供单独的接地返回路径来完全去耦栅极信号,确保栅极电流回路没有电源电流;需要使用专用引脚作为信号地的连接点,专用开尔文接地引脚的FET 可以满足这个要求。本文选择专用开尔文连接FET,参数重点在于击穿电压和峰值额定电流是否满足要求[8-10]。FET 的等效图如图2 所示。

图2 FET 等效图Fig.2 FET equivalent diagram

图2 中,Cgs和Cgd这两个电容的大小由器件的实际几何结构决定,而Cds电容器即寄生双极晶体管的基极集电极二极管(体二极管)的电容。栅极存在漏源导通电阻和外接电阻,漏源之间存在电感。

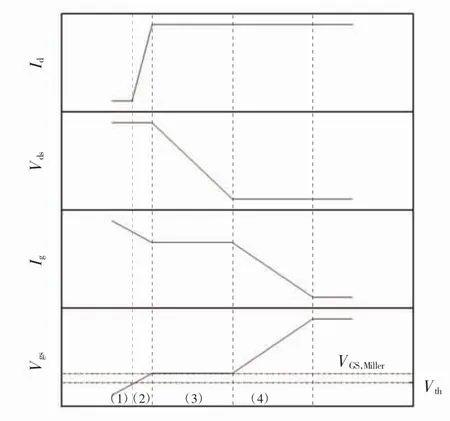

FET 的导通速度和导通损耗对于驱动器性能非常重要。图3 所示为FET 导通过程。

图3 FET 导通过程Fig.3 FET turn-on process

图3 中,FET 的导通分为以下几个过程:

(1)器件的输入电容从0 V 充电至Vth。在此期间,大部分栅极电流用于对Cgs电容器充电,少量电流也会流经Cgd电容器。随着栅极端子电压升高,Cgd电容器的电压将略有下降。这个过程称为开通延时,因为器件的漏极电流和漏极电压保持不变。栅极充电至阈值电平后,MOSFET 就能载流了。

(2)栅极电平从Vth升高到米勒平坦电平VGS,Miller。当电流与栅极电压成正比时,为器件的线性工作区。在栅极侧,与第1 阶段相同,电流流入Cgs和Cgd电容器中,Vgs电压升高;在器件的输出端,漏极电流升高,同时漏源电压保持之前的电平(VDS,off)。在所有电流传输到MOSFET 中,并且二极管完全关断能够阻止其PN 结上的反向电压之前,漏极电压必须保持输出电压电平。

(3)栅极已充电至足够电压(VGS,Miller),可以承载完整的负载电流且整流器二极管关断。此时,允许漏极电压下降。当器件上的漏极电压下降时,栅源极电压保持稳定。这就是栅极电压波形中的米勒平坦区域。驱动器提供的所有栅极电流都被转移,从而对Cgd电容器充电,以便在漏源极端子上实现快速的电压变化。此时,器件的漏极电流受到外部电路(直流电流源)的限制,保持恒定。

(4)通过施加更高的栅极驱动电压,充分增强MOSFET 的导通通道。Vgs的最终幅值决定了开通期间器件的最终导通电阻。所以,在第4 阶段中,Vgs从VGS,Miller上升至最终值VDRV。这一过程通过对Cgs和Cgd电容器充电来实现,此时栅极电流在两个组件之间分流。当这些电容器充电时,漏极电流仍然保持恒定,而由于器件的导通电阻下降,漏源电压略有下降。

以上为FET 的导通过程,FET 的关断过程与导通过程类似逆过程,不再赘述。

1.4 电容的选择

电容的封装、位置和电容值的大小是非常重要的,电源回路中电容必须允许最大总线电压通过,提供足够的电荷,以满足电流要求,最小化电感路径。电容器依靠施加电压使其带电,电极面积越大,相对电容率越高,电极间距离越短,则静电荷量越大[11-13]。

电容串联时,耐压值增大,电容量减小,公式为:

电容并联时,增大电容量,耐压值不变。电容器按照外观可分为带导线电容器和无导线的表面安装器件(SMD)型电容器。根据静电容量的范围、频率的高低,本设计选用SMD 器件。SMD 器件分为电解电容器和积层陶瓷贴片电容器,本文选择积层陶瓷贴片电容器,其静电容量计算公式为:

式中:C 为静电容量;ε0为真空电容率;εr为电介质的相对电容率;S 为电极面积;d 为电解质层之间的距离;N 为积层数。

时间常数τ = RC,则电容电量与充电时间的关系为:

式(3)中,当充电时间不同时,电量Q 的值存在差别。取时间 t 为 τ 的倍数,可得 e-1≈0.37,e-2≈0.14,e-3≈0.05,e-4≈0.018,e-5≈0.007。所以,充电时间要大于 3倍时间常数,有足够的时间充电,电容器才能达到充电电源电压。

2 纳秒激光驱动电路仿真

2.1 未考虑回路电感的电流分析

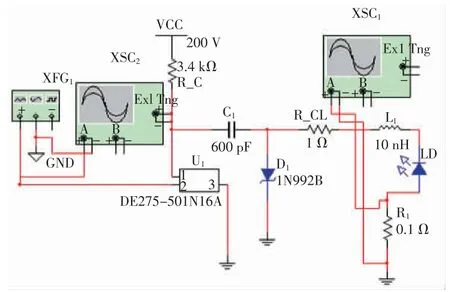

利用Multisim12.0 仿真工具对电路模型进行仿真,按照上述分析建立的电路基本模型如图4 所示,此时不考虑电感的影响。

图4 不考虑电感的驱动器电路仿真模型Fig.4 Drive circuit simulation model without considering inductance

图4 中驱动器工作原理为:电容器C1通过R_CC1-D1电路在高压VCC 下充电,R_C 是充电限流电阻,决定电容C1充电时间长短,直接决定LD 输出脉冲激光的重复频率,同时保证在晶体管导通时,不直接对电源短路。电容C1与电阻R_C 串联成为缓冲器,抑制产生的尖峰噪声,保护转换元件。功率MOSFET导通时,电容器C1通过激光二极管LD 放电。电容器C1和功率MOSFET 可在高电压下工作,电阻R_CL 将放电电流限制在所需的值。R1为放电时电流监测电阻,用来测量回路中脉冲电流的大小、宽度等,所以该电阻为高频、高精度、大功率电阻,通过改变高压VCC 幅度来控制电流强度。脉冲电流的上升时间由功率MOSFET的导通速度决定,下降时间由R_CL-C1-Q1-LD 电路的时间常数决定,通过改变电容值控制脉冲持续时间。按照图4 设置,所得R1两端电压如图5 所示。

图5 电阻R1 两端电压Fig.5 Voltage across resistor R1

图5 中,电阻R1两端电压与电阻的比值即为通过R1的电流。信号发生器提供PWM 信号,重复频率、占空比、电压幅值可调,直流电压为200 V,电容为600 pF、充电电阻为3.4 kΩ,放电限流电阻为1 Ω 时,所得电流脉冲宽度约为4 ns,电压约为3 V,即通过LD 的电流为30 A。通过调整电压VCC 幅值、PWM 信号的重复频率、占空比、电压幅值,均可以对通过R1的电流产生影响,得到大电流纳秒激光脉冲。

2.2 回路电感对电流的影响分析

在实际电路中不可避免地存在回路电感、激光二极管封装电感等,所以在仿真时应考虑电感对于所得电流的影响,将分布电感等效为电感L1,如图6 所示。

图6 考虑回路电感的电路模型Fig.6 Circuit model considering loop inductance

调整图6 中电感的大小,可观察回路中电感对于电路中电流的影响。信号发生器提供电压幅值为16 V、重复频率为50 kHz、占空比为1%、上升和下降时间为5 ns时,不同电感下通过R1的电压如图7 所示。

图7 不同电感对电路中电流的影响Fig.7 Effect of different inductances on current in circuit

由图7 可知,当电感为 2 nH(图7(a))时,电流脉宽约为8 ns,电流最大值约45 A;当电感为20 nH(图7(b))时,电流脉宽约为30 ns,电流最大值约为27 A。由图7(a)、图7(b)对比得出,回路中电感的大小对通过激光二极管的脉冲电流的幅值、脉冲宽度、上升时间、下降时间都有很大的影响。回路电感增加,脉冲上升时间变长,下降时间变长,电流峰值降低,即通过激光二极管的脉冲电流减小。因此,在实际电路中,应该尽量减少电路中存在的电感。

3 纳秒脉冲激光驱动电路的实现

利用Altium Designer 实现PCB 设计,检查无误后方可制作驱动器集成电路板。驱动电路原理图如8所示。

图8 中,为了减少由PWM 产生的脉冲信号在传输过程中产生的能量损耗及波形的失真,在PWM 信号输出端至栅极驱动器的输入端之间,添加了一个整形电路,该电路能减少信号的过冲,保持原有的波形,同时将电压提升至栅极驱动器的工作电压。

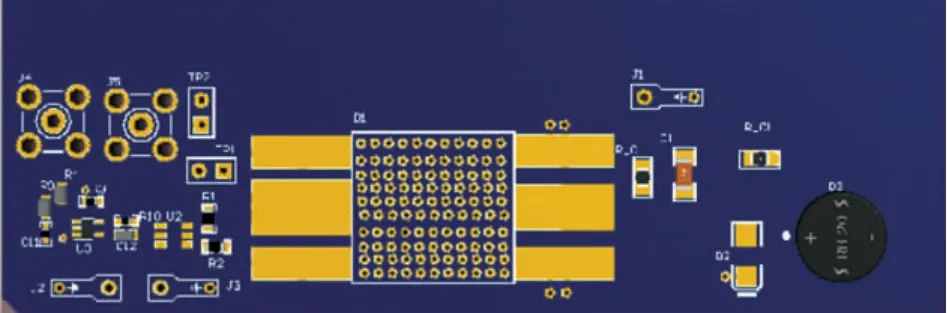

由于大电流和高速的要求,电路的布局尤为重要,将图8 转化为PCB,如图9 所示。

图9 纳秒脉冲激光驱动电路PCBFig.9 Nanosecond pulse laser driver circuit PCB

对图9 说明如下:

(1)所有接地回路都是在紧邻的层上完成的,最小间距为0.127 mm,通过为电流回路提供尽可能接近的耦合返回路径来最小化电感。

(2)信号地和电源地在内部连接到FET,在电路板上完全隔离,命名为2 个不同的网络。通过避免地面提升保持更快、更平滑的特性。

(3)并联多个不同的旁路电容器可以抑制不同频率的噪声,将噪声接地释放,同时满足向IC 瞬间供应电流,抑制电源电压变动,并且应尽可能靠近电源引脚。

由于本次设计为高速脉冲,需要考虑最小化寄生电感。所以,电路板采用分体式电源回路,旁路电容放在激光二极管的两侧。分体式回路的优势如下:

(1)由于回路是对称的,并有相同的电感,因此,分体相当于将两个电感并联,从而将有效电感减半,同时将电流分配到两个独立的分支中。如果仅有一个回路有电感L 和电流I,通过增加第2 个回路电感L,总体看来就像单电路电感减半[14-16]。

(2)由于两个回路中的电流以相反的方向流动,因此,磁通量有抵消的趋势,可以减少耦合损耗和电路板上的干扰,从而减少杂散阻抗,提高周围电路的抗干扰度。

焊盘中通过使用微通孔进一步降低寄生电感,提高组件的垂直提取电流,同时使电流回路尽可能短。

4 纳秒脉冲激光驱动电路的测试

激光管(LD)具有尺寸小、成本低、商业可用性高、重复率容限高、稳定性好、无需额外的外部冷却系统等优点,本文将其作为驱动电路的驱动对象[17-20]。

经测试,脉冲激光二极管(PLD)的发光区域约800 μm×400 μm,脉冲激光二极管工作时占空比低,平均功率较低,峰值功率较高,产生热量较低;缺点是重复频率只到几万赫兹,且发光波段仅在近红外波段,PLD单脉冲能量约为几微焦,由于生物组织血红蛋白的吸收系数在近红外区域,较可见光范围低2~3 个数量级,且在近红外650 ~1 200 nm 范围内产生的低对比度使得毛细血管成像困难。针对以上问题,可通过增加脉宽来提高脉冲能量,弊端是降低了空间分辨率。

连续波(CW)二极管可工作在近红外和可见光范围内,由于血红蛋白在可见光范围的高吸收率,使得较低的脉冲能量也能达到较好的SNR。CW 激光二极管可以更加紧密地聚焦且提供更短的脉宽,更加适合高分辨率成像。

本文使用OSRAM 的PL TB450B 激光二极管,其连续光输出功率为1.6 W(Tcase=25 ℃),典型发射波长为450 nm,持续工作电流为1.2 A,激光二极管的热量仅通过二极管的基板消散,必须保持二极管的基板与散热器相连。CW 激光二极管产生超短光脉冲,产生比额定值更强的光脉冲,不损坏器件,同时,可用波长范围更广且成本更低。通过匹配二极管发射波长与血红蛋白的吸收最大值,利用过驱动,改善成像的SNR 和分辨率。

根据 ANSI(American national standards institute)规定,在450 nm 处的单脉冲可具有20 mJ/cm2的最大能量密度和18 W/cm2的最大功率密度[21-22]。激光二极管的主要损伤机制为:

(1)光学灾变损伤COD(Catastrophic optical damage),激光二极管表面的光子密度过高会损坏二极管,即单个非常高能量的脉冲会降低甚至损坏激光二极管的性能。

(2)热容限,当耗散功率使二极管加热超过破坏阈值时,发生另一种损伤,即热损伤。

COD 限制了最大脉冲能量,热容限限制了最大重复频率。CW 激光二极管可在这两种损伤的极限附近工作,只要不超过任何一个极限值,激光二极管便可以稳定工作。保证CW 激光二极管的平均光输出功率低于额定损伤阈值,就可以进一步提高重复频率,以便在更短的时间内获得更多的平均值,缩短成像时间。

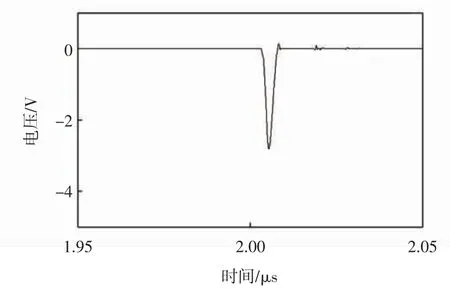

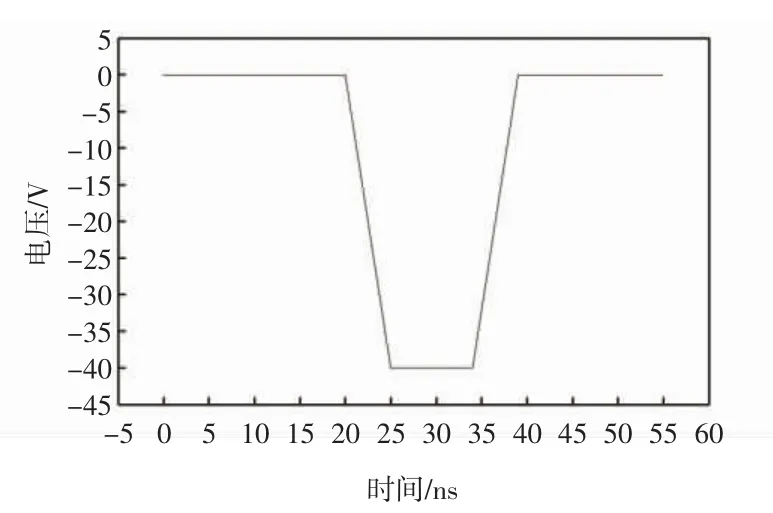

电路板中通过PL TB450B 激光二极管所得电流如图10 所示。

图10 调试电路通过电阻R1 的电流Fig.10 Current through resistor R1 in test circuit

由图10 可知,由于电流是通过地端流向LD,所以电流为负值。通过PL TB450B 激光器的最大电流约为40 A,脉冲宽度约为10 ns,重复频率50 kHz,能够充分触发激光二极管,且散热正常,没有多余的热量积累,电路实现正常工作。

5 结 论

本文介绍了纳秒激光驱动器的电路结构,并进行仿真和测试。测试中使用的过驱动激光二极管产生电流的重复频率为50 kHz,脉宽约10 ns,峰值电流约40 A。过驱动激光二极管可产生的电流最小脉宽约6 ns,峰值电流约50 A,单脉冲能量约200 nJ。通过本次电路设计,可以得出以下结论:

(1)MOSFET 的功率和开关速度对于驱动器电路中是否可以形成超短脉冲起到决定作用,形成超短脉冲时应使用开关速度更快的MOSFET。

(2)在满足耐压值的前提下,电容应该在满足容值时尽量提高重复频率。

(3)降低脉宽的主要限制因素是PCB 和激光二极管封装上的电感,电感阻碍电流的快速变化,环路寄生电感越小,放电电流的上升速度以及随时间的衰减越快,越容易形成窄脉冲。

(4)本次设计中的激光驱动器适用于驱动连续和脉冲激光二极管,过驱动CW 激光二极管可以扩大波长的使用范围,提高重复频率,从而提高成像速度,同时节约激光器成本。

综上所述,本次纳秒激光驱动器的设计满足了光声显微成像对于信噪比、分辨率、成像深度等指标的要求,与典型光声成像相比,降低了激光器的使用复杂度,提高了成像速度,大幅降低了光声显微成像的成本。