基于FPGA的UART控制VGA图像显示器设计

李 营,范静静,权循忠,吕兆承,陈 帅

通用异步串行收发器(UART)是一种实现设备之间低速数据通信的标准协议,该传输方式不需要时钟控制,只需通过两根信号线,分别进行数据的收发.所谓串行,是指将多位数据转为一位一位的串行数据进行传送,发送完后组合得到并行数据.该方式适合远距离传送[1-2].传统的串口控制往往通过单片机实现,他不便于扩展和模块化[3],而FPGA 作为高密度可编程处理器,具有IO 口多、并行运算速度快、模块化集成度高[4],对外围硬件进行扩展移植性高等特点.鉴于此本文根据UART 原理和VGA 时序显示原理,利用层次化建模思想将系统划分为PLL 分频器、波特率发生器、串口接收通信和VGA控制模块等模块,在Quartus 下利用硬件描述语言Verilog实现各功能模块,并进行配置,最终以FPGA芯片为核心控制器,将存储IP 核ROM 中的图像数据按照串口端的命令通过VGA在显示器端进行显示.

1 UART原理简介

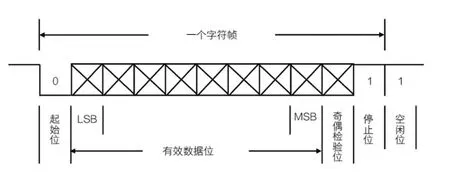

串行异步通信需要接收双方约定好数据传输速度和帧格式,即约定好一个数据位传输的时间和一个数据的长短.其中数据传输速度是用波特率描述,即每秒传输的数据位数,典型的数据帧格式如图1 所示,一个字符帧由起始位、数据位、校验位、停止位、空闲位构成[5].接收端一直处于监听状态,当监听到低电平的起始位后,就按照约定的波特率接收数据.即每当发送端发送数据时,先发送1 bit的起始位,以表示通信的开始,然后发送8 bit的有效数据位.有效数据的低位在前高位在后,之后再传送1 bit的奇偶校验位,最后发送停止位.

图1 串口帧格式

2 VGA接口原理

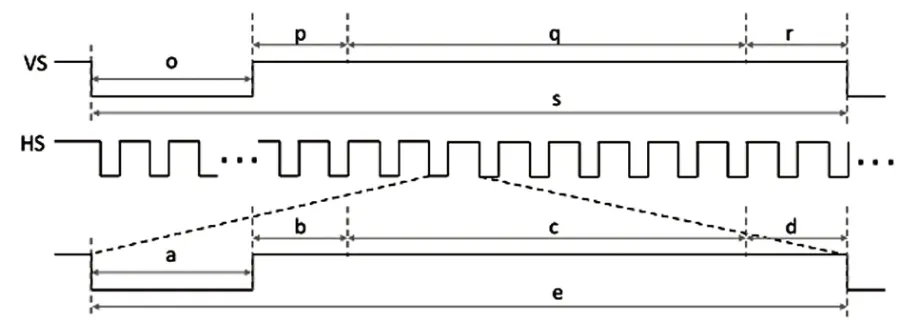

VGA 接口即视频图形阵列,采用非对称分布的15针连接方式,用户常用的有红绿蓝三色,行同步信号HS 以及场同步信号VS 等5 个信号.其中HS和VS的作用是处理输入模拟信号,并联合起来控制VGA的显示时序[6].文中VGA显示遵循640*480@60 工业标准,行扫描时序要求和场扫描要求分别见表1 和表2.通信时序如图2 所示.

表1 行扫描(HS)时序要求

表2 场扫描(VS)时序要求

图2 VGA的行扫描和场扫描时序图

3 系统总体实现方案

本系统由FPGA芯片、时钟电路、系统电源、VGA时序控制模块和串口通信模块等构成.依据层次化建模思想可将系统分为底层模块和顶层模块,功能框图如图3 所示.由图3 可知,该系统底层可划分为:波特率发生器模块(speed_setting)、PLL分频模块、串口接收处理模块(my_uart_rx)、VGA 时序控制模块(vga_controller).顶层模块(top.v)声明输入输出端口,并调用各底层模块构建串口通信控制VGA的图像显示功能.

图3 FPGA系统功能实现框图

3.1 VGA时序控制模块(vga_controller)

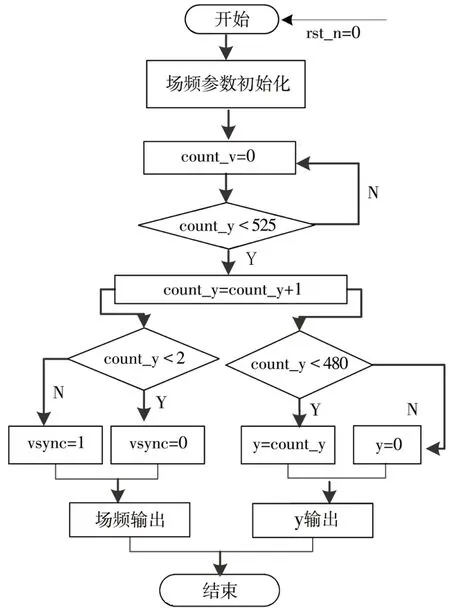

该模块连接串口接收处理模块和PLL 分频模块,最终实现针对不同串口指令,VGA显示不同的图像的功能,其中图像数据存储于IP 核ROM内以便本模块进行调用.工作原理是根据串口接收处理模块发送的不同串口指令数据rx_data,针对其不同数据进行模式切换,显示不同图像.设计采用640*480@60 工业标准.由文献[6]知此时场同步信号VS的周期为16.7 ms,行同步信号HS的周期为31.75 us,所需时钟频率25 MHz.设计中VS 扫描流图如图4 所示,HS 扫描算法与其类似,此处省略.

图4 场频率扫描算法流图

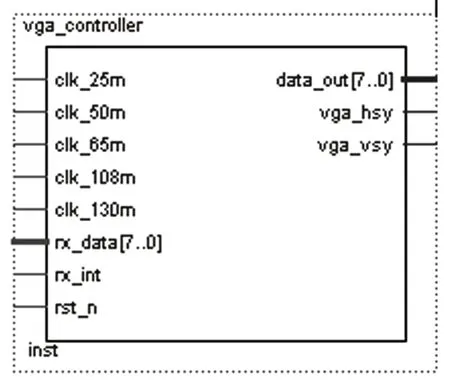

模块接口框图如图5 所示.以下为各端口的说明.

输入信号:rst_n 是复位信号,低电平有效;clk_25m 连接PLL 输出25 MHz 时钟,clk_50m 等其他信号类似;rx_data 信号接收数据寄存器,保存直至下一个数据来到;rx_int 信号接收数据中断信号,接收到数据期间始终为高电平.

输出信号:data_out是VGA显示色彩;vga_hsy是VGA显示行同步信号;vga_vsy是VGA显示场同步信号.

图5 VGA时序控制模块接口框图

3.2 分频模块(PLL_controller.v)

该模块的功能是对系统时钟进行分频,分别产生c0(25 MHz)、c1(50 MHz)、c2(65 MHz)、c3(100 MHz)、c4(130 MHz)时钟,以便其他功能模块调用.

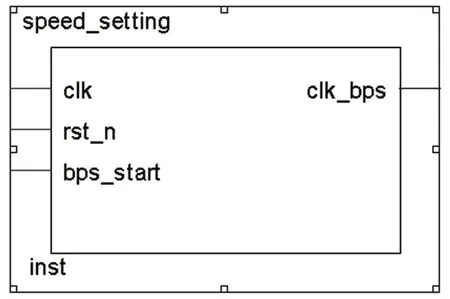

3.3 波特率发生器模块(speed_setting.v)

该模块的功能是根据给定的系统时钟频率和要求的波特率算出波特率发生器分频系数.波特率是指每秒钟传输的数据位[5].文中采用的波特率为9 600 bps,此时每位数据持续的时间是1 s/9 600=104.2 us,即每隔104.2 us 进行一次采样,若需要其他波特率也可在本模块选择,该模块的接口框图如图6 所示.其中输入信号clk 是25 MHz 主时钟,输入信号rst_n 是低电平复位信号,输出信号clk_bps 的高电平为接收或者发送数据位的中间采样点.

图6 波特率发生器模块接口框图

3.4 串口接收处理模块(my_uart_rx)

该模块连接波特率发生器模块和VGA时序控制模块,其功能是通过串口外设来接收计算机发送的数据,并送至VGA时序控制模块,模块示意图如图7所示.以下为各端口含义.

输入信号:clk 是25 MHz 主时钟;rst_n 是低电平复位信号;uart_rx 是RS232 接收数据信号,即用户键盘输入信号;clk_bps 连接波特率发生器模块,其高电平为接收或者发送数据位的中间采样点.

输出信号:bps_star接收到数据后,波特率时钟启动信号置位;rx_data 接收数据寄存器,保存直至下一个数据来到,rx_int接收数据中断信号,接收到数据期间始终为高电平.

3.5 顶层模块(top.v)

顶层模块连接各底层模块实现数据通信,满足实现系统功能要求,系统最终生成的RTL图如图8所示,从图8中可知,各底层模块间的连接关系与图3系统功能框图一致.

图8 系统RTL图

4 系统仿真实验

4.1 系统开发工具

系统开发采用的仿真软件是QuartusⅡ13.1,硬件描述语言是Verilog,硬件包含FPGA 核心板EP4CE6E22C8及UART控制器和VGA控制器等.

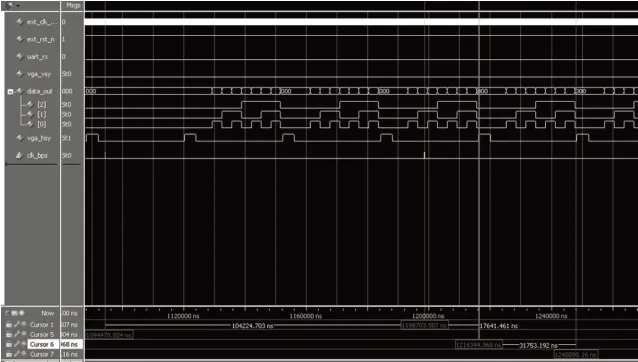

4.2 系统时序信号仿真

系统设计完成后编写测试文件进行时序仿真,结果如图9所示.图中ext_clk_50是50 MHz输入时钟信号,ext_rst_n 为输入复位信号,vga_vsy和vga_hs 分别为输出场同步和行同步信号,data_out为输出图像数据,clk_bps为串口波特率发生器的中间采样信号,由图9 中分析线可知:输出vga_hs的周期为31.75 us,与文中3.1小节所要求的VGA 接口时序一致,说明VGA 时序满足系统要求.clk_bps 的周期为104.2 us,与文中3.3 小节要求波特率为9 600 bps 时的信号采样间隔时间一致,说明串口通信满足系统设计要求.

图9 系统时序信号仿真结果图

4.3 硬件仿真

通过串口调试助手发送不同的16 进制数,存储于ROM内的不同图像将通过VGA在显示器端显示.如图10 所示,当通过串口调试助手发送16’h01时,在VGA显示器上显示了一幅男生图片.

图10 串口端发送16’h01时VGA显示的图像

4.4 系统仿真结论

通过4.2小节可知系统仿真时序与前述VGA显示和UART通信要求的时序一致,说明系统时序正确.通过4.3 小节硬件仿真验证了该系统可实现串口控制VGA图像显示功能.综上两方面说明利用层次化建模思想构建的UART 控制VGA图像显示器系统的设计方案是切实可行的.

5 结束语

文章利用自顶向下层次化建模思想,设计出基于FPGA的串口通信控制VGA图像显示系统,该系统能够利用UART控制VGA显示不同图像.与传统单片机设计相比,FPGA可方便地进行系统升级和移植,且本系统可实现异步通信及图像显示,在图像远程控制显示方面有一定的工业参考价值[7].