一种高速SpaceWire系统设计与验证*

姜 宏,刘淑芬,陈 龙

0 引 言

近年来,星载电子系统呈现出分布式和网络化的发展趋势,互联网络和总线作为数据交互的通道,其重要性日益显现.由于航天器任务复杂度的持续增加,控制计算机系统的计算量不断增大,从而导致系统中各个网络节点的数据量迅速增长.与此相对照,以1553B[1-2]为代表的传统总线技术,数据传输率低、支持的节点数量有限,成为制约系统性能和规模进一步提高的瓶颈.针对传统技术的不足,国内外学者提出了一些替代技术,例如:FC(Fiber Channel)[3]、TTE(Time-Triggered Ethernet)[4]和SpaceWire[5-6]等.

FC的协议标准最早制定于1988年,由ANSI X3T11标准委员会负责开发和协调.FC技术最初主要应用于商业数据中心的存储局域网(Storage Area Networks, SAN),随后被应用于航空领域,形成了FC-AE协议族.FC-AE协议主要包含FC-AE-1553、FC-AE-ASM、FC-AE-RDMA、FC-AE-FCLP及FC-AEVI协议,可用于航空电子环境下各设备之间的数据通信.在航天领域,美国NASA于2003年将FC技术运用到了其地面超级计算机Columbia,我国则在空间站型号上进行了FC-AE-1553产品的搭载试验.

TTE是由TTTech公司提出的,在IEEE802.3协议的基础上实现SAE AS6802的时间触发机制,能够兼容普通以太网和AFDX,支持以太网、AFDX(Avionics Full-Douplex Switched Ethernet)和TTE三种报文通信.TTE技术在工业控制领域已成功应用于汽车的车联网中;在航空领域,已在波音787和空客A380上得到应用;在航天领域,应用于NASA的猎户座载人探索飞行器(计划于2021年正式发射).

SpaceWire标准是由欧空局和英国的STAR-Dundee公司于2000年共同制定的.经过十几年的发展,SpaceWire标准不断丰富和完善,近年来衍生出了光纤版的SpaceFibre[7]协议.由于SpaceWire协议主要面向航天,因此自诞生不久的2003年起就开始应用于型号,目前已有几十个航天器使用了该技术.

在上述三种技术中,SpaceWire在航天器上的应用最为广泛,因此引起了众多国内外学者的关注.但是,在这些相关的研究工作中,标准SpaceWire传输速率一般只能达到200Mbps,很难满足星上新型传感器的实时图像传输需求;SpaceFibre协议的性能指标虽然很高,但是核心技术被国外机构所掌握,目前国内还未能实现自主化.因此,本文在前期工作[8-10]的基础上开展高速SpaceWire系统的设计和验证工作是非常必要的.

1 系统介绍

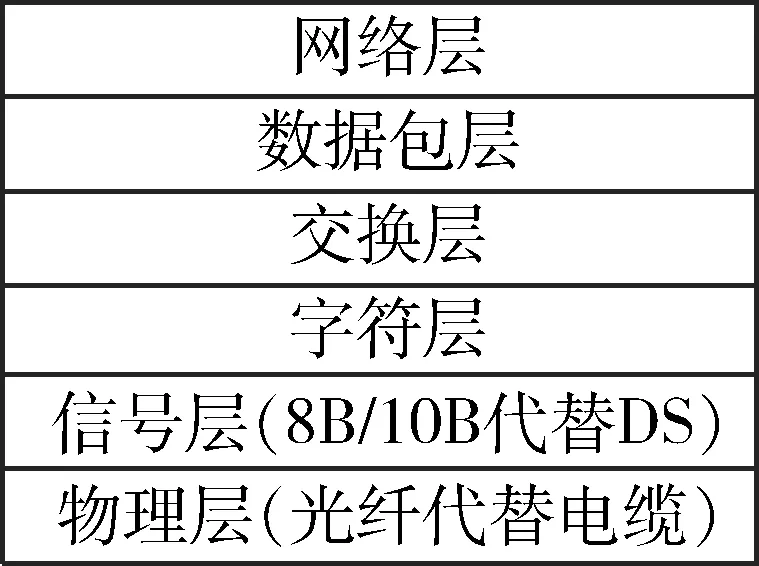

本文提出的高速SpaceWire系统对标准SpaceWire的物理层和信号层进行了改进(如图1所示),以提高总线系统性能.在改进中的主要设计思路是:保持信号层以上的协议与标准协议的一致性.

图1 高速SpaceWire的协议层Fig.1 Protocol levels of high-speed SpaceWire

2 系统架构

本文高速SpaceWire系统的设计目标是构造一个由1个路由节点、4个终端节点和两台监视主机(如图2所示)组成的简单而完整的总线系统.其中,终端节点1和2位于终端板卡1上,终端节点3和4位于终端板卡2上.终端板卡1通过光模块1和2接路由端口1和2,终端板卡2通过光模块3和4接路由端口3和4.终端节点和路由节点之间通过1米长光纤链路进行互联,最大物理带宽超过10 Gbps.

不论是路由节点还是终端节点,核心功能都通过FPGA(Field Programmable Gated Array)实现.其中,终端节点的FPGA实现了高速SpaceWire的Codec(Coding and Decoding) IP(Intellectual Property),路由节点FPGA实现了高速SpaceWire的Router IP.

3 节点设计

图2中的终端节点除了要执行高速SpaceWire协议处理外,还要频繁与后端系统进行交互,而路由节点主要进行不同端口间的数据转发.本文根据这两种节点的工作特点,开展设计工作.

3.1 终端节点

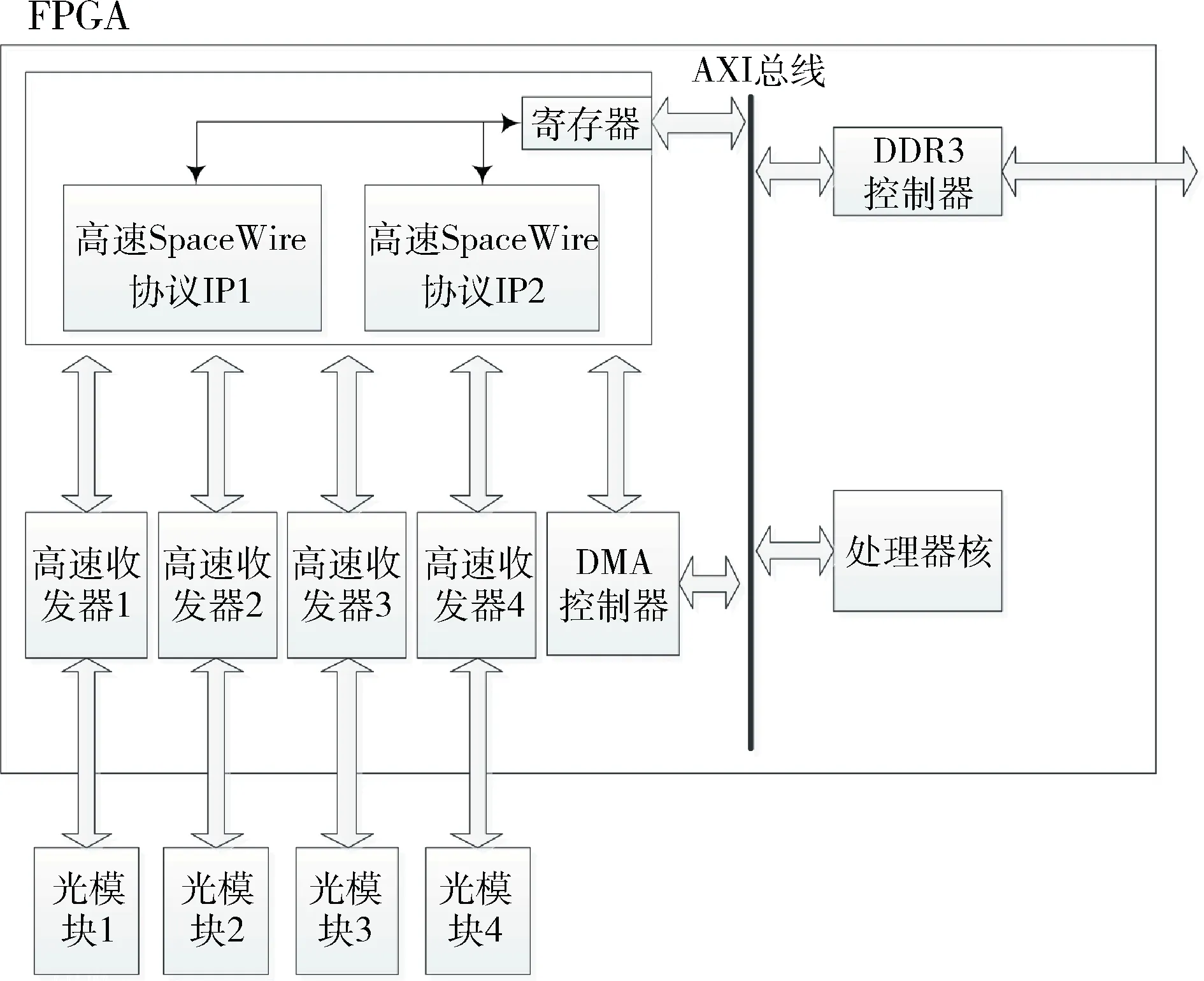

本文在传统SpaceWire协议IP的基础上,对终端节点的物理接口、片上总线技术进行了改进,并设计了DMA(direct memory access)模块以进一步提高系统性能(如图3所示).

(1) 物理接口

传统SpaceWire是一种全双工、双向、串行、点到点的数据总线.在每个方向上,它使用一对差分信号线传输编码后的数据.从而在每个方向上都会有四根信号线(D+、D-、S+、S-).SpaceWire物理层传输介质是电缆,其内部包含4组独立的屏蔽双绞线,物理带宽一般只有几百兆,很难达到吉比特级.为了提高网络带宽,在物理接口设计中采用高速光模块,并用光纤链路取代电缆.

由于光模块的传输速率通常可超过10 Gbps,因此需要在其后端配备高速收发器.本文的收发器采用Xilinx Virtex-7 FPGA内部的GTx(Gigabit Transceiver,包括:GTP、GTX、GTH等),具体类型为GTH,最大传输速率可达到13.1 Gbps.通过GTH实现串行信号与并行信号的相互转换:在接收方向,将高速的8B/10B串行信号转换为低速并行信号,便于FPGA内部逻辑执行复杂的协议处理;在发送方向,将低速的并行信号转换为高速的8B/10B串行信号,便于数据的高速传输.

(2) 片上总线

传统SpaceWire终端节点在协议IP与CPU间通过AMBA2.0标准下的AHB(Advanced High-performance Bus)总线进行互联,单位时间的数据吞吐量较低.

本文采用服从AMBA4.0标准的AXI4片上总线,最长可支持512位宽度的数据访问,而且利用AXI4 burst transfer(突发传输)中一个地址对应多个数据的特点,明显提高了片上总线利用率.

图2 高速SpaceWire系统架构Fig.2 Components of high-speed SpaceWire

图3 终端节点的功能结构Fig.3 Function structure of terminal node

图4和图5(阴影部分为无效信号)绘制了AXI4和AHB这两种片上总线在进行突发写操作时的时序.AXI4信号包括:

ACLK为AXI的时钟,AWADDR是写地址,AWVALID是地址有效信号、WDATA是写数据、WVALID是写地址有效信号、WLAST是写数据结束标志.当AHB对连续递增的地址进行写数据操作时(如图5),它和AXI4的执行效果类似,但是由于AHB每个时钟周期都要发布递增的地址到HADDR上,因此要执行写数据必须先等待HREADY信号有效且地址更新完成,两次数据之间的间隔时间明显变长,从而AHB总线的时钟周期相应延长,最终导致总线带宽的无效浪费.在极端情况下,当对相同的地址进行写操作时,AXI4允许数据连续不断地执行写数据,而AHB必须在每次写数据操作前插入类型为NONSEQ的HTRANS,以及对应的HADDR,在这种情况下AHB的总线利用率大约相当于AXI4的一半.

(3) DMA模块

DMA控制模块分为DMA发送和DMA接收两个子模块.

1) DMA发送

DMA发送子模块的核心是DMA发送状态机,包含7个状态:空闲、读描述符、检查描述符、读内存、写FIFO(First Input First Output)、写标志、写描述符(如图6所示).

图4 AXI4突发写操作时序Fig.4 Time sequence of AXI4 Burst writing

图5 AHB不定长突发写操作时序Fig.5 Time sequence of AHB Burst writing in random length

图6 DMA发送状态机Fig.6 The State Machine of DMA Transmission

系统复位时,状态机处于空闲状态,当链路建立连接且DMA_TxStart为1时状态机进入读描述符状态;读描述符状态主要执行读发送描述符的动作,然后进入检查描述符状态;在检查描述符状态,控制器会检查DMA发送使能位DescEn是否有效,如果有效则当等待发送的数据长度TxLen大于0时进入读内存状态,否则进入写标志状态,如果DescEn无效则返回空闲状态;在读内存状态,控制器通过AXI(Advanced eXtensible Interface)总线接口读取存储器中(地址由发送描述符指定)的128位数据,然后进入写FIFO状态;写FIFO状态的主要操作是检查发送FIFO是否已满以及发送是否完成,如果发送FIFO已满则停留在当前状态,如果发送已完成则进入写标志状态,否则将数据写入发送FIFO后继续进入读数据状态;在写标志状态,控制器会判断发送FIFO是否已满,如果未满则将数据包结束标志写入发送FIFO,然后进入写描述符状态;写描述符状态的主要操作是将发送状态写入描述符表,接着将当前描述符的DMA发送使能位改写为无效,然后重新回到读描述符状态,开始下一轮发送.

2) DMA接收

DMA接收子模块的核心是DMA接收状态机,包含6个状态:空闲、读描述符、检查描述符、读FIFO、写内存和写描述符(如图7所示).

图7 DMA接收状态机Fig.7 The State Machine of DMA Reception

当系统处于复位状态时DMA控制器处于空闲状态,当链路建立连接且DMA_RxStart为1时进入读描述符状态;在读描述符状态,控制器读取描述符信息,然后进入检查描述符状态;检查描述符状态的主要操作是检查DMA接收使能位DescEn是否有效,若无效则返回空闲状态,否则进入读FIFO状态;在读FIFO状态,控制器首先判断已接收的数据长度RxLen是否大于等于描述符中规定的最大长度或者已经接收到了数据包结束标志EOP(End of Packet)或EEP(End of Error Packet),若是则跳转到写描述符状态,否则检查接收FIFO是否为空,当不为空时从接收FIFO中读取数据,然后进入写内存状态,否则停留在当前状态;在写内存状态,控制器通过AXI总线接口将数据写入存储器中的规定地址(由接收描述符指定),然后回到读FIFO状态;在写描述符状态,控制器会将接收状态写入当前描述符,接着将当前描述符的接收使能位改写为无效并写入内存,最后回到读描述符状态,开始下一轮的接收.

3.2 路由节点

3.2.1 工作原理

本文路由节点的FPGA设计原理是:当接收到数据包的包头时将会检测输出端口.若输出端口空闲,则会打开输入端口和输出端口之间的交换阵列开关,建立连接通道,数据通过该连接通道源源不断地进行传输.当接收到结束字符时,表明一个完整的数据包传输完成,此时将会断开交换阵列开关,关闭连接通道,释放目的端口给下一个从其它输入端口进入的数据.FPGA逻辑在对数据包的包头完成识别后包头已经没有任何作用和意义,因此会采用包头删除技术将其丢弃.图8是在FPGA中实现的一个四端口路由节点的功能结构.

图8一共包含4个Codec模块,1个交换阵列模块及1个路由控制模块.Codec模块是高速SpaceWire协议的处理单元,用于建立和维护SpaceWire链路连接并负责数据包的接收和发送;交换阵列是路由器转发的物理路径,通常采用mesh结构;路由控制模块是路由器的核心单元,包含目的端口仲裁模块和组寻址路由转发模块两个最主要的子模块.

3.2.2 子模块设计

(1) 目的端口仲裁模块

目的端口仲裁子模块的核心部分是转发仲裁状态机.该状态机在初始时处于空闲等待状态,当进入工作状态后首先判断数据包转发端口的状态,如果目的端口断开或未运行,则数据包被丢弃;然后判断目的端口的发送缓冲队列是否已满,如果是则将数据包丢弃,否则判断是否具有相同目的端口的其他数据包;如果多个数据包的目的端口相同,则按照优先级进行排队,如果优先级也相同,则按照先后顺序进行排队.

图8 路由节点的功能结构Fig.8 Function structure of Router

(2) 组寻址路由转发模块

组寻址路由转发子模块支持单播和组播,主要功能是通过路由信息查找数据包的目的端口,并在适当时机转发数据包.在设计过程中,本文实现了路由转发状态机.该状态机包含的6个状态,分别为:等待地址、生成请求、请求被应答、删除头部、等待结束、数据包丢弃.

在等待地址状态,转发模块判断源端口缓冲区是否非空,若满足条件则对地址进行解析后进入生成请求状态,否则停留在当前状态;在生成请求状态,等待目的端口的应答,若收到应答则进入请求被应答状态,若超时无应答则进入数据包丢弃状态,否则停留在当前状态;在请求被应答状态,若删除使能信号为1,则进入删除头部状态,否则进入等待结束状态;在删除头部状态,执行删除头部操作,然后进入等待结束状态;在等待结束状态,若源端口缓冲区和目的端口缓冲区状态正常且未收到数据包结束标志,则停留在当前状态并执行数据传输,若收到了数据包结束标志则回到等待地址状态,否则禁止数据传输,并在等待了一段时间后进入数据包丢弃状态;在数据包丢弃状态,转发模块会清空源端口缓冲区然后返回等待地址状态,开始新一轮的路由转发.

4 测试验证

4.1 测试条件

(1) 硬件平台

图2中的终端板卡和路由器的硬件都采用Xilinx公司的VC709评估板,对评估板FPGA加载不同的配置使之实现不同的功能,监视主机则采用HP Z800工作站.

(2) 软件平台

嵌入式处理器采用Xilinx公司的Microblaze软核.嵌入式软件开发和调试工具采用Xilinx SDK.

监视主机的操作系统是Windows7.在Windows7下,利用VisualStudio2010开发了测试软件.该软件可通过PCI-E接口与VC709评估板上的嵌入式处理器软件进行通信,发起功能测试和性能测试.

(3) 测试环境

测试在实验室条件下开展,温度约为25°.

4.2 测试过程

为了对高速SpaceWire系统的设计进行验证,本文开展了功能和性能测试,具体包括:

(1) 数据传输功能测试;

(2) 性能测试

1)误码率测试;

2)数据传输速率测试.

4.2.1 数据传输功能测试

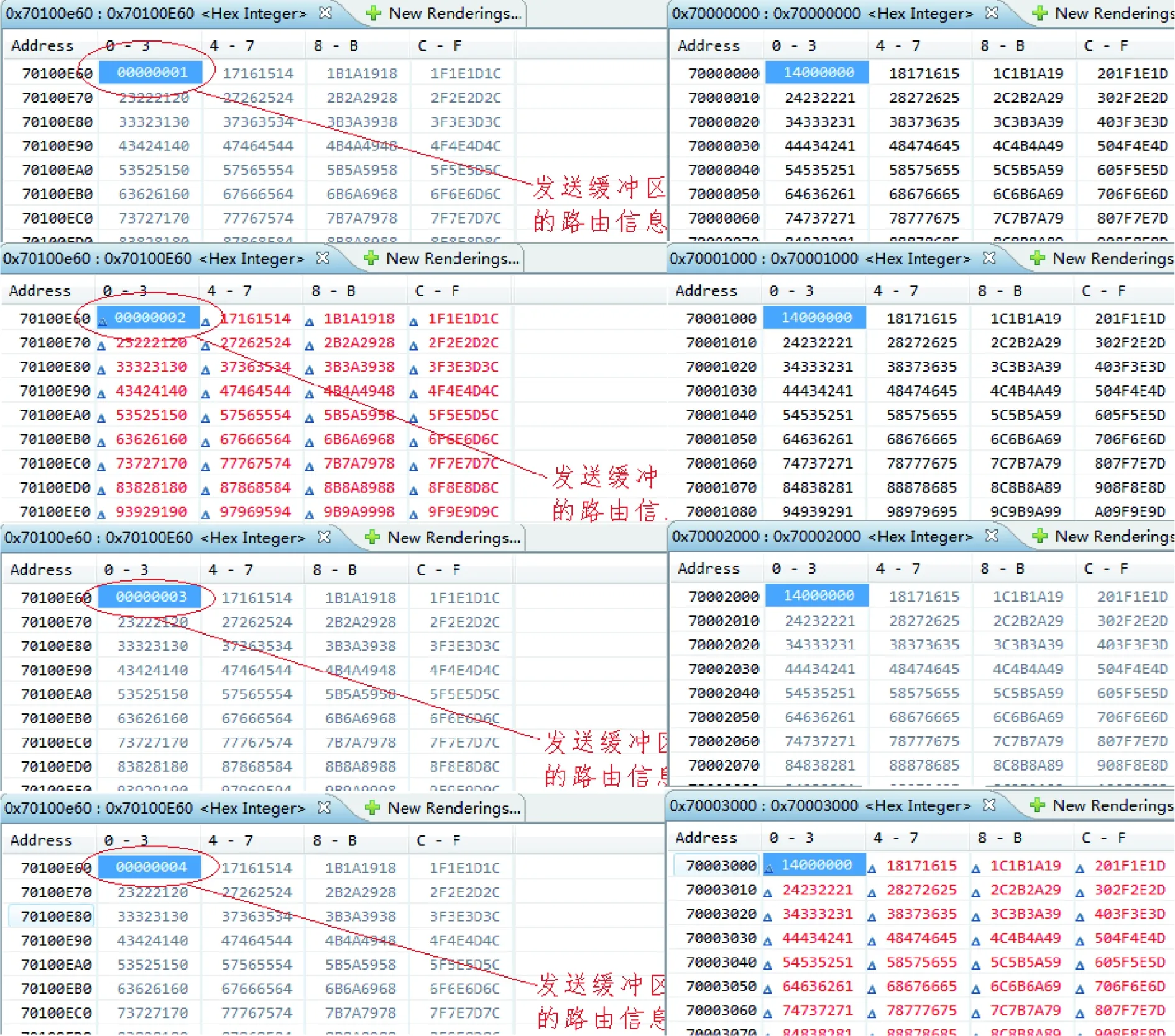

测试方法是:以图2中的终端节点1为源节点,再分别以终端节点1,2,3,4为目的节点,开展数据包大小为1000个字节的数据传输测试,若目的节点正确接收到数据则测试通过.

图9中,左侧显示的是源节点1的发送缓冲区内容,右侧显示的是目的节点分别为1、2、3、4时的接收缓冲区内容.为了便于区分,终端节点1和2使用了不同的光模块,由于每个光模块对应不同的接收缓冲区,从而图9右侧显示的四个起始地址也不同,分别为:0x70000000、0x70001000、0x70002000和0x70003000.通过比较发送缓冲区和接收缓冲区的内容可以发现数据是完全一致的,因此测试通过.

4.2.2 性能测试

(1) 误码率测试

误码率测试的方法是:首先将终端板卡1上的光模块1与光模块2进行连接,然后设计FPGA内部的处理器软件,生成伪随机测试序列[11],接着由终端节点2将数据发送出去,再经过光纤链路回到终端节点1,最后由处理器软件对发送和接收的数据进行比对,检查是否存在误码.

在实际测试过程中,基于上述方法连续测试了58个小时,共发送和接收了3476823008000 bit数据,对发送和接收数据进行比对后未发现1位误码,因此由文献[12]可估计得到误码率以大于95%的置信度等于1×10-12(图10和图11是发送数据存储区和接收数据存储区的比对情况).

图9 数据传输测试结果Fig.9 Results of data transmission testing

图10 发送存储区数据Fig.10 Transmitting data in memory

图11 接收存储区数据Fig.11 Received data in memory

比较图10和图11可发现,发送和接收存储区中的数据是完全相同的,并且都是没有规律的随机数.

(2) 数据传输速率测试

数据传输速率测试细分为两部分,第一部分是协议链路层传输速率测试,第二部分是应用层传输速率测试.

第一部分的测试方法是:在协议IP与GTH收发器之间设计一个64位的计数器,每次传输后计数器加1,计数器的数值被写入寄存器供处理器访问.处理器上运行的测试软件由主程序持续进行数据传输,然后启动一个定时器,在每次定时器中断处理函数中读取传输计数器的数值Ci,接着取相邻两次数值的差值ΔC=(Ci+Δt-Ci),最后由ΔC/Δt计算出的结果即为协议链路层传输速率.在测试软件运行过程中,实际测得的结果约为2 Gb/s.

第二部分的测试方法是:由测试软件的主程序发起连续的数据传输并启动1个定时器(每10 ms触发1次中断),每次传输的数据包大小为1 000个字节,并在每次传输后将传输计数器值TxCnt加1,每执行一次定时器中断处理函数对时间值TmCnt加1,当传输达到规定的时间后,按照公式8×105×TxCnt/TmCnt进行计算即可求得应用层传输速率.在测试软件运行过程中,实际测得的结果约为413.4 Mb/s.

4.3 测试结果汇总

综合以上实验情况,可得到如表1所示的测试结果.

表1 测试结果Tab.1 Testing results

在表1中,数据传输测试由于是功能性,因此当通过路由转发进行数据传输都满足测试要求后可得出测试正确通过的结论,误码率和数据传输率都是性能测试,利用测试软件开展测试验证后分别得到表中的数值.需要说明的是,应用层最大数据传输率是加上软件运行开销后测得的结果,因此在数值上明显小于链路层最大数据传输率.

5 结 论

本文在对国内外研究现状进行归纳总结的基础上,指出了传统SpaceWire总线技术虽然在航天器上应用广泛,但是存在传输速率低的弱点.针对这一不足,本文首先提出了高速SpaceWire系统架构.在此基础上开展了高速SpaceWire终端节点和路由节点的FPGA设计.其中,关于终端节点部分对物理接口、片上总线和DMA设计进行了着重论述;路由节点部分重点解决了目的端口仲裁模块和组寻址路由模块的设计问题.在测试验证部分,开展了数据传输测试、误码率测试和数据传输率测试,测试结果表明高速光纤SpaceWire系统不仅数据传输功能正确,而且误码率以大于95%的置信度等于1×10-12,在链路层最大数据传输率2 Gbps的前提下应用层软件的传输速率最大可达到413.4 Mb/s.本文的研究工作已经设计实现了可成功组网的吉比特级终端节点和路由节点,具备主要功能且技术指标较先进,从而为高速SpaceWire技术在航天器上的工程应用创造了良好的条件.