CAN总线控制器CRC校验码的设计原理及实现

王 爽

(中国电子科技集团公司第四十七研究所,沈阳110032)

1 引 言

在对以CAN 总线作为现场总线进行设备互联的电路系统的设计中,为保证设备间数据传输的正确性,需要对CAN 网络设备间通信过程传输的报文数据进行差错控制。为此,要在CAN 总线控制器的设计中加入了CRC(循环冗余)校验逻辑设计。对于报文传输出现错误的情况,CAN 总线控制器采用的处理措施是反馈错误信息给发送端进行报文重发,即一旦收到接收端发出的出错信息,发送端便自动重发。循环冗余校验码的工作原理简单,误判率较低,在CAN 总线通信系统中获得了广泛的应用。故此对CAN 总线控制器中循环冗余校验码的设计原理和实现过程展开介绍。

2 CRC码检错工作原理

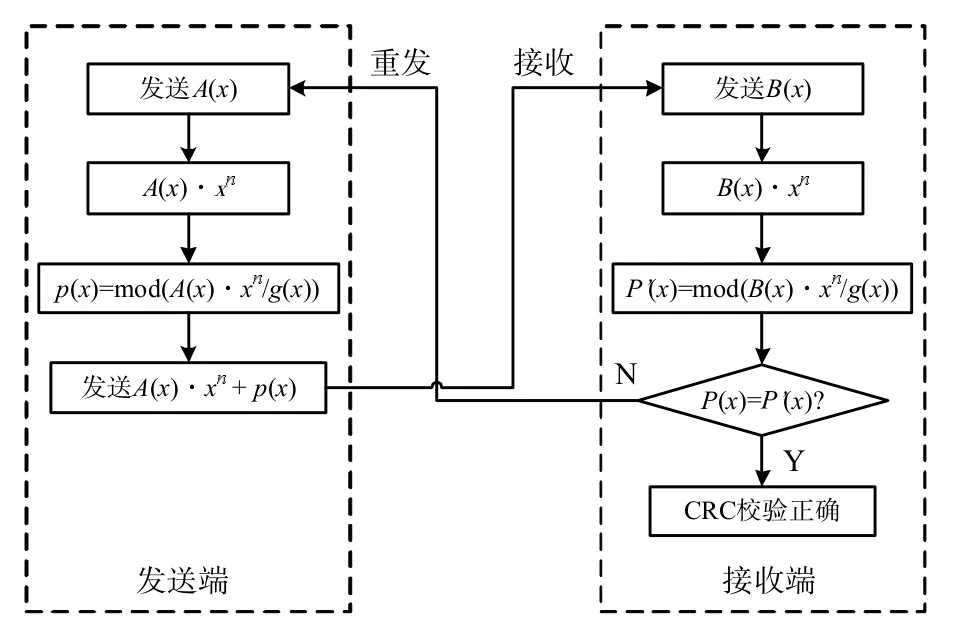

在对CAN 总线控制器的设计中,CRC 校验码所起的作用是将发送端检测到的报文二进制序列作为一个二进制多项式A(x)的系数,将接收端检测到的报文二进制序列作为另一个二进制多项式B(x)的系数,若能够正确接收,A(x)与B(x)应完全相同。用该系数除以发送端和接收端共同使用的生成多项式g(x)后,将得到的余数p(x)作为CRC 校验码。随后CAN 总线控制器的发送端将得到的CRC 校验码附加到报文中,一并发送给接收方。接收方再用同样的g(x)去除收到的报文B(x),如果余数等于p(x),则传输正确(即A(x)和B(x)相同),否则判定传输过程中出错,接收端发送出错信息通知发送端重发报文,并重新开始CRC 校验,直到传输报文正确为止。

在对CAN 总线控制器CRC 校验逻辑的设计过程中,需要注意以下三个方面:

① CRC 校验的计算采用的是模2(mod 2)运算法,不进位亦不借位,实际上是被除的二进制多项式与生成多项式两个操作数的逻辑异或运算;

②将待处理报文组成的被除多项式A(x)左移n 位,即乘以 xn,n 为生成多项式 g(x)的最高幂值,空出的n 位用来存放CRC 计算的余数p(x),因此CAN总线控制器实际计算出的带有CRC 校验码的报文序列为 A(x)·xn+p(x);

③生成多项式g(x)的首位和末位的系数必须为1。

CRC 校验的工作原理如图1所示。

图1 CRC 码检错工作原理图

3 循环冗余校验码的工作原则

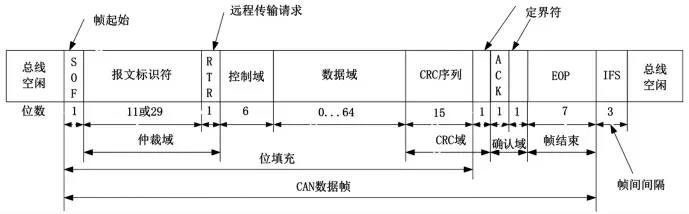

CAN 总线协议中规定了数据帧和远程帧两种帧格式,其传输报文都会携带CRC 校验数据随同发送和校验。数据帧由7 个不同的位域组成:帧起始、仲裁域、控制域、数据域、CRC 域、应答确认域、帧结尾[1]。远程帧比数据帧减少了数据域,相当于数据长度为0。图2 为CAN 总线数据帧/远程帧格式。

图2 数据帧/远程帧格式

在数据收发的过程中,对由帧起始、仲裁场、控制场、数据场(远程帧无数据场)组成的位流进行CRC 循环冗余校验。CAN 协议规定,当CAN 总线上连续出现5 个以上相同极性的数据时,在第5 位数据发送后,CAN 总线控制器自动填充一位相反极性的数据发送出去。该位即为填充位,用以避免CAN总线上长时间保持同一数据极性,确保区分错误帧和过载帧。在CAN 总线控制器的检错逻辑设计中,为进行 CRC 计算,被除的多项式(A(x)、B(x))系数由帧起始、仲裁场、控制场、数据场(远程帧无数据场)部分的无填充位流给定。

CAN 总线协议中规定,CAN 总线控制器检错设计所采用的CRC 算法生成多项式[2]为g(x)=x15+x14+x10+x8+x7+x4+x3+1。CAN 总线控制器中采用的CRC 校验多项式能够校验七级,它的检错能力很强,误判率极低,成为提高CAN 总线设备间数据传输正确性的有效保证手段。

被除的多项式(A(x)、B(x))被 g(x)多项式除(其系数以2 为模),得到此多项式除法的余数即为发送到CAN 总线上的CRC 序列。

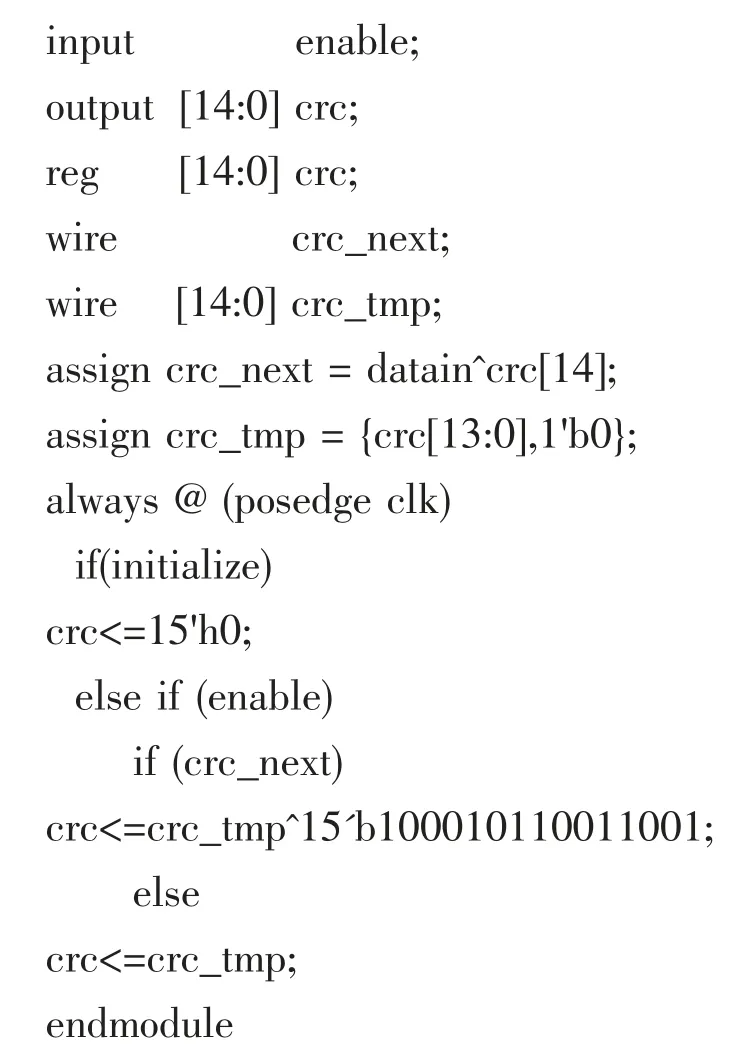

4 CRC校验代码的设计实现

CRC 校验码的RTL 代码设计便于实现,此处给出 CAN 总线控制器 CRC 码的 verilogHDL 的 RTL级实现[3]。CAN 总线控制器的CRC 逻辑设计采用被除多项式由帧起始、仲裁场、控制场、数据场(假如有)部分的无填充位流构成,生成多项式由第三节的g(x)给出,除法得到的余数就是发送到CAN 总线上的CRC 序列。这个多项式除法遵循模2 运算法则,不考虑进位、借位,实际上是按位异或运算。为实现此功能,在CAN 总线控制器的CRC 逻辑设计中使用了15 位的移寄存器crc[14:0][4-6]。如果用datain 存放指示位流的下一位数据,它从帧的起始到数据场末尾皆由无填充的位序列给定[7]。CAN 总线控制器CRC 检错逻辑的RTL 设计实现代码如下:

5 功能仿真

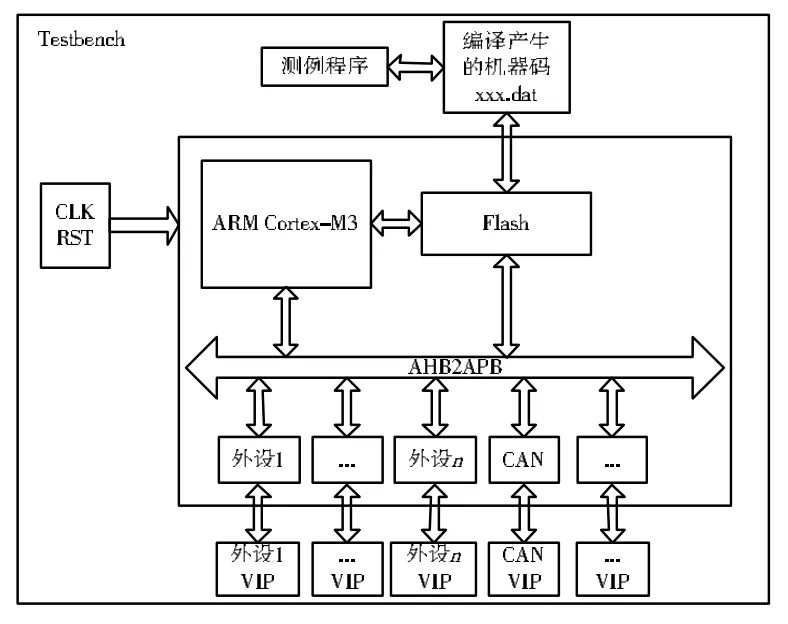

CAN 总线控制器的CRC 检错逻辑设计完成后,将其与CAN 总线控制器的其他模块设计进行系统整合,并将其挂接到以Cortex-M3 为核心处理器的一款MCU 设计中,搭建仿真验证平台进行功能仿真验证[8-9]。图3 为所设计的仿真验证平台,其中包括处理器内核ARM Cortex-M3、flash 存储器(用于存放测例程序)、CAN 总线控制器设计(其中包括被测单元CRC 检错设计)以及平台激励信号。

图3 CRC 仿真验证平台

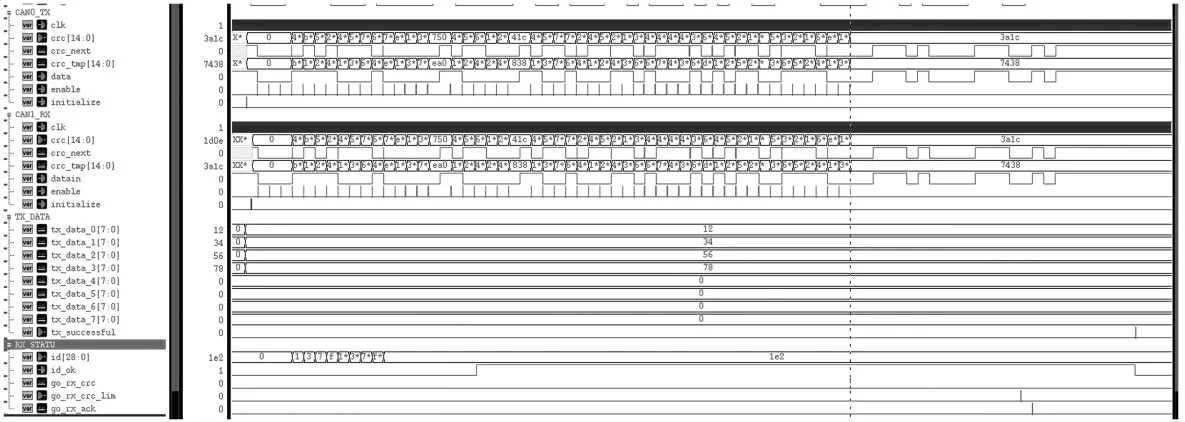

图4 为CAN 总线控制器CRC 检错设计仿真波形图。该例程发送的是一个标准格式的数据帧,标识符id 序列为00111100010,发送数据字节长度为0100,发送数据为 0x12、0x34、0x56、0x78,通过 CRC检错单元计算得出的CRC 校验码为0x3a1c。通过仿真可以看出,发送方与接收方的CRC 计算结果相同,最后接收方成功接收到了正确的数据并通过校验。图中光标所示的右侧为开始发送CRC 序列,到go_rx_crc_lim 标志结束。

图4 CRC 仿真波形图

6 结束语

通过对设计的研究与分析,完成CAN 总线控制器的CRC 检错逻辑设计,并将其集成在CAN 总线控制器中,验证功能正确。由于CRC 校验码的检错能力强,设计实现简单,可广泛应用于各类电路的数据校验设计中,用于提高数据传输可靠性。所提出的设计方法可直接应用于其他串行数据的CRC检错逻辑设计中,具有一定的通用性。