基于晶振偏移补偿的机械振动WSN同步累积误差抑制方法

鲜鸿宇, 邓 蕾, 汤宝平, 肖 鑫

(重庆大学 机械传动国家重点实验室,重庆 400030)

无线传感器网络(Wireless Sensor Networks, WSNs)应用于机械振动监测往往需要多测点同步采集[1-4],同步采集精度的高低直接影响信号采集的有效性和状态分析结果的好坏[5-8]。晶振偏移是影响同步采集精度的一个重要因素[9-10],为节点提供时钟的晶振频率会随外部环境变化发生偏移,使各节点采样间隔存在差异,造成同步误差累积,因此需要对晶振偏移进行补偿。采用不同采样模式模数转换器(Analog-to-Digital Converter, ADC)的WSN节点需要不同的晶振偏移补偿方法,ADC的采样模式有以下两种:①到达采样点时,为ADC输入相应数量(由控制域位数和ADC位数确定)的时钟脉冲,时钟脉冲的微小抖动对其采集精度影响可以忽略,只需保证采样频率准确即可;②ADC需要连续精准的采样时钟,常结合过采样技术(采样时钟大于采样频率)来提高模数转换精度。针对采用第①种采样模式ADC的无线传感器网络节点,黄庆卿等[11-12]分析晶振的非理想特性造成采样间隔抖动,并提出补偿算法抑制同步累积误差,Xiao等[13]校准信标在网关节点到采集节点间的传输时延,补偿路由节点与采集节点的晶振偏移,实现多跳无线传感器网络同步采集;针对采用第②种采样模式ADC的无线传感器网络节点,曾贵伟等[14]设计了一种采用24bits∑-Δ型ADC ADS1271的机械振动无线传感器网络节点,该ADC在低功耗模式下完成一次数据转换需要512个时钟脉冲,微控制器无法进行晶振偏移补偿。因此,针对采用第②种采样模式ADC的无线传感器网络节点,考虑到节点功耗和晶振偏移补偿对微控制器的处理性能要求,本文采用24 bits SAR ADC AD7766-1,完成一次数据转换只需16个时钟脉冲,在50 kHz采样频率下,需要800 kHz连续采样时钟,微控制器可以有效对其进行晶振偏移补偿。

针对采用连续高频采样时钟ADC的WSN节点存在同步累积误差的问题,提出了一种基于晶振偏移补偿的同步累积误差抑制方法,通过补偿晶振偏移,提供连续精准的高频采样时钟,消除各节点间采样间隔差异,在连续数据采集过程中保持同步精度,实现机械振动无线传感器网络高精度同步采集。

1 连续高频采样时钟ADC的WSN采集节点

基于连续高频采样时钟ADC的WSN节点硬件架构,如图1所示。采用双核心处理架构,核心1 STM32F405负责信号采集和数据处理,核心2 CC2530负责网络的组建和维护,两者协同工作,减少采集控制和网络维护的耦合性。设计低噪声电源管理方案,隔离数字电路和模拟电路噪声串扰;采用IEPE加速度传感器,提高采集信号的信噪比;设计截止频率动态可调的抗混叠低通滤波器和信号差分化的信号调理电路,有效滤除高频噪声和抑制共模干扰。采用专用于振动分析的24 bits SAR ADC AD7766-1,最高采样频率为64 kHz,具有10.5 mW的超低功耗,提高模数转换精度。在保证信号采集幅值精度和频率精度的前提下,兼顾了节点功耗和晶振偏移补偿对微控制器的处理性能要求。

机械振动无线传感器网络节点的采样时钟一般由微控制器内部定时器提供,或者由独立外部晶振引入微控制器内部分频获得,两种方式都需要晶振提供时钟。本文WSN节点的采样时钟由微控制器内部定时器提供,采样时钟获取流程如图2所示。首先外部晶振时钟经过微控制器内部锁相环(Phase Locked Loop,PLL)倍频得到系统时钟,然后通过预分频器获得外设时钟,最后通过定时器分频获得控制ADC模数转换的采样时钟。

图2 WSN节点采样时钟获取流程Fig.2 The acquisition process of sampling clock for WSN node

基于连续高频采样时钟ADC的WSN节点同步累积误差产生原因,如图3所示。晶振的振荡频率会随着外部环境(如温度等)的变化而产生偏移,使采样时钟产生偏移,造成同一采集节点不同时刻的采样间隔出现偏差(Δt1≠Δt5);同一型号晶振的频率特性也存在差异,使各采集节点间的采样时钟存在差异,导致不同采集节点的采样间隔不相等(Δt1≠Δt2≠Δt3≠Δt4)。随着采集过程的进行,采样间隔的差异会逐渐累积,高精度同步触发采集的同步精度逐渐丢失,造成同步累积误差,即Δe2, Δe3, Δe4。基于连续高频采样时钟ADC的采集节点,在一个采样间隔内需要多个连续精准的采样时钟脉冲,各采集节点间采样时钟同步,才能保证采样间隔的一致性以及采样的准确性。因此,为在连续数据采集过程中保持同步精度,需要对晶振偏移进行补偿,使各节点间采样时钟同步,避免同步累积误差。

图3 同步累积误差产生原因Fig.3 The reason of synchronous accumulated error

2 晶振偏移补偿的同步累积误差抑制方法原理

无线通信协议采用TI公司设计的IEEE 802.15.4协议栈TIMAC,在信标使能模式下,网关节点周期性发送信标,无线模块将信标中的帧起始界定符(Start of Frame Delimiter, SFD)信号直接在物理层传输到采集模块,减少SFD信号在协议栈层与层之间通信的随机迟滞,节点间SFD信号最大延迟误差的平均值为72 ns,可利用SFD信号作为同步信息。

晶振偏移补偿的同步累积误差抑制方法原理,如图4所示。网关节点周期性发送信标,采集模块定时器1捕获信标中的SFD信号并记录捕获时间,同时SFD信号触发外部中断,在外部中断服务程序中读取和保存定时器1的捕获时间,并计算出当前SFD信号间隔。由定时器1测得的SFD信号间隔与参考SFD信号间隔差值即是由晶振偏移引起。由于采样时钟频率大于采样频率,考虑到采集节点的处理性能,设置定时器1的频率与采集节点采样频率相同而不是与采样时钟频率相同。根据SFD信号间隔差值,调整定时器1的计数溢出值,进行晶振偏移补偿,使各节点间定时器1的时钟频率同步,然后根据采样频率与采样时钟之间的比值关系,计算定时器2各个时钟脉冲的计数溢出值,最后由定时器2输出补偿后的采样时钟fMCLK,消除节点间采样间隔差异,抑制同步累积误差。

图4 晶振偏移补偿的同步累积误差抑制方法原理Fig.4 Synchronous accumulated error suppression method theory based on crystal offset compensation

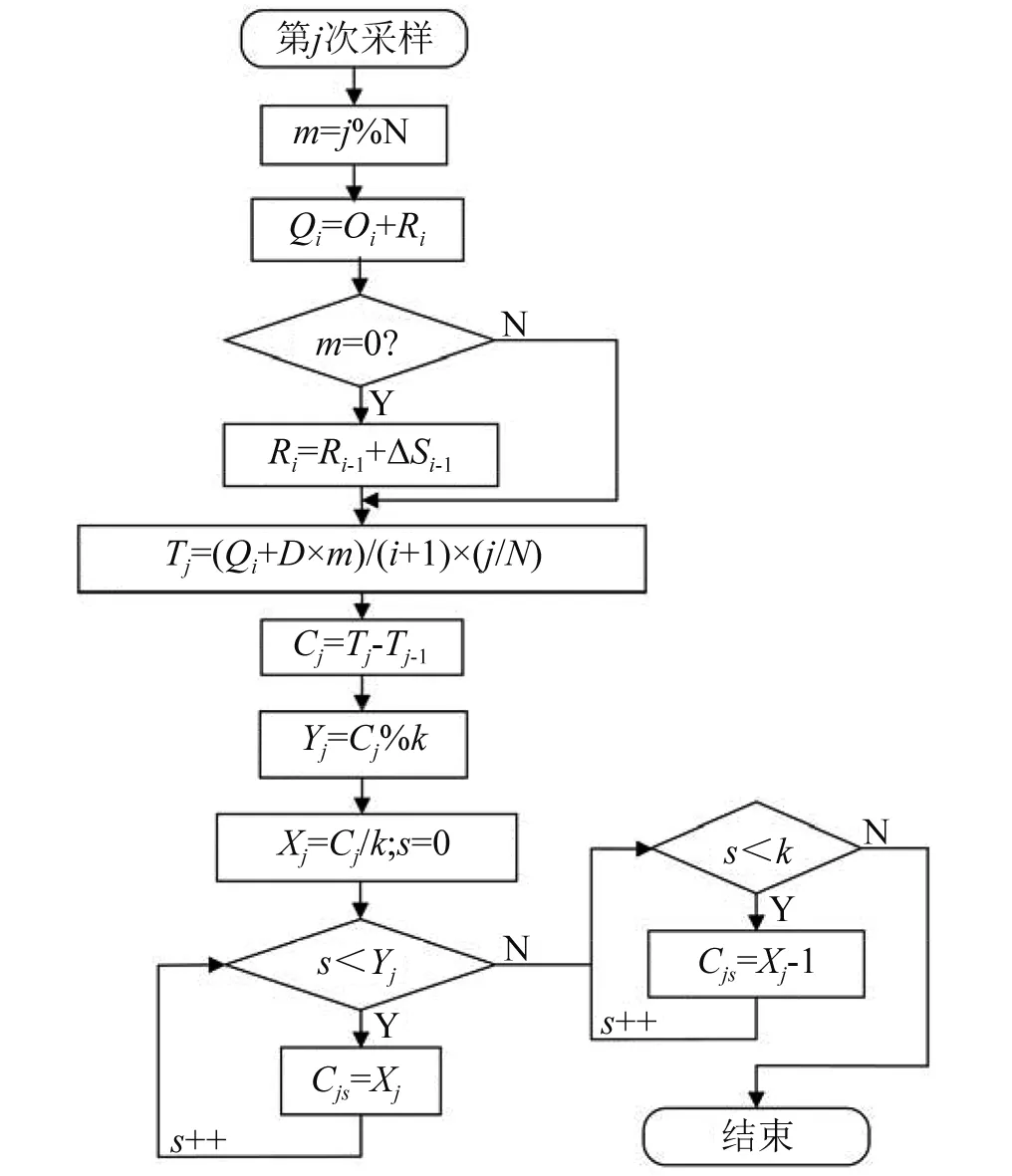

3 晶振偏移补偿的同步累积误差抑制流程

节点接受到采集命令,完成同步触发后开始采集,晶振偏移补偿的同步累积误差抑制流程,如图5所示,以最近一次SFD信号间隔S0作为参考,由于晶振偏移影响,之后的SFD信号间隔Si会与S0有偏差。 假设第j次采样在第i+1个SFD信号间隔内, 第i次SFD信号间隔与参考值的偏差为: ΔSi=Si-S0, ΔSi可为负数。 在第i+1个SFD信号间隔中对ΔSi进行补偿,则每个采样间隔需要补偿的计数值为

D=ΔSi/N

(1)

式中:N为参考SFD信号间隔内理论采样次数。

图5 晶振偏移补偿的同步累积误差抑制流程Fig.5 Flow chart of synchronous accumulated error suppression methed based on crystal offset compensation

在i个SFD信号间隔内定时器1理论计数总次数为Oi=i×S0, 补偿后的计数总次数为

Qi=Oi+Ri

(2)

式中:Ri为i个SFD信号间隔内的补偿计数值总和, 当m=j%N=0时进行更新Ri=Ri-1+ΔSi-1,m为第i+1个SFD信号间隔内的采样次数。

第j次采样时定时器1补偿后的计数总次数为

(3)

那么第j次采样定时器1计数溢出值Cj=Tj-Tj-1, 更新定时器1计数溢出值,补偿晶振偏移。

假设采样时钟频率与采样频率的比值为k, 那么在一个采样间隔内,定时器2需精确输出k个时钟脉冲。每次更新定时器1的计数溢出值后,需同时更新k个定时器2的计数溢出值,并且k个定时器2的计数溢出值的计数总次数为Cj, 避免定时器1和定时器2的时钟产生相位误差。那么第j次采样时,更新定时器2的k个时钟脉冲计数溢出值根据式(4)和式(5)计算

Xj=Cj/k

(4)

Yj=Cj%k

(5)

式中:Yj个计数溢出值为Xj,k-Yj个计数溢出值为Xj-1。

4 实验验证

4.1 同步采集精度测试

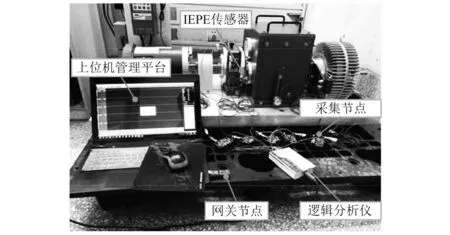

为验证本文提出的基于晶振偏移补偿的同步累积误差抑制方法的有效性,以5个采集节点和1个网关节点构成星型网络进行同步采集实验,实验布置现场如图6所示。节点采样频率设置为50 kHz,设置逻辑分析仪采样频率为100 MHz(最小分辨率为10 ns),用逻辑分析仪采集ADC的采样时钟信号,分析各节点采样时钟时序变化,计算同步误差。5个采集节点连续采集40 s,以节点1的采样时钟为基准信号,其他节点与节点1的采样时钟偏差即为该节点与节点1的同步误差。

图6 同步采集精度测试Fig.6 Synchronous acquisition accuracy test

未进行晶振偏移补偿的同步误差,如图7所示,同步误差随着采集时间的推移而累积,当采集时间到40 s时,最大同步误差在节点3~节点1达到255.4 μs,节点2和节点5与节点1的同步误差基本一致,说明节点2和节点5的晶振特性类似,但与其他节点晶振特性仍然有较大差异。

图7 未晶振偏移补偿的同步误差Fig.7 Synchronous aequisition error with crystal offset not compensated

采用本文方法对晶振偏移进行补偿后的同步误差测试结果如图8所示,节点间最大同步误差为0.64 μs,同步误差没有随着采集时间的推移而累积,验证了本文晶振偏移补偿方法抑制同步累积误差的有效性。

图8 晶振偏移补偿后的同步误差Fig.8 Synchronous aequisition error with crystal offset ompensated

4.2 同一信号源同步采集测试

为验证本文同步累积误差抑制方法对实际信号同步采集性能,用Agilent 33522A函数信号发生器产生频率为3 125 Hz,峰峰值为100 mV的标准正弦信号,将此正弦信号同时接入两个采集节点,设置节点采样率为50 kHz,连续采集25 s,对未采用本文方法和采用本文方法采集到的信号时域波形进行对比分析。

未采用本文同步累积误差抑制方法的两采集节点前35点时域信号波形如图9(a)所示,第1 000 000点(20 s)后的35点的时域波形如图9(b)所示。在前35点,由于采用同步触发方法,两节点几乎同时采集,时域波形无明显相位误差,但在第1 000 000点后的35点,两节点的时域波形已经有明显的相位误差,是因为没有进行晶振偏移补偿,同步误差逐渐累积。

图9 未晶振偏移补偿时域波形Fig.9 The time-domain waveform with crystal offset not compensated

采用本文同步累积误差抑制方法的两采集节点前35点时域信号波形如图10(a)所示,第1 000 000点后的35点的时域波形如图10(b)所示。可以看出两采集节点在前35点和第1 000 000点后的35点的时域波形都没有明显的相位误差,表明同步精度没有随着时间的推移而降低,同步误差没有累积,本文提出的晶振偏移补偿方法可以在连续数据采集过程中保持同步精度。

图10 晶振偏移补偿后时域波形Fig.10 The time-domain waveform with crystal offset compensated

5 结 论

为解决采用连续高频采样时钟ADC的机械振动无线传感器网络节点存在同步累积误差的问题,分析基于此类采样模式ADC的WSN节点的同步累积误差原因,提出了一种基于晶振偏移补偿的同步累积误差抑制方法,采用一个外部中断和两个定时器处理网关节点周期性发送信标中的SFD信号,利用SFD信号作为时间基准补偿晶振偏移,获得连续精准的高频采样时钟,消除节点间采样间隔差异,抑制同步累积误差。通过实验测试,连续采集40 s,节点间最大同步误差为0.64 μs;采用本文方法的两个采集节点在连续采集同一信号源过程中没有出现明显相位误差。以上结果表明,本文提出的晶振偏移补偿方法能有效抑制机械振动无线传感器网络同步累积误差。