基于FPGA的CIC滤波器设计

1 引言

在软件无线电中,数字线变频器接收经过高速采样的中频数字信号,将所需的频带下变到基带。它一般位于信号处理链的前端,靠近A/D。它主要由数字振荡器、数字乘法器、数字滤波器三部分组成[1-3]。DDC( Digital Down Converter,数字下变频)中数字滤波器的主要作用是抽取、低通滤波,一般由FIR滤波器实现。但FIR滤波器需要大量的乘法器,且一般DDC中的采样速率很高,因此FIR滤波器需要工作在很高的频率,使用资源多、功耗大。鉴于此,当前的专用DDC芯片中,一般采用了一种高效的滤波器---CIC滤波器作为第一级滤波器,实现抽取、低通滤波;第二级则采用一般的FIR或FIR实现的特殊滤波器,此时它们工作在较低的频率下,且滤波器的参数得到了优化,因此更容易以较低的阶数实现,节省资源,降低功耗[4-6]。

CIC(Cascade Integrator Comb) Filter,即级联积分梳状滤波器,是一种在多速率信号处理中广泛应用的高效抽取或内插滤波器。它具有只需加法器,不需要乘法器,运算速度快,易于工程实现等特点。本文在研究CIC滤波器基本原理的基础上,重点研究CIC滤波器设计方法,分析CIC滤波器级联级数和滤波器阶数的选取对通带衰减和旁瓣抑制的影响,并通过QuartusII软件仿真CIC滤波器,在FPGA芯片中实现该功能。

2 软件无线电的基本结构

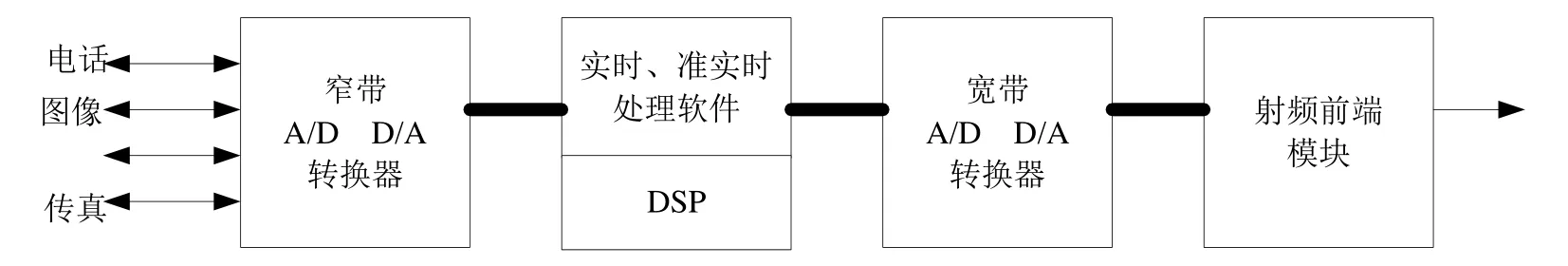

软件无线电的基本思想是以一个通用、标准、模块化的硬件平台为依托,通过软件编程来实现无线电台的各种功能,从基于硬件、面向用途的电台设计方法中解放出来。功能的软件化实现势必要求减少功能单一、灵活性差的硬件电路,尤其是减少模拟环节,把数字化处理尽量靠近天线。软件无线电强调体系结构的开放性和全面可编程性,通过软件的更新改变硬件结构的配置结构,实现新的功能。软件无线电采用标准的、高性能的开放式总线结构,以利于硬件模块的不断升级和扩展[7-10]。软件无线电系统的组成结构如图1所示。

图1 软件无线电结构框图

3 积分梳状(CIC)滤波器

高分解速率滤波器有一种非常有效的结构,就是由Hogenauer引入的积分梳状(cascade integrator comb,CIC)滤波器。CIC滤波器是一种基于零极点相消得FIR滤波器,已经被证明是在高速抽取或插值系统中非常有效的单元。一种应用就是无线通信,其中以RF(Radio Frequency,射频)或者IF(Intermediate Frequency,中频)为采样速率的信号需要降低到基带。在窄带应用中,抽取比率经常需要超过1000,这样的系统通常称作信道器。另一个应用领域就是数据变换[4,5]。

CIC滤波器的基础是完美的极点零点抵消,要实现这样一个事实,只有使用精确地积分算法才是唯一可行的。二进制补码和余数系统都具有支持无误差算法的能力。二进制补码是目前DSP领域内最为流行的有符号数字表示方法,二进制补码表示法使得累加多个有符号数值成为可能,这样就可以在N为范围内,忽略任何算术意义上的溢出。二进制补码可以用来实现模算法,而且不需要在算法中做任何改动。

3.1 单级CIC滤波器的原理

CIC(Cascade Integrator Comb) Filter是一种在多速率信号处理中广泛应用的高效抽取或内插滤波器。它具有只需加法器,不需要乘法器,运算速度快,易于工程实现等特点。所谓积分梳状滤波器,是指该滤波器的冲激响应具有如下形式:

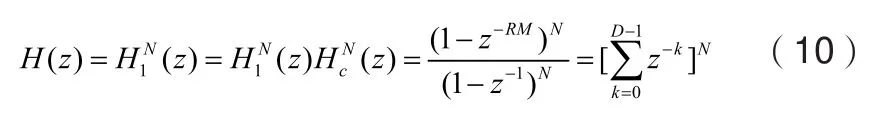

式中,D即为CIC滤波器的阶数,也就是抽取因子,根据Z变换的定义,CIC滤波器的Z变换为:

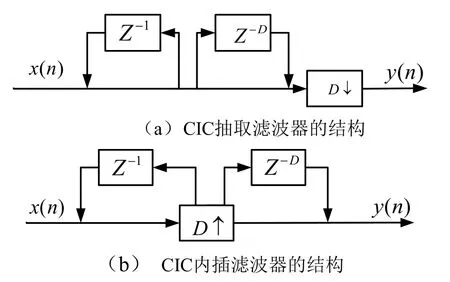

它的实现框图如图2所示,由图可见,CIC滤波器有两部分组成,积分器和梳状器滤波的级联。

图2 单级CIC滤波器的基本结构

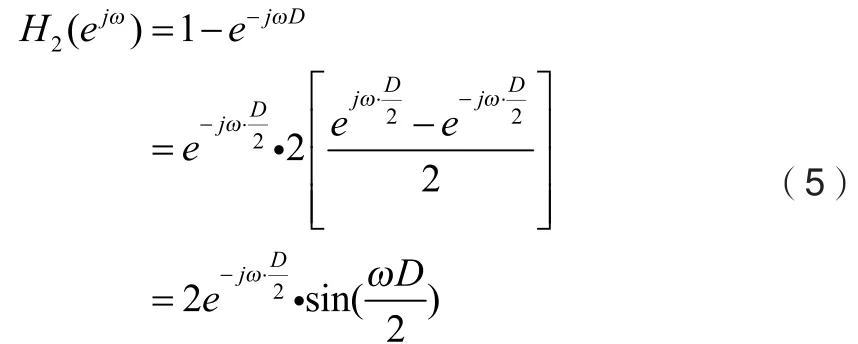

所以整个CIC滤波器的频率响应为:

可见单级CIC滤波器的旁瓣电平是比较大的,只比主瓣低13.46dB,这也就意味着阻带衰减很差,一般是难以满足使用要求的。为了降低旁瓣电平,可以采用多级CIC滤波器级联的办法来解决。

图3 CIC的幅频特性

3.2 多级CIC滤波器的原理

N级CIC滤波器的传输函数为:

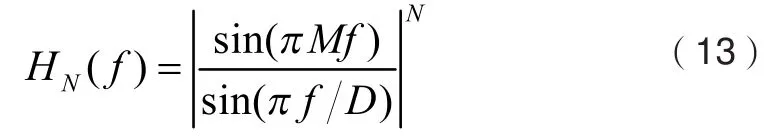

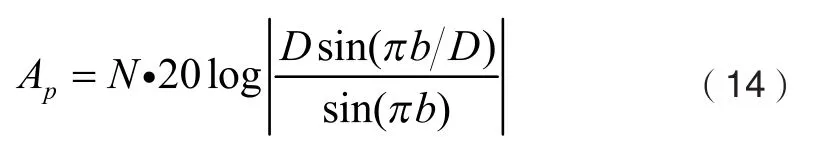

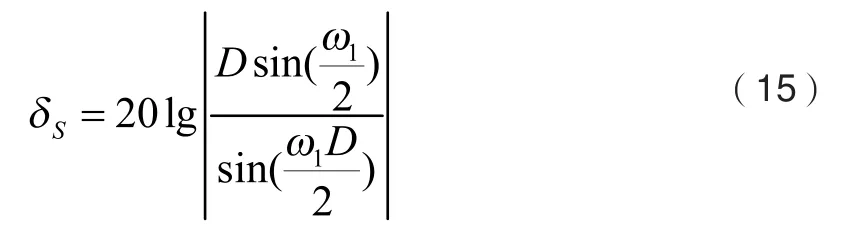

式中M是梳状部分中延迟的数量,R是向下抽取因子。相应N级CIC滤波器的频率响应为:

在构造N级CIC滤波器时,只需把N级积分器的输出和N级梳状器输入串联起来,就构成了多级的CIC滤波器。

也就是说从带内平坦度考虑,带宽因子b也不能选得太大,或者说信号带宽不宜选得太宽,否则会引起高频失真,这显然是不允许的。同理我可以得到N级的CIC滤波器的带内容差为:

也就是说N级CIC滤波器的带内容差是单级的N倍。从上面的分析可以看出,CIC滤波器无论是阻带衰减还是带内容差只与带宽比例因子有关,或者说只与相对信号带宽(相对于输出采样率的信号带宽)有关,而与绝对信号带宽无关。这样在绝对信号带宽较宽时,可以通过降低抽取因子D来提高输出采样率,从而达到减小相对信号带宽,也就是减少带宽比例因子b的目的。

4 CIC滤波器的FPGA实现

编写CIC内插滤波器的梳状部分时,需要有一个延迟,再利用减法器来实现。而积分部分,则是在计数开始时将梳状部分的值输到端口中然后进行累加输出。Quartus II输出结果如图4所示。

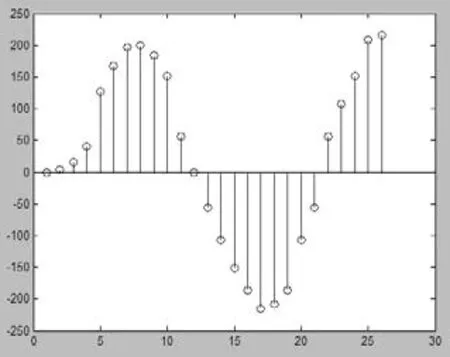

将生成的结果用Matlab编程导出,得到的结果如图5所示。

图4 Quartus II仿真波形

图5 CIC滤波器输出结果的波形

5 总结

本文主要研究了四级CIC内插滤波器,该滤波器有以下优点:结构规则,只有加法器和减法器,没有乘法器,不需要寄存器来存储滤波系数;只有极少的外部控制,对时钟的要求也不高;通过提高数据速率的处理,减少了中间存储环节;通过改变内插率因子R,可以实现不同滤波器的设计;频域特性可预测,可以方便地用一个FIR滤波器来补偿,产生平坦的通带,增大阻带衰减。随着R的增大,滤波器中寄存器的位数也就必须相应地增加,并且,因为CIC滤波器的频率响应仅由参数R、N、M决定,其特性必然会受到一定的限制,所以经常需要和其它的FIR滤波器配合使用。通过结果分析,可以看出CIC内插滤波器的作用是在采点较少的输入信号中加入一系列的数可以使波形的输出更加的完善,提高了采样速率,在软件无线电中具有重要的应用价值。