一种基于卡尔曼滤波算法的高精度 时间频率同步器研制

赵越,华宇,金晓臻

(1.中国科学院 国家授时中心,西安 710600;2.中国科学院 精密导航定位与定时技术重点实验室,西安 710600;3.中国科学院大学,北京 100049)

0 引言

时间是自然界中一个最基本的物理量,是描述物体运动的基础。高精度的时间比对技术是随着科技的进步和时间服务精度的不断提高而逐步发展起来的。近几年来,国家经济快速发展和综合国力日益增强,各行各业对高精度时间频率传递技术要求也越来越高。比如在卫星导航定位系统中,精确位置测量实际上是精确时间的测量,如果没有高精度的时频,卫星导航定位系统就不可能实现高精度的导航与定位[1]。特别是在国防和空间技术领域,对时间同步精度的要求已达到纳秒量级。所以急切需要开展高精度时间频率技术的应用和研究。本文所设计的高精度时间同步器是利用GPS或北斗高精度定时接收机输出的1 PPS信号作为外部参考时间源,利用10 MHz高稳晶振产生本地1 PPS信号,实时测量以上两路1 PPS信号之间的相位差,完成对本地高稳晶振输出频率的建模,然后对晶振的相位/频率进行预测控制,完成本地频率的高精度保持以及本地1 PPS信号与参考1 PPS的高精度同步。

1 工作原理

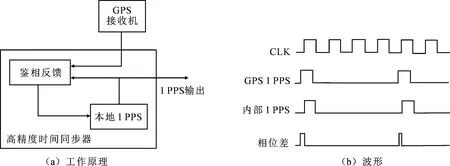

高精度时间同步器的工作原理如图1(a)所示,主要由鉴相反馈与本地1 PPS两功能模块组成。时间同步器内部采用原子钟或超稳晶振作时钟源,经分频输出作为本地1 PPS信号。鉴相反馈主要是指接收来自GPS接收机与本地的1 PPS信号,对其进行相位比对处理,将结果输出至本地1 PPS控制本地输出1 PPS信号的相位,从而达到与GPS的1 PPS信号的同步。鉴相反馈是整体系统的核心部分,分为两级反馈。其中一级反馈基于FPGA(field programmable gate array)计数,控制精度为10 MHz系统时钟周期即100 ns,二级反馈基于可编程线延迟芯片DS1023,最小控制精度达0.25 ns。波形如图1(b)所示,内部1 PPS为一级反馈后的输出,与GPS接收机的1 PPS仍会有小于一个时钟的相位差;输出1 PPS信号为二级反馈后的信号。高精度时间同步器的同步精度取决于相位对比的分辨能力与对本地1 PPS调节的能力。

图1 高精度时间同步器工作原理

2 系统设计

高精度时间同步器系统设计主要分为两个部分。第1部分为硬件设计,主要介绍系统所采用的各个器件及其功能;第2部分为软件设计,介绍了高精度时间同步器系统的核心算法与处理流程。

2.1 系统硬件设计

高精度时间同步器系统硬件框图如图2所示。利用GPS和北斗高精度定时接收机输出的1 PPS信号作为外部参考时间频率源,其主要硬件包括:用于测量相位差的TDC-GP1芯片,主控芯片为FPGA与ARM-STM 32[2-3],用于调节输出标准频率相位的时延芯片DS1023。

主控芯片是整个系统的控制核心,负责整体系统中各个部分的协调管理、相位差数据采集以及包含本文研究算法的数据处理与运算任务。本文设计的系统中的主控芯片为ARM-STM32,M3系列,型号为STM32F102ZE,主要负责接收相位差测量数据并进行处理,之后与FPGA通信,使其对电压、分频等参数进行一定调节。STM32是一款精简指令集的单核单芯片控制器,芯片内部集成了丰富的资源;其外部接了一个8 MHz的晶体振荡器,通过内部锁相环倍频为72 MHz,具有非常快的运算速度。其功耗小,性价比高,外部引脚标准电平为3.3 V,可以很方便地与FPGA以及TDC-GP1直接进行通信。

图2 高精度时间同步器系统结构

FPGA的时钟由铷钟10 MHz信号提供,经过内部分频模块10 MHz分频,为1 PPS信号。关于整体系统的伺服反馈系统分为粗调节与精细调节两部分。其中粗调节为根据ARM传至FPGA的数据,对FPGA内部分频模块的系数进行调节。因为是10 MHz分频,系统时钟为10 MHz,所以调节精度为100 ns。通过粗反馈可将时间同步在百纳秒量级[4]。

鉴相功能由TDC-GP1芯片完成。脉冲相位差可用两个脉冲上升沿的时间差表示,通常采用计数器实现这一功能。考虑小型化和技术成本的要求,本文采用德国 ACAM 公司研发的时间间隔测量芯片实现时间间隔的数字化测量。该芯片可提供两通道250 ps 或单通道 125 ps 分辨率的时间间隔测量; 每个通道可采样4次,测量范围3 ns ~200 ms。我们用TDC-GP1对本地1 PPS与GPS的1 PPS信号进行相位测量,测出它们之间上升沿的时间差。所得数据由ARM接收,在ARM中进行处理分析,最后对FPGA进行反馈控制[5]。

精细调节部分采用了DS1023芯片。DS1023芯片是DALLAS公司的8位可编程延迟线,步进调整分辨率0.25 ns。管脚通信电压3.3 V或5 V,可以通过并行或者串行SPI协议很方便地与控制芯片进行通信。本文设计中采用DS1023完成本地1 PPS信号精细调节。FPGA接收ARM的数据之后,经过处理,与DS1023通过SPI协议进行延迟配置,从而使最终输出的1 PPS与GPS的1 PPS信号达到高精度的时间同步,同步精度纳秒级。

2.2 系统的软件设计与开发

本文设计的时间同步系统开机后的工作流程如下。系统开机上电后,首先,系统会进入一段闲置的时间延迟,一方面为了使压控晶体上电后进行开机预热;另一方面需要等待主控制器与GPS初步通讯,发出同步命令,使系统能够稳定地接收到GPS的1 PPS信号并将其作为本地的同步信号。其次,主控制器进入正常工作状态,打开中断,循环地接收由TDC-GP1测得的相位差数据,进行结合算法数字滤波等计算与处理,得到本地频率标准信号与GPS的1 PPS信号的时刻差与相对频差等估算值。最后,将处理的数据通过SPI总线协议发送至FPGA之后,FPGA通过改变内部分频模块的分频系数与DS1023的时延,实现整个系统的闭环控制功能,如此循环完成高精度时间的同步任务。

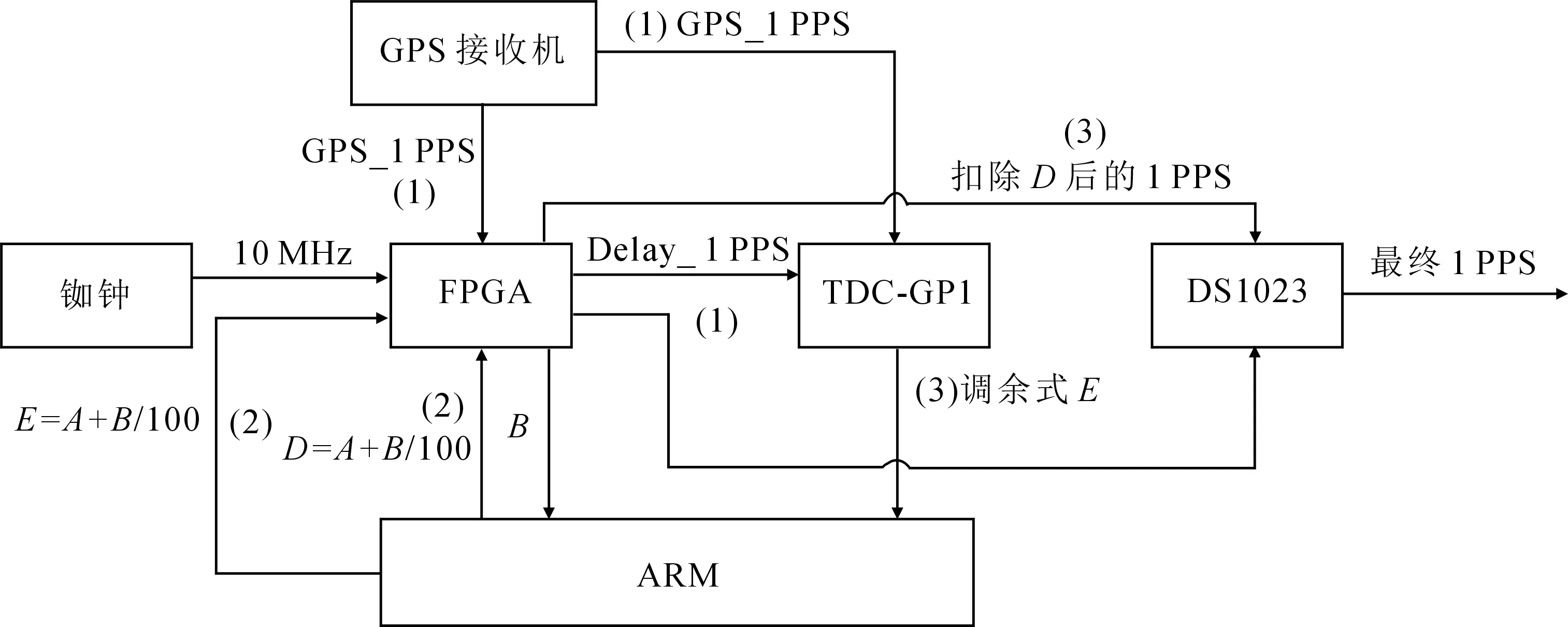

FPGA部分按照严格的开发、自测、测试流程进行设计[6],主要包括分频模块、DS1023驱动、数据处理模块与ARM_SPI模块,如图3(a)所示。其中分频模块是一个分频系数可调的累加器分频电路。ARM_SPI模块负责FPGA与ARM进行SPI总线协议通信,由1 bit时钟信号、1 bit片选信号以及4 bit数据信号组成,依次将需要控制FPGA内部分频器系数与DS1023数据以二进制发送至FPGA。FPGA接收数据后在数据处理模块内进行整理,利用分频系数对分频模块进行配置,将分频系数相关数据发送给DS1023模块,通过粗调与细调结合完成1 PPS信号相位的完美调整。在ARM的程序设计中,流程图如图3(b)所示。在上电复位之后,与TDC-GP1进行通信,得到本地1 PPS信号与GPS的1 PPS信号的相位差,之后进行处理。最后,将处理的数据通过SPI总线协议发送至FPGA之后,再次与TDC-GP1进行通信,如此循环[7-8]。

图3 FPGA内部分频模块及ARM程序流程

由于GPS接收机输出的1 PPS时间信号噪声较大,因此在接收GPS信号同步1 PPS的过程中,怎样在大噪声中提高信号的可靠性是设计中的难点。在传统设计中,基于最小二乘法的算法较为常用,它通过对受驯晶振进行反馈控制以提高输出信号的准确性与长期稳定性,这种方法缺点是控制过程需要大量钟差数据导致控制带宽较低、反应较慢,以至于出现异常时不能即刻纠正。在高精度时间同步中,由于环境噪声很大(噪声的阿伦方差是信号阿伦方差的成百上千倍),利用卡尔曼(Kalman)滤波[9-11]对信号进行估计,可有效提升时间同步的精度。利用卡尔曼滤波可重现系统的状态,经卡尔曼滤波后获得的结果,其实是量测值对系统状态向量的一种重构,通过量测值可实现对系统随机干扰的消除。当环境噪声很大时,采用卡尔曼滤波对信号进行估计,能够使测量数据变得平滑,从而有效提升时间比对的精度。此外,卡尔曼滤波是通过递推进行数据处理的,当前时刻的估计值仅来源于当前时刻的观测值以及上一采样时刻的估计值,与其他时刻的观测值以及估计值无关。因此,我们在ARM中的数据预处理部分采用了卡尔曼滤波算法,计算钟差的卡尔曼模型如公式(1)和(2)所示。

X(t+1)=AX(t)+q(t),

(1)

Z(t)=HX(t)+r(t)。

(2)

式(1)和(2)中,t为时间,X(t)由钟差X1(t)、频率偏移X2(t)、老化系数X3(t)组成。Z(t)为测量量,等于钟差X(t)。q(t)与r(t)为钟噪声,A与H分别为状态转移矩阵与观测测量矩阵,如公式(3)和(4)所示。

H=[1 0 0],

(3)

(4)

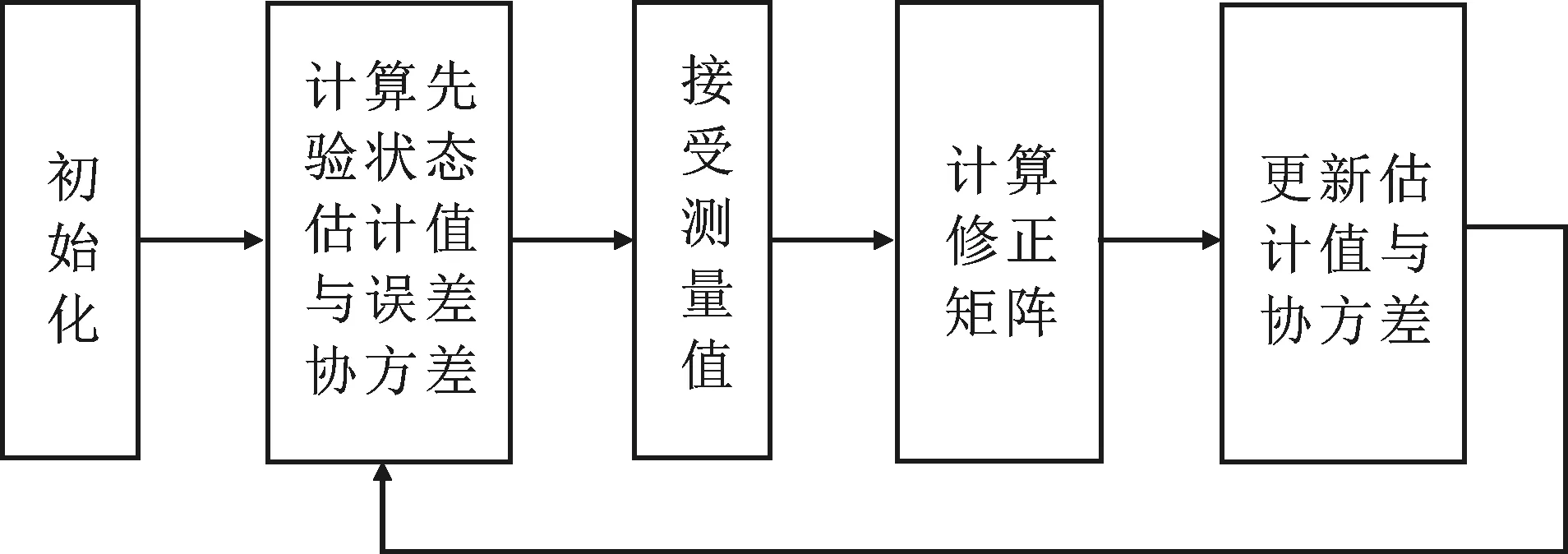

在ARM中,数据处理部分的流程如图4所示。在初次进行数据处理时,先对各个系数进行初始化赋值,之后计算下一时刻的估计值与误差协方差。在接收到实际测量数据之后,根据实际数据得到修正矩阵。最后更新估计值与误差协方差,将更新的值投入下一次运算之中,如此循环[12]。

图4 ARM内部数据处理部分流程

3 测试数据

目前初步完成3台高精度时间同步器的研制,并完成设备实验数据的采集和处理,分别进行性能比对测试,结果如下文所述。

3.1 1 PPS输出与标准1 PPS(UTC(NTSC))的比较

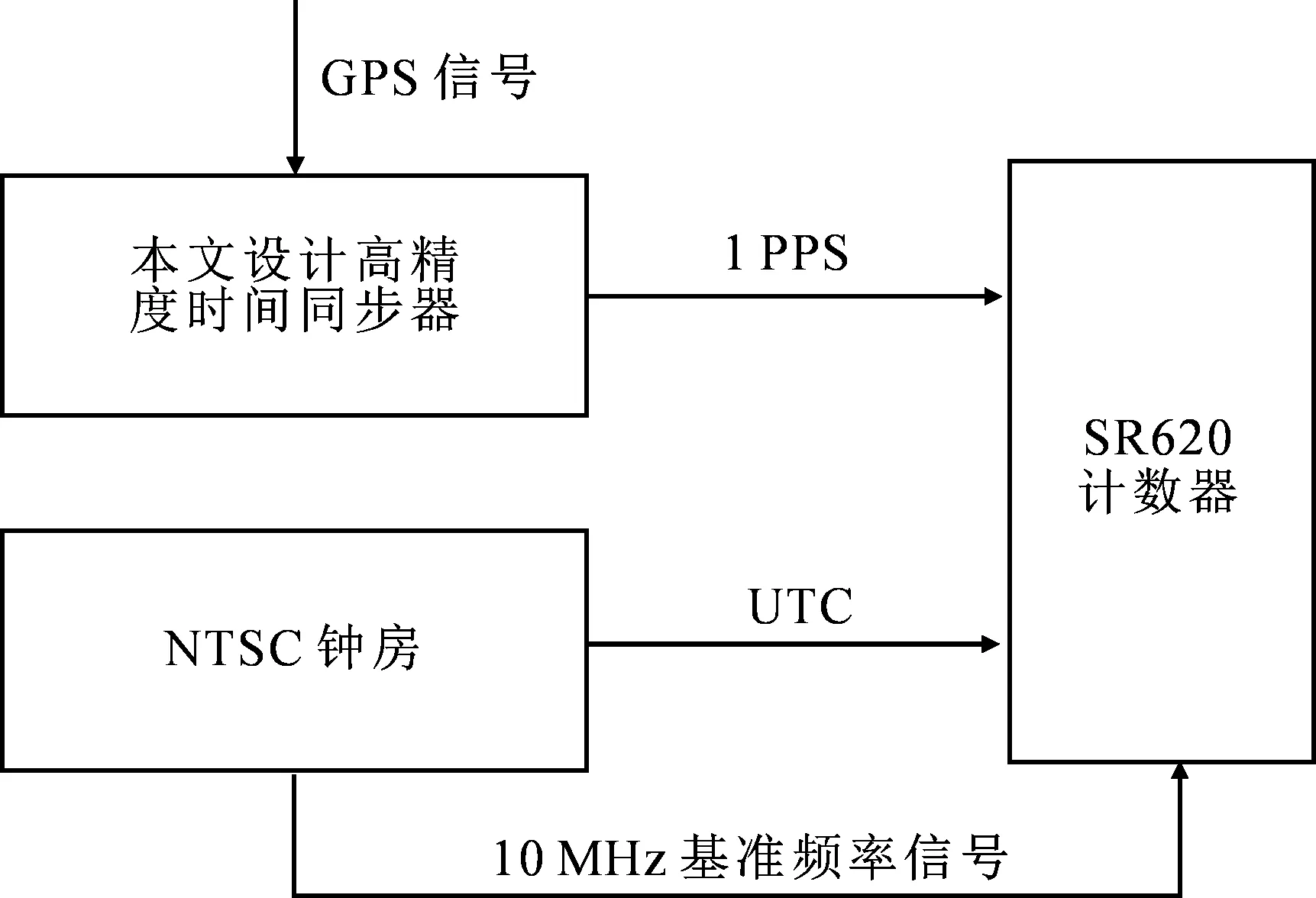

首先,我们将3台高精度时间同步器分别与钟房信号进行对比,其中钟房的时间延迟为1 682 ns。测试连接图如图5所示。

图5 时间同步精度测试原理图

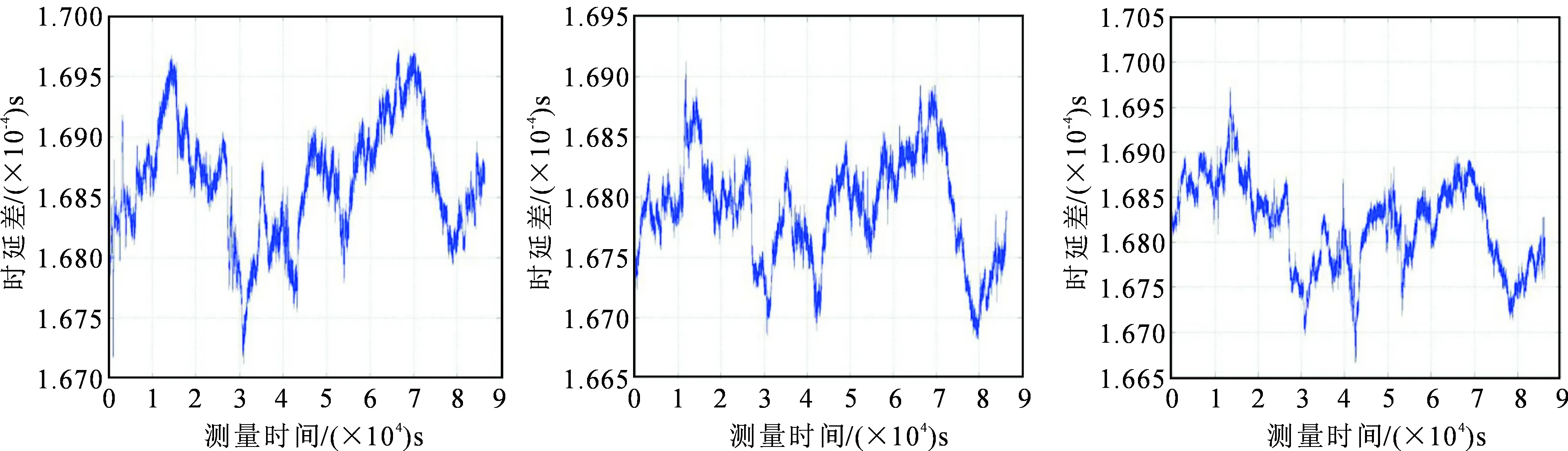

以NTSC钟房输出的标准1 PPS作为比对参考,分别与自行研制的3台高精度时间同步器进行了时间对比(钟房的时间延迟为1 682 ns)。时间比对结果如图6(横坐标为测量时间,单位为10 ks;纵坐标为同步器输出的1 PPS 与钟房输出的1 PPS时延差,单位为μs)所示,分别进行连续测量24 h,标准差分别为4.8,4.3和4.8 ns,3台同步器的同步效果较好。

图6 高精度时间同步器与钟房比对结果

3.2 不同设备同天线共电缆测试

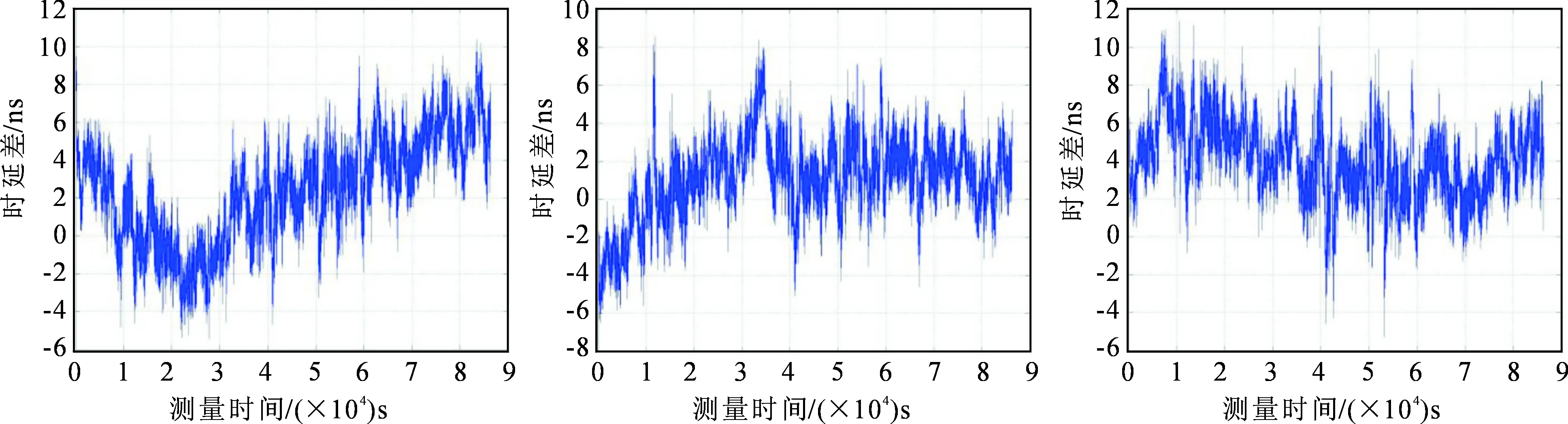

此外,我们将自行研制的3台高精度时间同步器两两之间进行对比测试。为了使外界干扰引起的测试误差降至最低,测试过程中将3台时间同步器的接收机天线以Y形放置在一起,使天线的位置近似相同,使用相同长度的电缆线。待所有同步器正常工作后开始连续测量24 h,每秒钟取得一次测量结果。测试结果如图7所示,其中图中横坐标为测量时间,单位为10 ks;纵坐标为3台同步器两两之间输出的1 PPS的时延差,单位为ns。

由数据可知两两比对测试的时间差均值分别为2.1,1.1和4.0 ns,方差分别为2.2,2.1和2.4 ns。测试结果表明,本文所设计的基于卡尔曼滤波算法的3台高精度时间同步器的时间同步功能实现较好。同时,由于3台同步器的内部硬件结构完全相同,数据处理方式一致,且比对结果存在的差异较小,因此,在允许的精度误差范围内可近似认为输出精度相同。

图7 高精度时间同步器间比对结果

4 总结

高精度时间同步器因其高精度的频率输出和时间同步性能,尤其适合应用在移动通信基站中;为基站其他设备提供高精度的频率源和时间同步。本文设计并研制了一种基于FPGA与ARM的高精度时间同步器,并在多台系统之间进行了比对测试。经测试表明,高精度时间同步器的同步功能效果较好。目前,该时间同步器主要采用 GPS 作为单一时间源,如果采用 GPS 和北斗双模时间源,并处理好两者之间时间源的相互切换,将会大大改善时间同步器工程应用的可靠性。