SDH E1时隙可配帧格式及数据编码的 设计与FPGA实现技术

池飞,武建锋,何在民

(1.中国科学院 国家授时中心,西安 710600;2.中国科学院 精密导航定位与定时技术重点实验室,西安 710600;3.中国科学院 时间频率基准重点实验室,西安 710600;4.中国科学院大学 电子电气与通信工程学院,北京 101048;5.中国科学院大学,北京 100049)

0 引言

随着通信、网络技术的不断进步,时间统一技术在SDH(synchronous digital hierarchy)光纤网络中的应用越来越广泛,但网络中网元设备内部晶振的精度较低,网元守时能力差,SDH光纤网络传统业务和新业务亟需实现整个网络的时间同步,以保证整个网络时间的高度统一。E1通道可靠性、稳定性高,可应用于SDH光纤网络的时间同步。E1是国际电联(ITU-T)制定并由欧洲邮政与电信协会(CEPT)命名的数字传输系统一次群(即PCM30)标准,E1通道的物理及电气特性符合CCITT(国际电报电话咨询委员会)的ITU-G.703标准,我国也采用E1标准作为PCM系统和N-ISDN的基群[1-4]。E1通道在国防、电力、通信、交通等领域得到广泛的应用,本文立足于用户实际需求,基于FPGA(field programmable gate array)工具,设计并实现了时隙可配的SDH E1帧格式及HDB3(high density bipolar)数据编码技术,通过实验,仿真验证其功能正确性[5-6]。

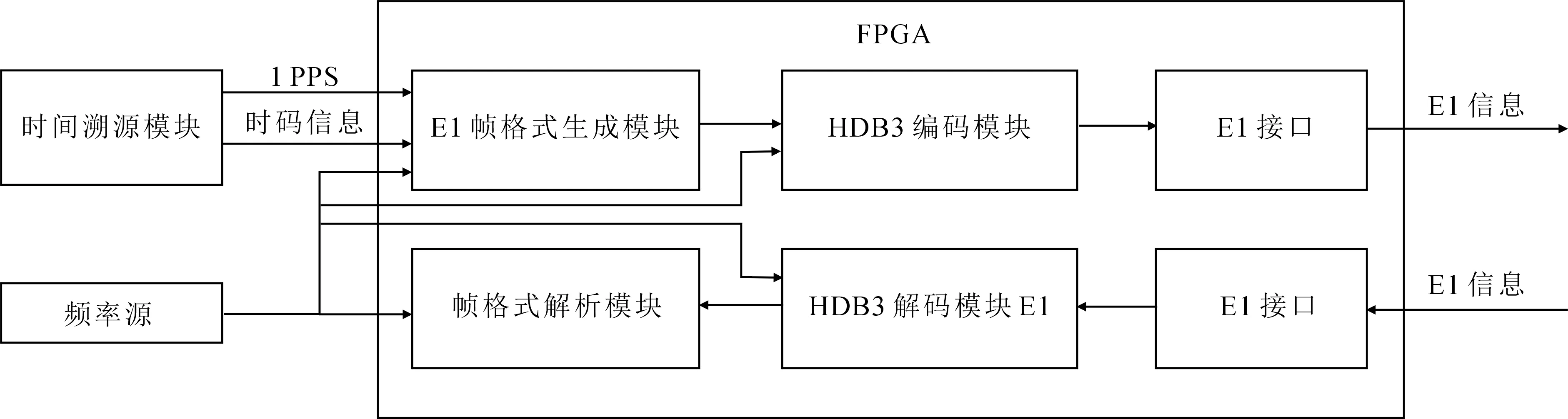

1 SDH E1时间同步系统设计

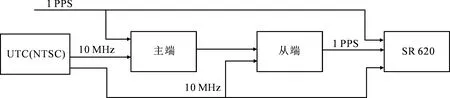

SDH E1时间同步系统总体框图如图1所示,FPGA集成相应的通信模块,与时间溯源模块进行通信,获取时码信息和1 PPS脉冲信号,同时外接10 MHz频率源作为外频标参考以驱动整个系统。FPGA系统用7位巴克码信息作为帧头来表示1 PPS以填充到对应时隙中,将其与时码信息进行组合,并配置成E1通道所规定的帧格式,利用HDB3编码模块将二元码变成适合在线路中传输的双极性码,最后通过E1通道将信息发送到下一个节点,SDH网络中另一端接收E1帧格式信号,经过HDB3解码,而后进行E1帧格式解析,从7位巴克码帧头中恢复1 PPS脉冲信号,即可在对端实现同步[7]。文中主要是设计并采用FPGA实现SDH E1线路中的帧格式生成和数据HDB3编码两个关键模块,采用Modelsim和Signal Tap II仿真工具,验证数据编码和帧格式生成的正确性。

图1 E1总体框图

2 E1帧格式及HDB3编码原理

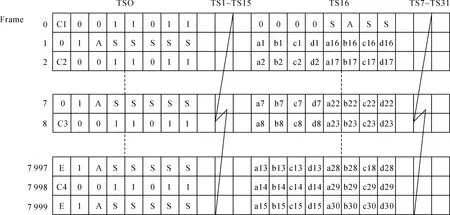

E1线路是一条基于时分复用的数字链路,它的数据传输速率为2.048 Mbit/s,整个线路由8 000个E1帧构成,每个E1数据帧由256 bit数据位构成,这256 bit的数据位又分为32个时隙(TS),每个时隙又包含8 bit的数据,即:8 bit×32×8 000=2.048 Mbit/s,这样,构成了整个E1线路[8-10]。我国和欧洲均采用2.048 Mbit/s的E1信号。

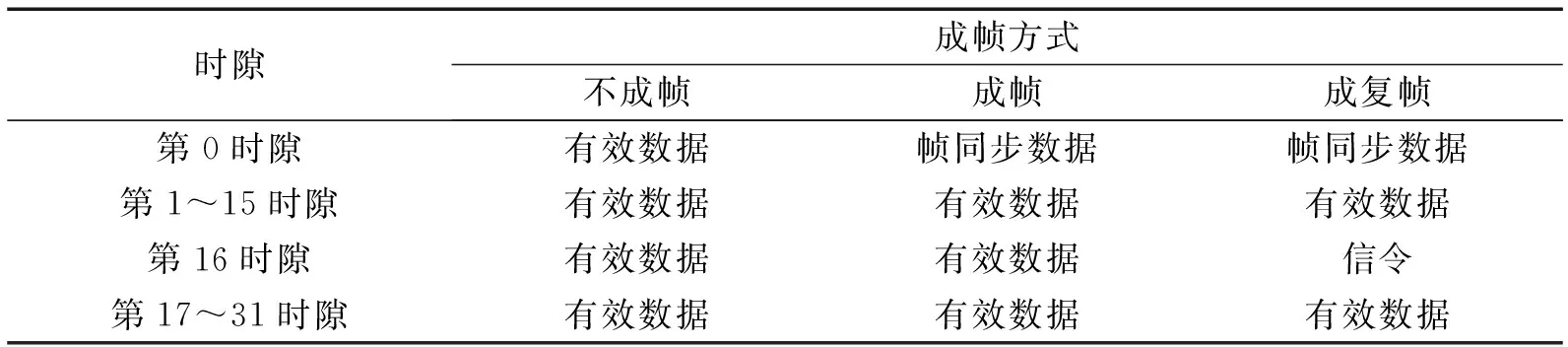

表1 E1帧格式

实际SDH网络应用中,核心业务数据传输一般采用成帧格式或成复帧格式[11-13]。进行系统时间同步时,时码信息传输可根据用户需求,在TS1~TS31 31时隙中的任意一个时隙灵活配置,帧格式如图2所示。

图2 E1帧格式

E1系统中,当输入信息被配置成规定的帧格式后,需要通过相应的编码才能更好的在整个系统中传输。根据CCITT的建议,E1线路中采用HDB3编码[14]。由于该编码方式不含直流分量,低频分量较少,同时含有定时信息。并且它改进了AMI码中出现过长的连“0”串造成信号电平长时间不跳变引起提取定时信息困难的问题。

HDB3编码规则如下:

①将二元码中的“1”进行极性交替,即完成“+1”和“-1”交替出现,变成AMI码;

②检查码中“0”的个数,当连“0”个数小于等于3时,HDB3码与AMI码一样,+1与-1交替;

③当连“0”个数超过3时,将每4个连“0”化作一小节,定义为B00V,成为破坏节,其中V成为破坏脉冲,而B成为调节脉冲;

④V与前一个相邻的非“0”脉冲的极性相同(这破坏了极性交替的规律,所以V成为破坏脉冲),并且相邻V码之间极性必须交替。V的取值为+1或-1;

《模拟电子技术》课程历年来大多数的学生觉得学习难度大,一些概念与原理比较难懂,为了提高该门课程的教学效果,在教学过程中积极探索了基于“雨课堂+互联网+PowerPoint”的在线混合式教学改革方法,不仅有利于了解学生的课前预习情况,也可以提高课堂的教学效果,大大改善了以往课堂教学沉闷的现象,还便于学生课后的复习,这种混合式的教学方法给予学生课前、课中、课后每个环节都有新的不同的体会与感受,并且充分的利用了智能手机的优势,让它更好地服务教学的方法,获得了广大学生的好评。

⑤B的可能取值可选0,+1或-1,以使V同时满足④中的两个要求;

⑥V码后面的传号码极性要交替。

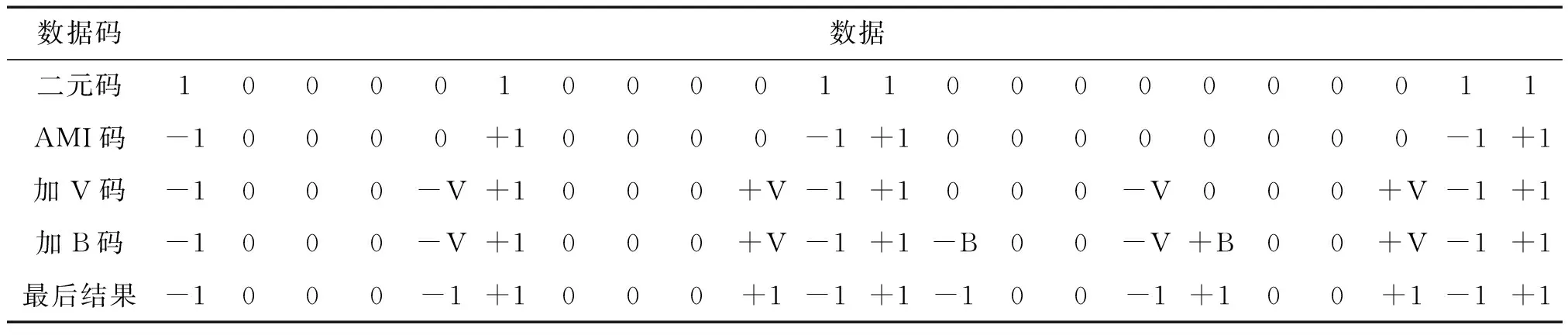

依据HDB3编码规则,对二元码“1000010000110000000011”进行编码,其对应过程序列及最终HDB3编码结果如表2所示。

表2 HDB3编码结果

总体来说,对于HDB3编码部分,可分为3个部分进行,包括:加“V”操作、加“B”操作、极性变换操作,其中的对应关系如表3所示。

表3 HDB3编码码型对应

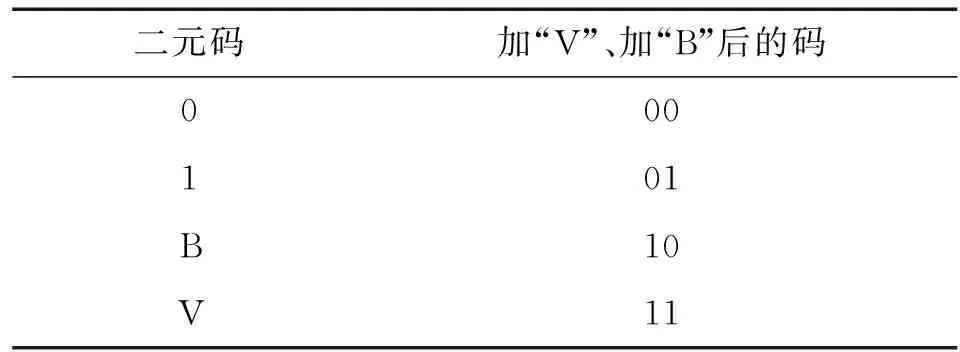

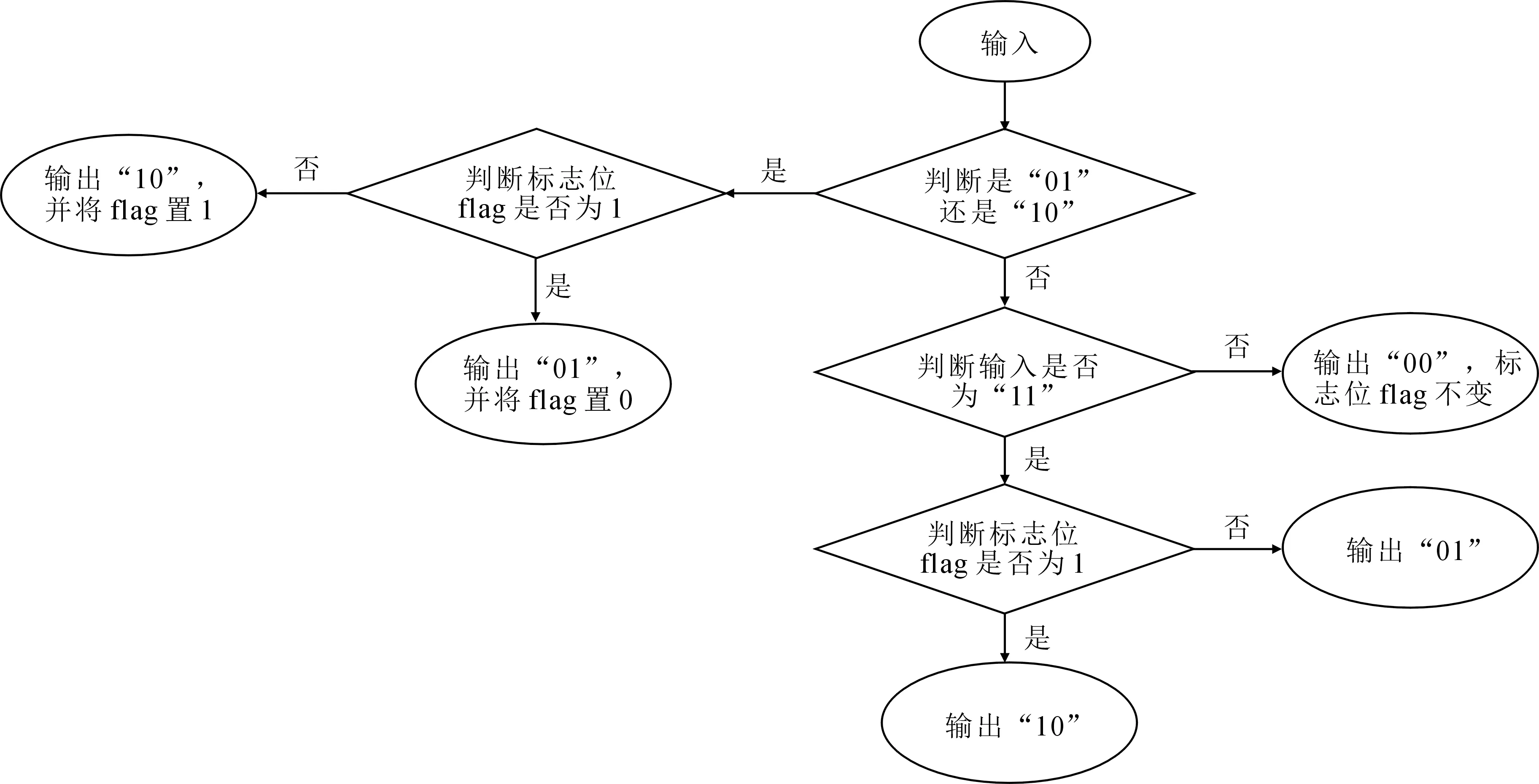

在加“V”操作中,主要是检测二元码中“0”的个数,一旦“0”的个数达到4个,就将第4个“0”变成破坏节“V”,具体的操作流程图如图3所示。

图3 HDB3编码加“V”操作流程图

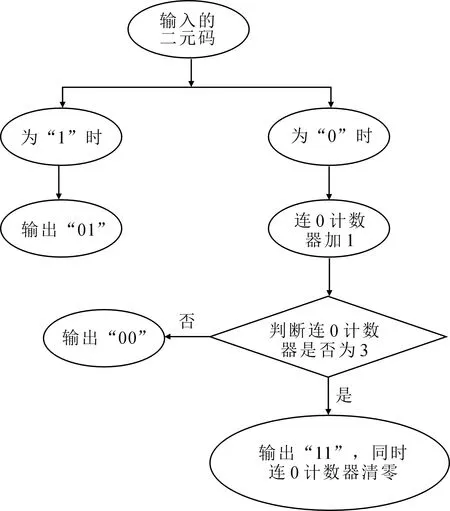

接下来就是加“B”操作,主要是检测相邻两个“V”之间有奇数个非“0”还是偶数个非“0”码,当非“0”码个数为偶数时,将“V”前面的第3个“0”变为“B”,具体流程图如图4所示。

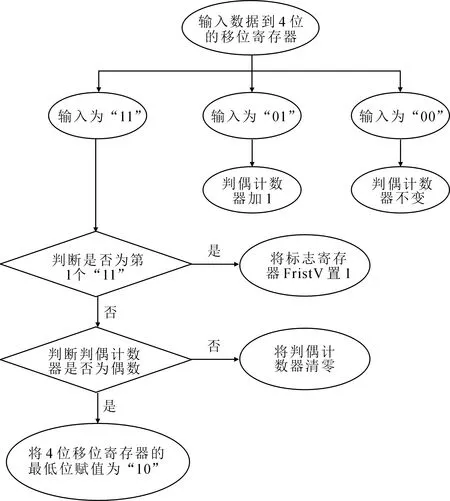

最后一部分为单双极性变换,整体思想是满足“V”的极性是正负交替的,同时满足“1”和“B”构成的整体也是正负交替的,流程图如图5所示。

图4 HDB3编码加“B”操作流程图

图5 HDB3编码极性变换流程图

3 E1帧格式实现

本文采用成帧的方式,即第0时隙用来传输帧同步信息,其他31个时隙传输有效信息。此处的帧同步信息是由7位巴克码“1110010”来表示,由1 PPS脉冲信号上升沿触发巴克码第1个码片的产生,由于此处用100 MHz作为时钟,故两者同步偏差在10 ns以内。由于巴克码是一种具有特殊规律的码组,有尖锐的自相关函数,与随机数字信息相区别,易于识别,故用巴克码作为帧头[15-18]。

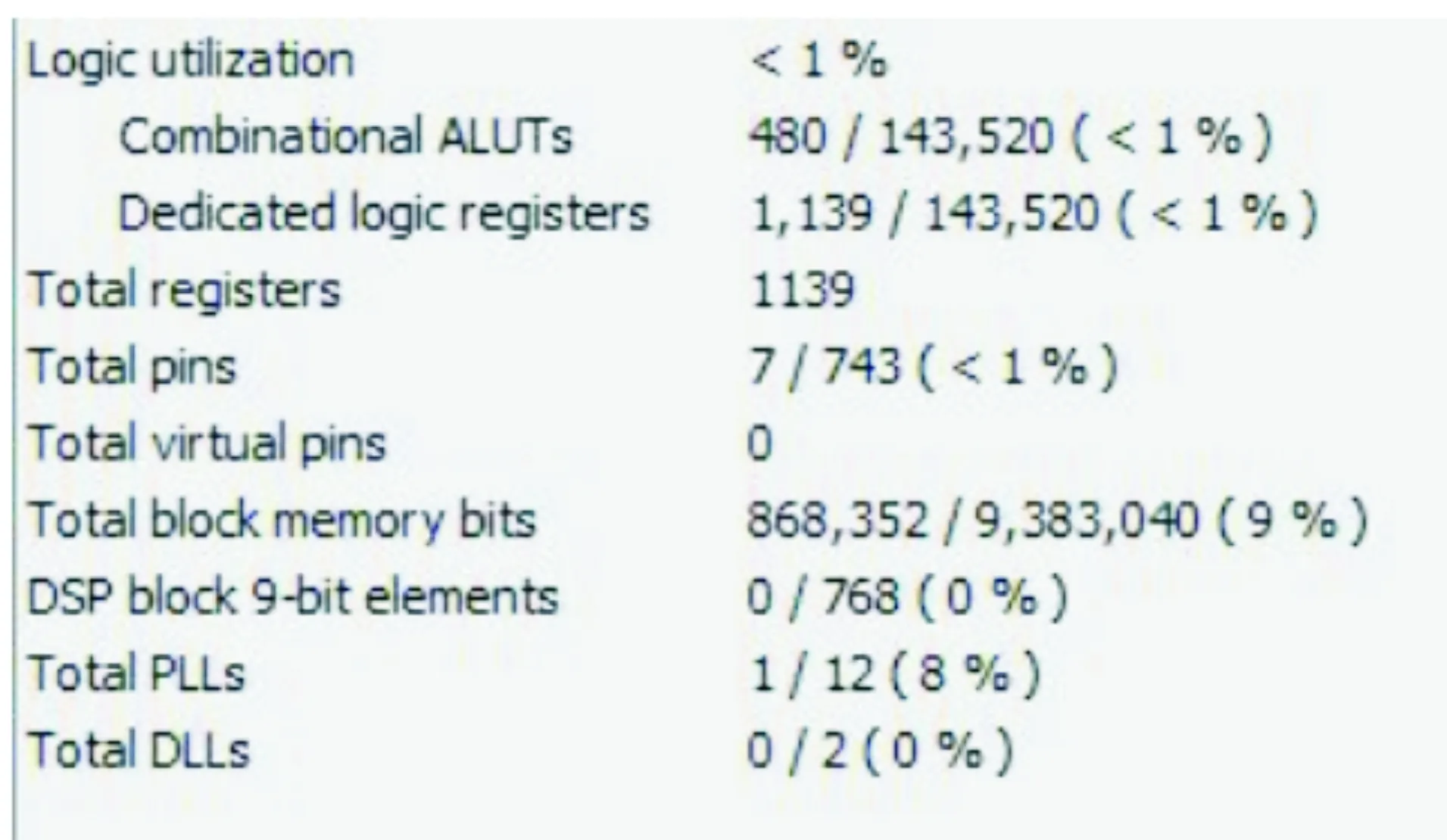

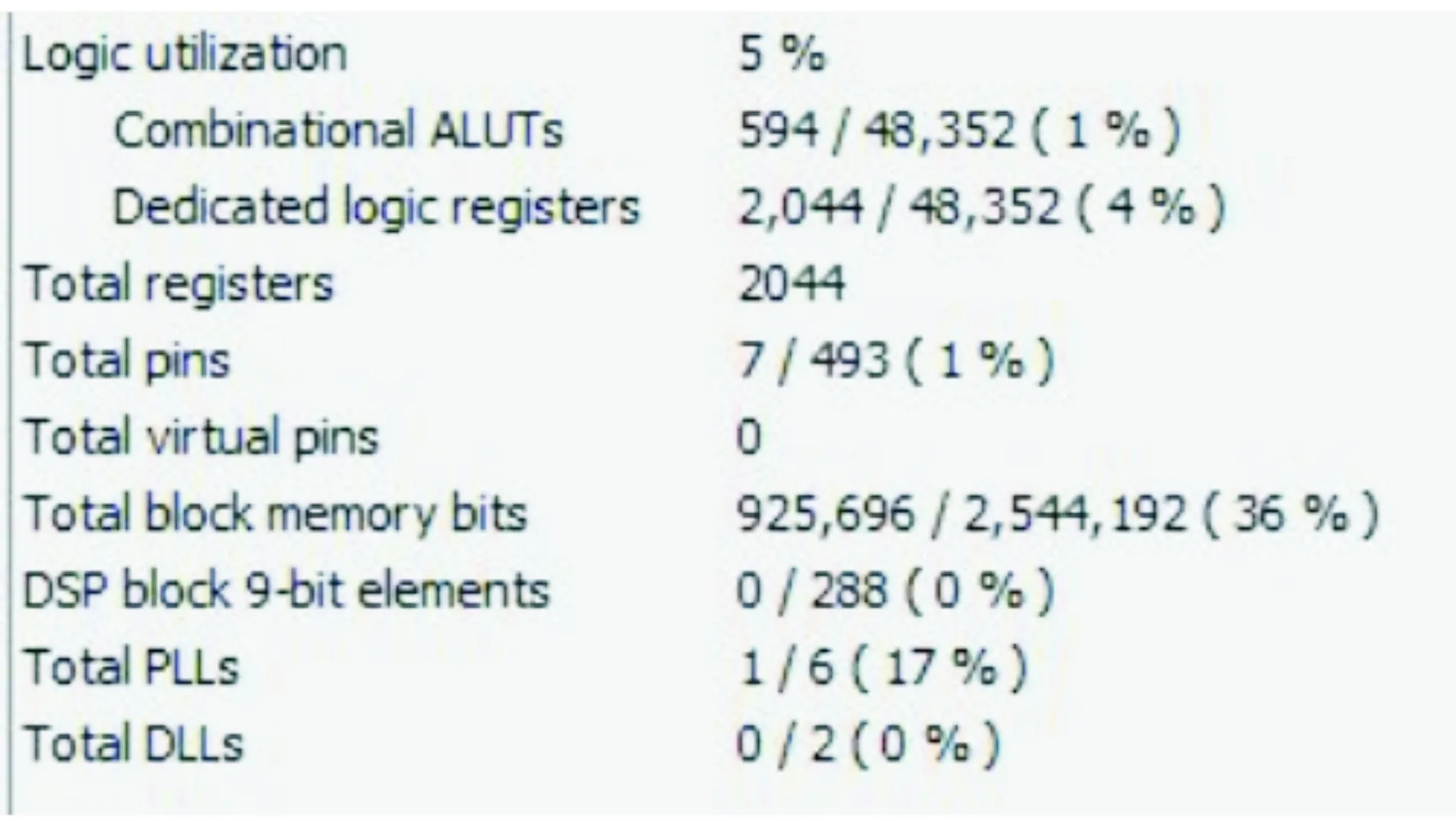

本工程采用Altera公司的EP2C8T144I8芯片,工作时钟由本地晶振(10 MHz)通过片内的PLL倍频、再经DDS模块分频产生,为SDH E1规定的2.048 MHz,对于帧格式生成部分,具体使用的逻辑资源以及片内资源使用情况如图6所示。

图6 帧格式生成所占用片内资源情况

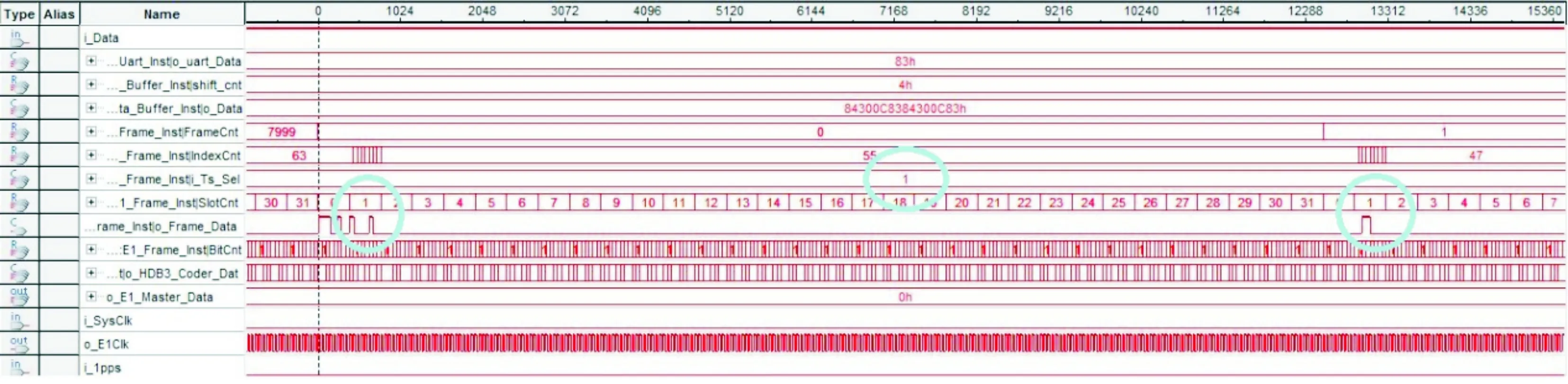

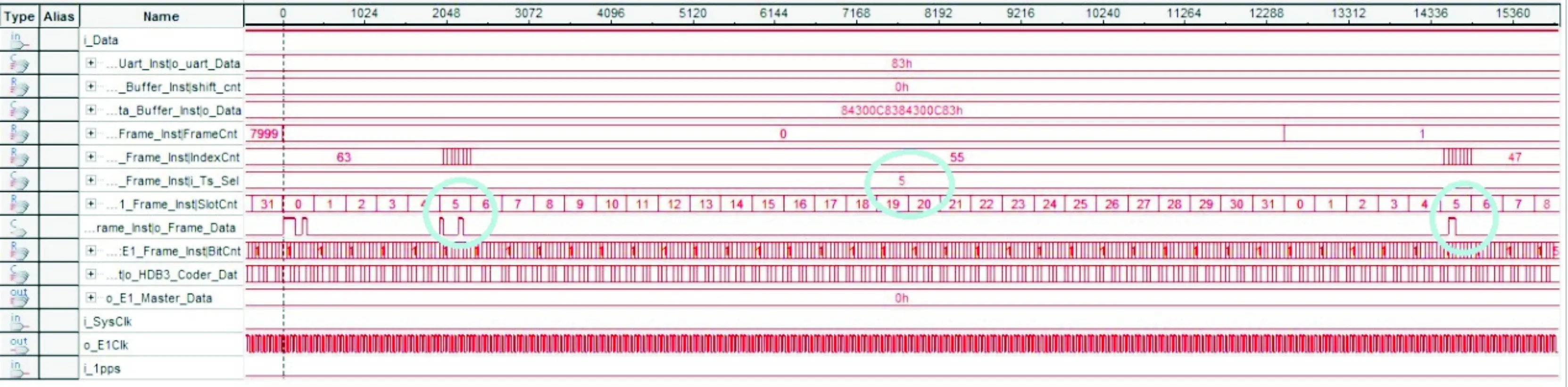

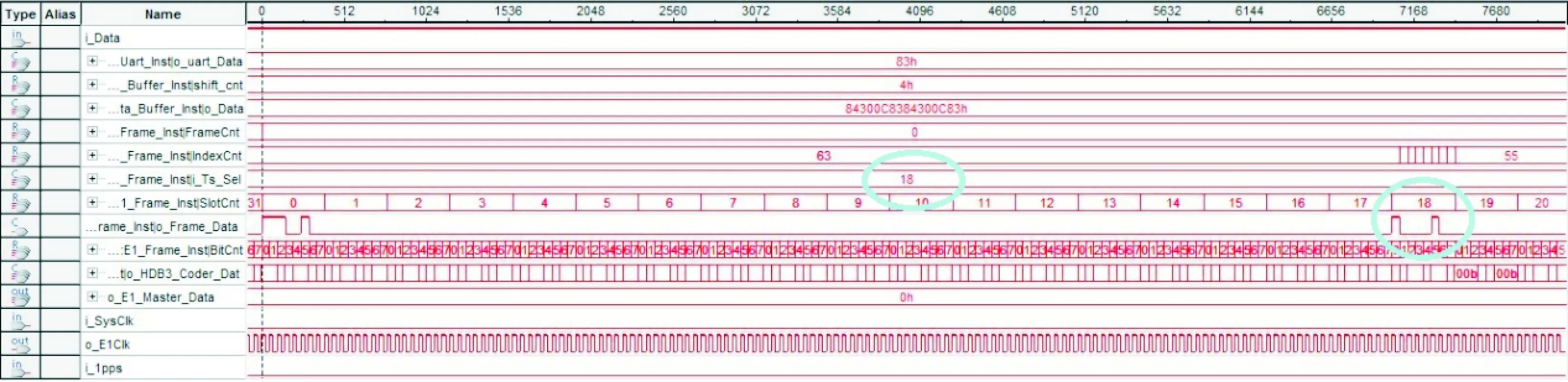

为了增强时隙利用的灵活性,本设计给用户提供了一个接口信号(时隙选择信号)i_Ts_Sel,让用户根据自身需求以及时隙的利用情况去灵活分配1~31中任一时隙为所用。使用中,只需给i_Ts_Sel赋上1~31中任一值,系统就会按照要求将所要传输的数据填充到指定时隙。当用户通过指令配置生效后,系统能够很好将巴克码作为帧头填充到第0时隙,将输入数据填充到用户指令配置的时隙,以达到灵活配置的目的。o_Data为输入信号,SlotCnt信号为时隙计数器,用来直观辨别时隙的占用情况,o_Frame_Data为最终的E1时隙填充信号,展示完整的32个时隙。下面通过选择第1时隙、第5时隙和第18时隙为例,利用FPGA的开发环境Quartus II软件自带的逻辑分析仪Signal Tap II进行仿真验证。

图7和图8为E1可配时隙帧格式。由图7可以看到,当给时隙选择信号i_Ts_Sel赋值为1,即选择第1时隙时,根据时隙计数器SlotCnt可以清晰看到,输出信号o_Frame_Data第1时隙的位置填充了相应的数据。

图7 E1可配时隙帧格式(填充时隙1)

由图8可以看到,当给时隙选择信号i_Ts_Sel赋值为5,即选择第5时隙时,输出信号o_Frame_Data第5时隙的位置填充了相应的数据。

图8 E1可配时隙帧格式(填充时隙5)

同理,当给时隙选择信号i_Ts_Sel赋值为18,即选择第18时隙时,输出信号o_Frame_Data第18时隙的位置填充了相应的数据,如图9所示。

图9 E1可配时隙帧格式(填充时隙18)

4 HDB3编码实现

由总体框图的设计流程可知,数据经过E1帧格式的生成以后,需要对数据进行编码,本系统采用的是HDB3的编码方式。

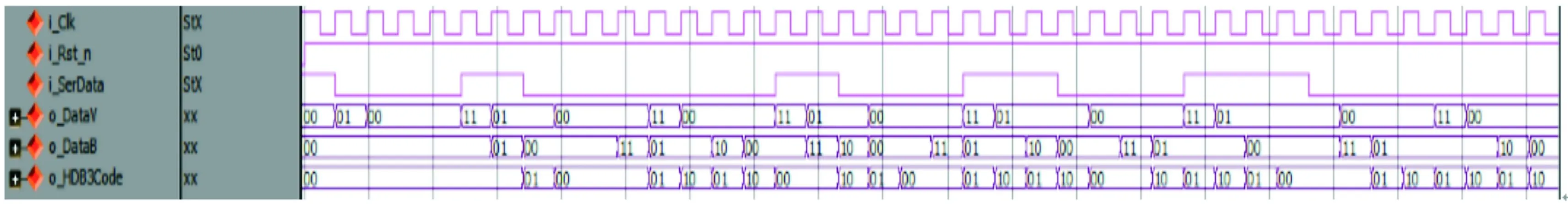

由于数字电路中只有“0”和“1”,无法传输“V”,“B”等字符,因此对编码过程中出现的“V”,“B”,“+1”,“-1”进行事先标识,以便后期的处理与识别。HDB3编码模块主要实现的是对二元码进行加“V”、加“B”和极性变化操作。本文将编码模块分成3步进行,在加“V”和加“B”两步中,以“00”表示“0”,“10”表示“B”,“11”表示“V”,在极性变换中,以“10”表示“+1”,“01”表示“-1”,“00”表示“0”。以“100001100000000 110000111 0000111100000000111000100000100000011”为测试数据进行测试,数据中包含多种长连“0”出现的情况,具有普适性。

对于HDB3编码部分,具体使用的逻辑资源以及片内资源使用情况如图10所示。

图10 HDB3编码所占用片内资源情况

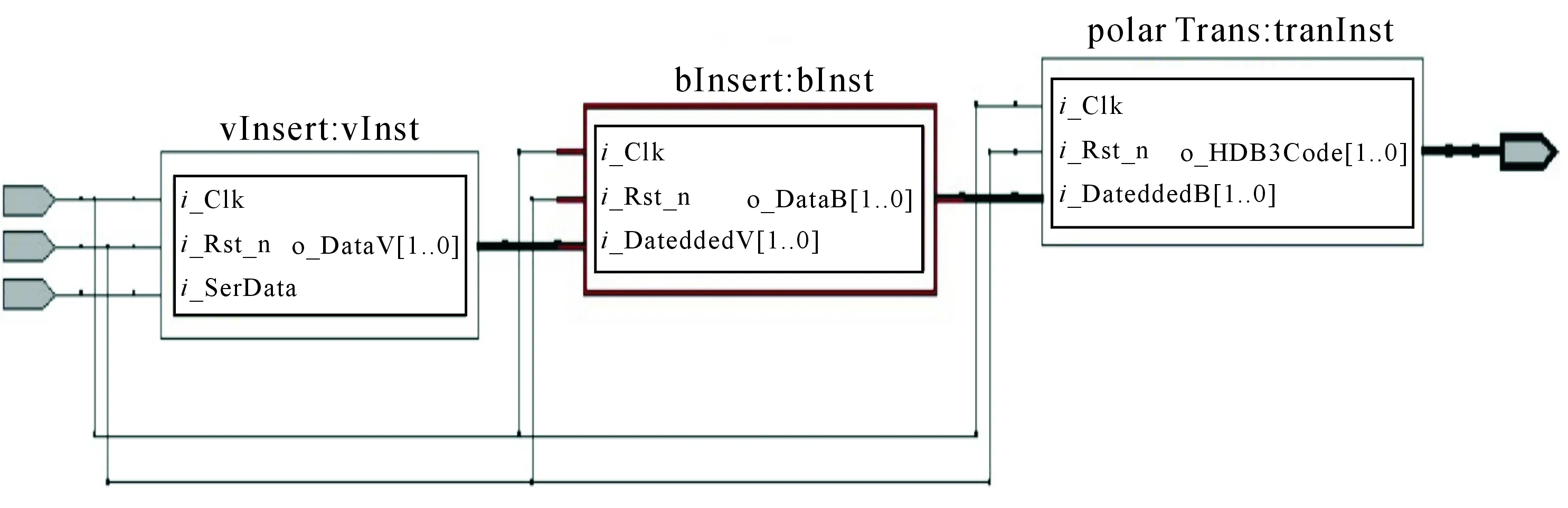

编码的RTL流程图如图11所示,主要包含3个部分,其中,vInst为加“V”模块,bInst为加“B”模块,tranInst为极性变换模块。

图11 HDB3编码RTL视图

具体的仿真见图12,此图为Modelsim的后仿真截图,由于时序裕量充足,未做时序约束。i_SerData为输入信号,o_DataV,o_DataB和o_HDB3 Code分别为加“V”,加“B”,极性变换后的信号。根据编码规则以及前面约定的标识,输入的二元码经过HDB3转换后应该为“01 00 00 00 01 10 01 10 00 00 10 01 00 00 01 10 01 10 00 00 10 01 10 01 00 00 00 01 10 01 10 01 10…”,图12仿真结果与之前理论推导结果一致,表明该编码方式实现正确。

图12 HDB3编码仿真图

5 测试结果分析

通过各模块的仿真验证无误后,对整个E1时间同步设备进行测试,将主端设备连接上GNSS定时模块输出的1 PPS信号,同时连接上UTC(NTSC)输出的10 MHz参考频率,经过主端设备的处理后,生成满足E1帧格式协议的信号[19-21]。该信号通过E1线路进行传输,当从端收到该信号后,对该信号进行解帧和解码操作,进而复现出1 PPS信号。最后,将最开始主端源头处的1 PPS和从端复现出来的1 PPS同时连接到SR620时间间隔计数器上进行测试(SR620时间间隔计数器的外参考频标是UTC(NTSC)输出的10 MHZ信号),从而测试出两者的时间间隔数据。

图13 测试流程图

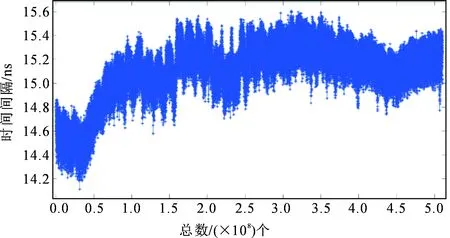

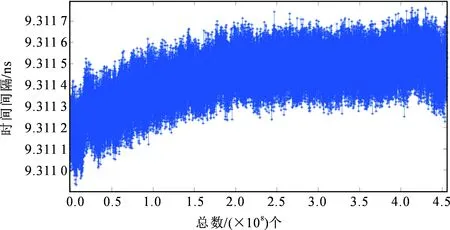

本次试验测试,通过分时段采集了两次数据。第1次的测试数据是从北京时间2018-01-19 20:37:57到2018-01-20 10:49:09,共采集了51 070个数据点;第2次的测试时间从北京时间2018-01-20 18:25:08到2018-01-21 11:16:41,共采集了60 694个数据点。

图14是第1段测试采集到原始数据的绘图,经过对数据的分析,计算得出均值为15.11 ns,标准差是0.24 ns。

图14 测试结果图1

图15是第2段测试采集到原始数据的绘图,同理,经过对数据的分析,计算得出均值为34.094 6 ns,方差为0.120 6 ns。

图15 测试结果图2

通过在两个不同的时间段对设备进行开关机试验,得出以上两个测试结果。鉴于E1的数据速率为2.048 Mbit/s,所以从端在检测接收到的数据的时候,会存在(1/2.048)s的不确定度,大约为488 ns。因此在每次开关机的过程中(即每次上电的时候),会存在488 ns的不确定度。以上两次的数据结果在该范围内,说明设备功能健全。

6 结语

基于帧格式生成和HDB3编码原理,设计时隙可配的SDH E1帧格式及数据编码方案,并在FPGA上进行实现,通过实验仿真验证其功能。基于本文设计结果,SDH光纤网络用户在保证其语音、图像等数据传输核心业务的同时,可根据信道特性和自身需求,通过软件对E1帧格式中的时隙进行配置,使得时码信息可占用E1帧格式31个时隙中的任意一个时隙,经过HDB3编码实现时间同步信息在SDH光纤网络中的传输,提高SDH光纤网络时间同步信息传输的灵活性,为SDH光纤网络通信性能的提升提供支撑,SDH光纤网络E1通道时间同步具有重要的工程实用价值。