栅极低电压对关断瞬态的影响

李乐乐 李建成 王洪利 孙铭泽

栅极低电压对关断瞬态的影响

李乐乐1李建成2王洪利1孙铭泽1

(1. 湘潭大学物理与光电工程学院,湖南 湘潭 411100;2. 国防科技大学电子科学与工程学院,长沙 410073)

随着开关频率的提高,寄生电感对碳化硅(SiC)MOSFET的影响越来越明显,所引起的器件串扰和器件应力,严重制约了SiC MOSFET器件在高频下的应用。在实际设计驱动电路中,为了抑制器件的串扰,栅极低电压多选在-5~0V之间的数值,然而却忽略了栅极低电压对器件应力的影响。在此本文通过理论和仿真分析,研究了寄生电感存在时,不同栅极低电压下的过冲电压和关断瞬间的功耗,从而在设计SiC MOSFET驱动电路时,指导栅极低电压的选取。

SiC MOSFET;栅极低电压;过冲电压;功耗

本文就是在此基础上,考虑寄生参数存在时,建立合理的理论模型,从理论和仿真结果来分析高频下不同栅极低电压对SiC MOSFET过冲电压的影响,通过结果来指导驱动电路设计时对栅极低电压的选择。

1 SiC MOSFET关断过程理论分析

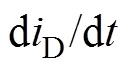

考虑寄生电感的SiC MOSFET双脉冲测试电路原理图如图1所示。Q为SiC MOSFET开关管,栅源极、栅漏极和漏源极之间的寄生电感分别为GS、GD和DS,D为漏极寄生电感,它包括MSOFET器件引脚分布的电感、二极管寄生电感、PCB走线寄生电感等;S为源极寄生电感,它包括MOSFET器件引脚寄生电感、PCB走线寄生电感等;ext为驱动电路引入的电阻,int为器件内阻;L为负载电感,与之相并联的为续流二极管。对于栅极寄生电感,在实际的分析中是被忽略的,一方面因为在电路设计时,驱动电路紧靠MOSFET,寄生很小;另一方面栅极寄生电感的存在不便于推导建立数学模型分析,因此忽略栅极寄生电感G。G为栅极驱动电压,DC为母线电压。

图1 带寄生参数的双脉冲测试电路原理图

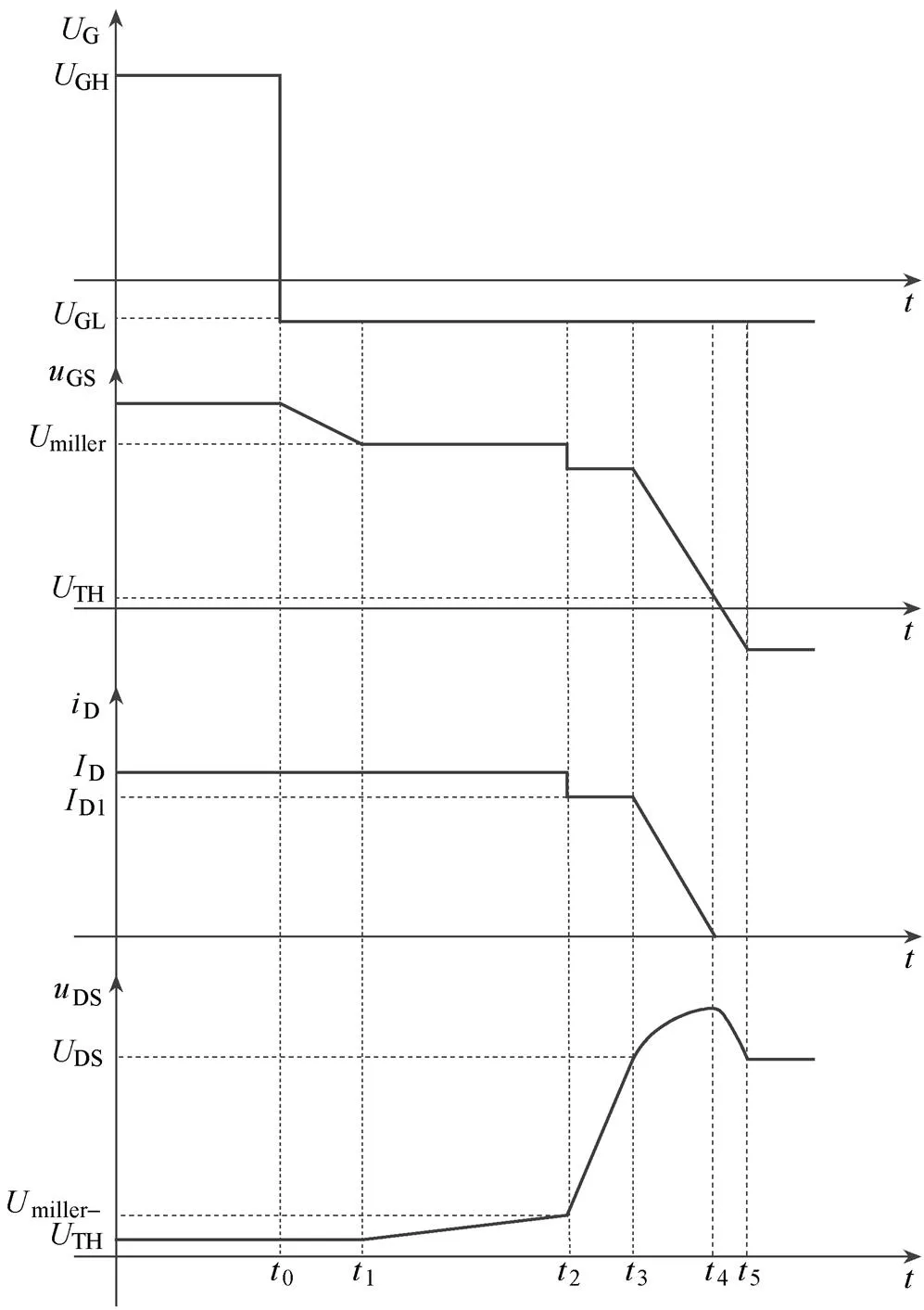

1.1 关断延时阶段(t0~t1)

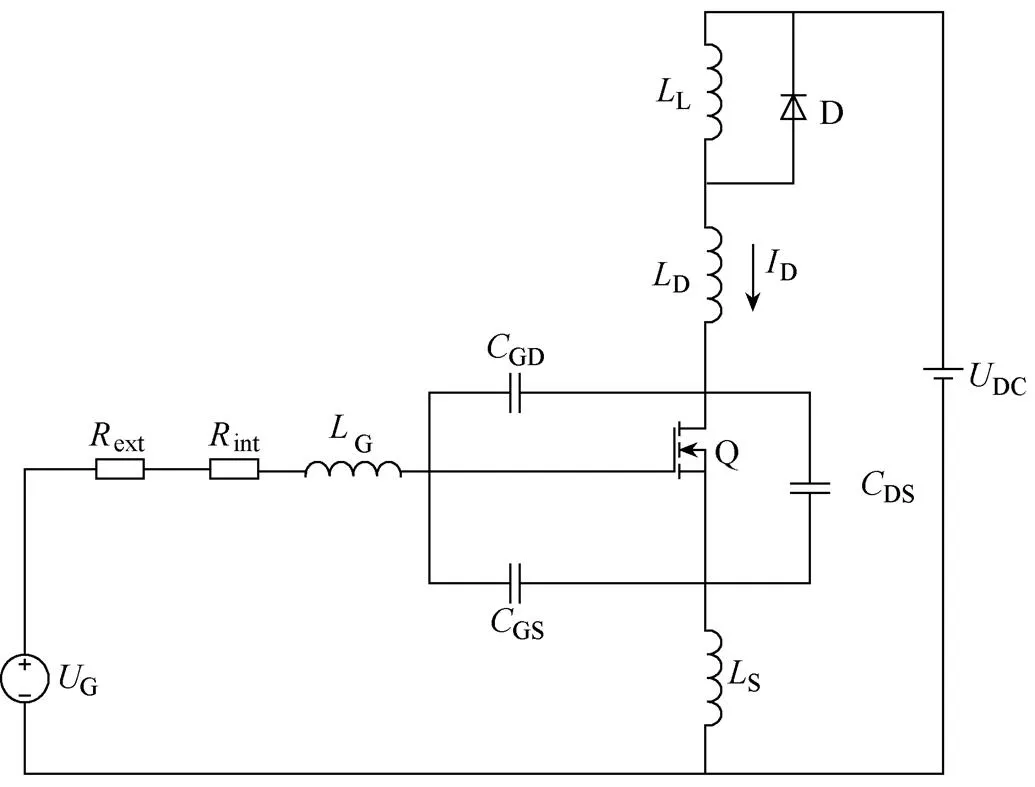

图2 SiC MOSFET关断过程波形示意图

1.2 电压上升阶段Ⅰ(t1~t2)

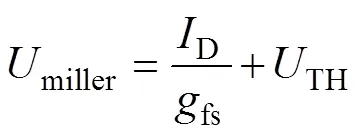

由式(2)可得,1时刻米勒电压可表示为

1.3 电压上升阶段Ⅱ(t2~t3)

因此,由于输出电容的分流,使得该阶段的米勒平台电压相比于上一个阶段有所降低。

1.4 电流降落和过充电压产生阶段(t3~t4)

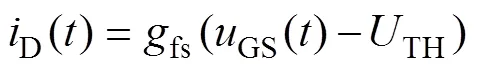

从上一阶段开始器件进入饱和区工作,漏极电流满足:

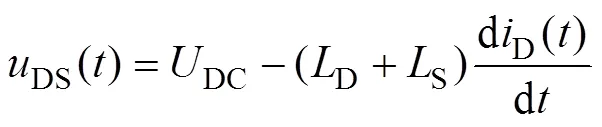

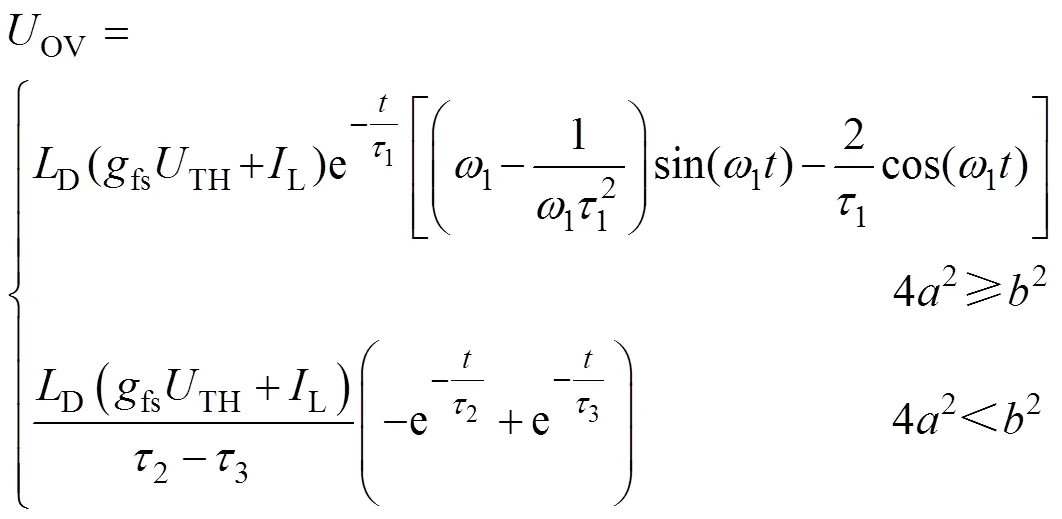

漏电流作用于主功率回路的寄生电感L和D上,产生感应电压,此时SiC MOSFET开关器件两端承受的电压表示为

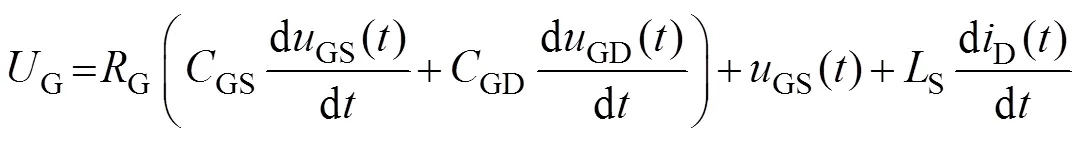

对应的栅极电压回路满足方程:

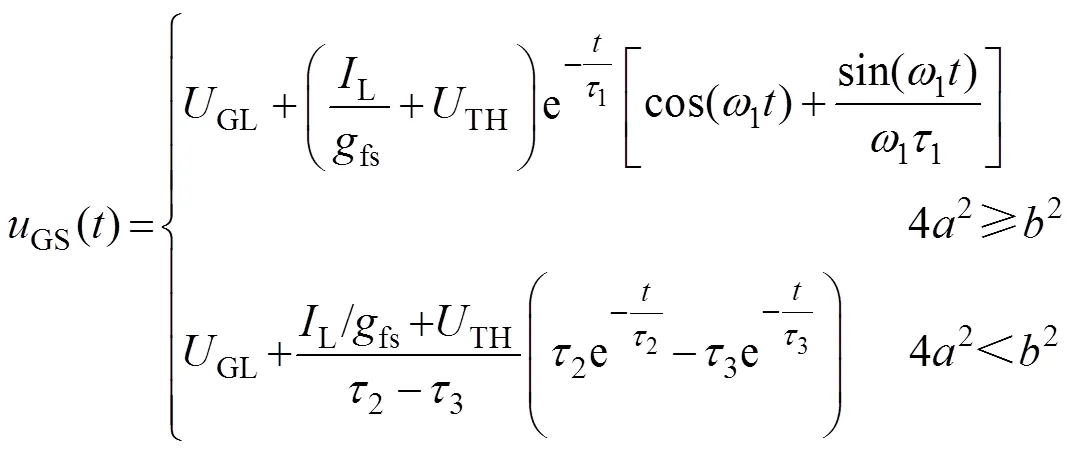

联立式(5)、式(6)和式(7)可得出关断后的栅源电压表达式:

对于42与2关系,影响因素主要是漏极寄生电感D、饱和区跨导fs和栅漏电容GD。其中饱和区跨导fs又是变量,因此分析起来较为复杂,难以得出一个广泛适用的结论,而在再具体条件下,却可以说明问题。

1.5 SiC MOSFET关断过程(t4~t5)

2 仿真结果

为了更好地理解不同的栅极低电压对SiC MOSFET器件过冲电压的影响,在此进行仿真测试,仿真器件选择的是CREE公司的C2M0040120D,使用该公司提供的PSpice模型进行仿真,续流二极管采用C4D20120A肖特基二极管,开关频率选取100kHz,栅极电阻5W,负载电感选取480mH,漏极寄生电感选取70nH/300nH。栅极低电压变化范围-5~0V,栅极高电压选择20V,直流电压选取800V,搭建双脉冲仿真测试电路。

2.1 栅极低电压对栅源电压的影响

图3 不同栅极低电压下栅极电压的仿真曲线

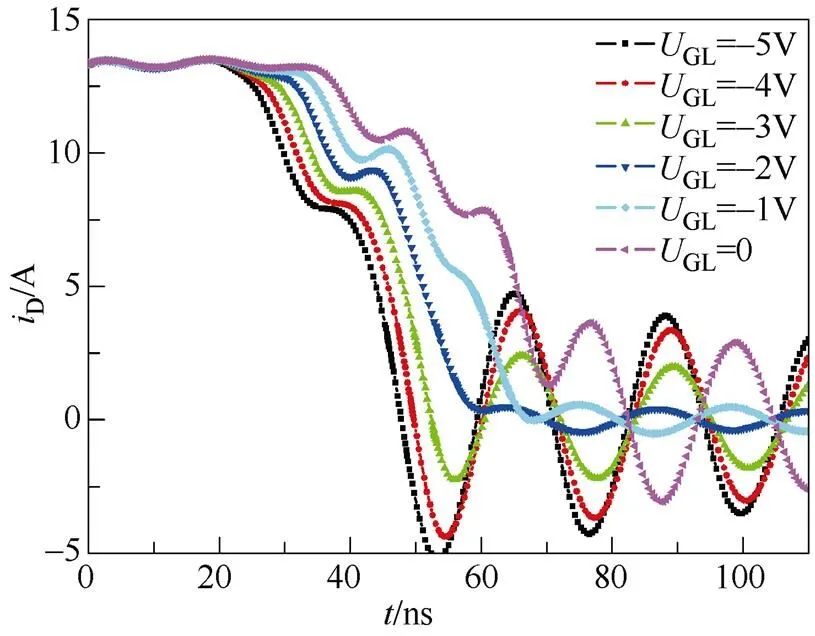

2.2 栅极低电压对漏电流的影响

从图4可以看出,受栅源电压影响,漏电流在不同栅极低电压下,下降速度明显不同,栅极低电压越低,漏电流下降速度越快。

图4 不同栅极低电压下漏电流的仿真曲线

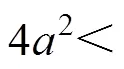

2.3 栅极低电压对漏源电压的影响

图5 不同栅极低电压下漏源电压的仿真曲线

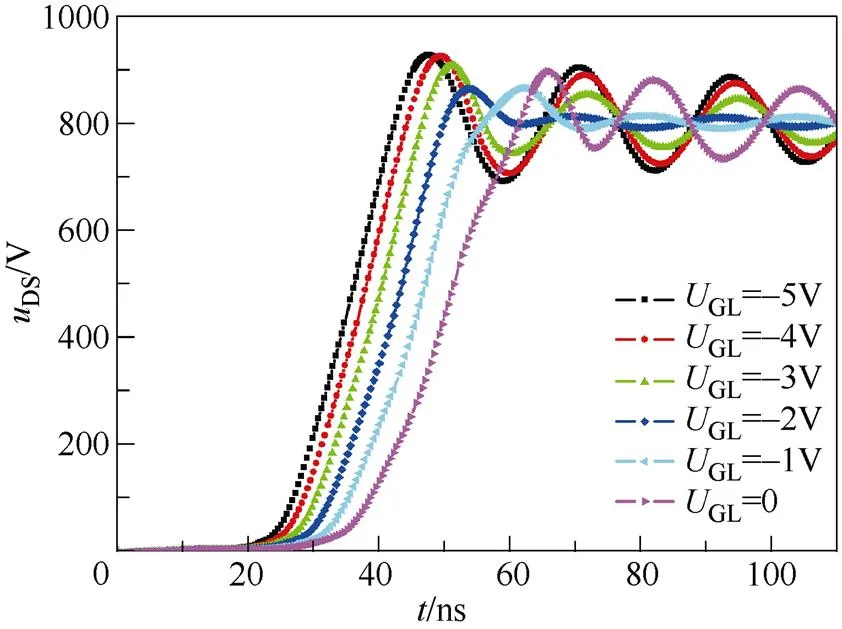

图6 漏极寄生电感为300nH时漏源电压仿真曲线

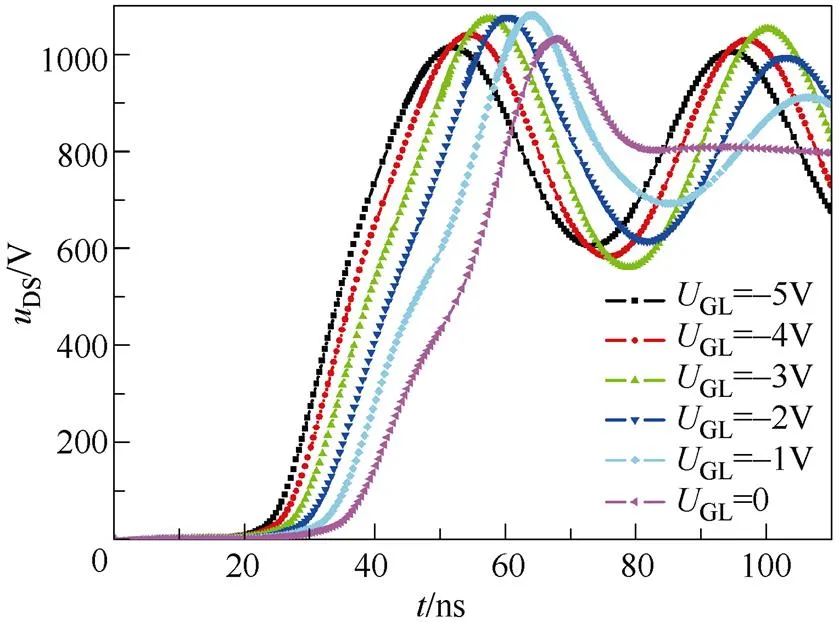

从图中的仿真结果可以看出,栅极低电压越小,SiC MOSFET漏源电压上升的速度越快,而且起步也越早。过冲电压的变化有一个明显的转折,对应的折线图如图7所示。

图7 不同栅极低电压下的过冲电压

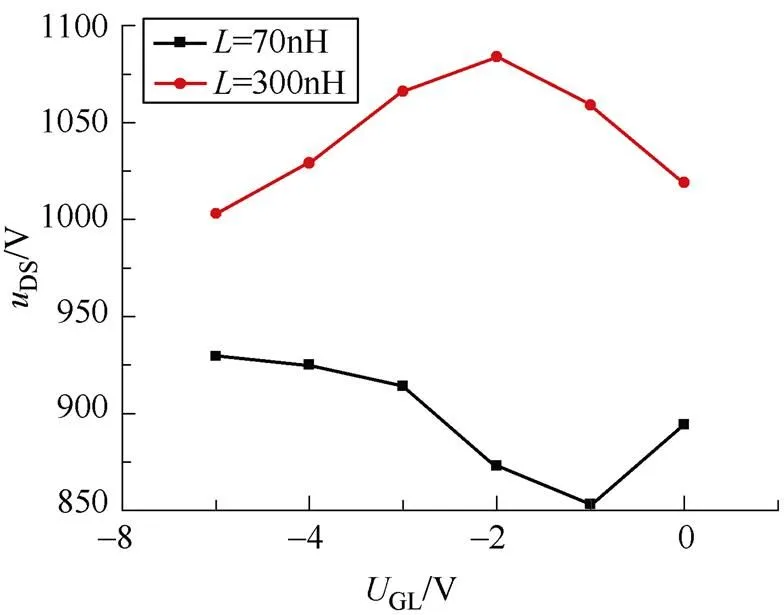

2.4 栅极低电压对功耗的影响

从以上的分析可以得出,栅极低电压对SiC MOSFET器件的关断瞬间速度和过冲电压大小有影响,因此在此对关断瞬间的功耗进行了仿真,仿真结果如图8所示。

图8 不同栅极低电压下的关断瞬间功耗曲线

3 结论

为了更好地了解栅极低电压对过充电压的影响,本文进行了一些理论和仿真方面的研究,说明了栅极低电压在高频下对SiC MOSFET对过冲电压、功耗等方面的影响,具有以下几点实用性价值:

1)对于一个确定的SiC MOSFET器件和电路,在驱动电路设计中选择栅极低电压时,具有一定的参考价值。

2)栅极低电压越低,SiC MOSFET器件的开关速度越快,功耗越小,但器件的过充电压却不一定最大。

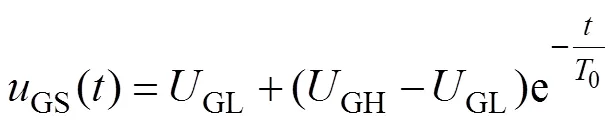

[1] 李典林, 胡欣. d/d引发的MOSFET误导通分析[J]. 通信电源技术, 2006, 23(6): 39-42.

[2] Zhang Z, Guo B, Wang F, et al. Impact of ringing on switching losses of wide band-gap devices in a phase-leg configuration[C]//Applied Power Electronics Conference and Exposition, 2014: 2542-2549.

[3] Zhang Z, Zhang W, Wang F, et al. Analysis of the switching speed limitation of wide band-gap devices in a phase-leg configuration[C]//Energy Conversion Congress and Exposition. IEEE, 2012: 3950-3955.

[4] Xu S, Sun W, Sun D. Analysis and design optimization of brushless DC motor's driving circuit considering thed/dinduced effect[C]//Energy Conversion Congress and Exposition. IEEE, 2010: 2091-2095.

[5] Lemmon A, Mazzola M, Gafford J, et al. Stability considerations for Silicon carbide Field-Effect transistors[J]. IEEE Transactions on Power Electronics, 2013, 28(10): 4453-4459.

[6] Stewart C, Escobar-Mejía A, Balda J C. Guidelines for developing power stage layouts using normally-off SiC JFETs based on parasitic analysis[C]//IEEE Energy Conversion Congress and Exposition. IEEE, 2013: 948-955.

[7] Liu Qian, Wang Shuo, Baisden A C, et al. EMI suppression in voltage source converters by utilizing dc-link decoupling capacitors[J]. IEEE Transactions on Power Electronics, 2007, 22(4): 1417-1428.

[8] Zhao Q, Stojcic G. Characterization of Cdv/dt induced power loss in synchronous buck DC-DC con- verters[C]//Applied Power Electronics Conference and Exposition, 1, 2004: 292-297.

[9] 赵斌. SiC功率器件特性及其在Buck变换器中的应用研究[D]. 南京: 南京航空航天大学, 2014.

[10] 秦海鸿, 朱梓悦, 戴卫力, 等. 寄生电感对SiC MOSFET开关特性的影响[J]. 南京航空航天大学学报, 2017, 49(4): 531-539.

[11] 秦海鸿, 张英, 朱梓悦, 等. 寄生电容对SiC MOSFET开关特性的影响[J]. 中国科技论文, 2017(23): 2708-2714.

[12] 范春丽, 余成龙, 龙觉敏, 等. 寄生参数对SiC MOSFET开关特性的影响[J]. 上海电机学院学报, 2015, 18(4): 191-200.

[13] Wang Jianjing, Chung H S, Li R T. Characterization and experimental assessment of the effects of parasitic elements on the MOSFET switching performance[J]. IEEE Transactions on Power Electronics, 2013, 28(1): 573-590.

[14] 沈瑾. 节能变频器叠层母线的设计[J]. 电机与控制应用, 2013, 40(5): 53-58.

[15] Yamashita Y, Furuta J, Inamori S, et al. Design of RCD snubber considering wiring inductance for MHz- switching of SiC-MOSFET[C]//Workshop on Control and Modeling for Power Electronics, 2017: 1-6.

[16] 王孝伟, 李铁才, 石坚, 等. 三段式门极驱动抑制MOSFET关断过冲振荡的研究[J]. 电机与控制学报, 2013, 17(7): 1-6.

[17] 王旭东, 朱义诚, 赵争鸣, 等. 驱动回路参数对碳化硅MOSFET开关瞬态过程的影响[J]. 电工技术学报, 2017, 32(13): 23-30.

[18] 梁美, 郑琼林, 李艳, 等. 用于精确预测SiC MOSFET开关特性的分析模型[J]. 电工技术学报, 2017, 32(1): 148-158.

[19] 朱义诚, 赵争鸣, 王旭东, 等. SiC MOSFET与SiC SBD换流单元瞬态模型[J]. 电工技术学报, 2017, 32(12): 58-69.

[20] 梁美, 李艳, 郑琼林, 等. 高速SiC MOSFET开关特性的测试方法[J]. 电工技术学报, 2017, 32(14): 87-95.

The effect of gate low voltage on the turn-off transients

Li Lele1Li Jiancheng2Wang Hongli1Sun Mingze1

(1. College of Physics and Optoelectronic Engineering, Xiangtan University, Xiangtan, Hu’nan 411100; 2. School of Electronic Science and Engineering, National University of Defense Technology, Changsha 410073)

With the increase of switching frequency, the effect of parasitic inductance on silicon carbide (SiC) MOSFETs becomes more and more obvious, and crosstalk and device stress caused by the devices seriously restrict the application of SiC MOSFET devices under high frequency. In the actual design of the driver circuit, in order to suppress the crosstalk of the device, the gate low voltage is generally selected between-5~0V. However, the influence of low gate voltage on device stress is ignored. In this paper, through theoretical and simulation analysis, the overshoot voltage and power loss at turn-off transients at different gate voltages are studied in the presence of the parasitic inductance. Thus, in the design of the SiC MOSFET driver circuit, the selection of the gate low voltage is instructed.

SiC MOSFET; low gate voltage; overshoot; power loss

2018-11-15

李乐乐(1990-),男,湘潭大学物理与光电工程学院在读硕士研究生,主要从事碳化硅大功率器件应用研究。