CAN总线控制器IP设计

汪晓翔,马 琪

(杭州电子科技大学 微电子CAD研究所,浙江 杭州 310018)

随着应用需求的提高,一些设备在进行实时数据通信时需要保证数据传输的稳定可靠性。CAN(Controller Area Network)总线被广泛应用于工业控制、汽车电子等设备之间的通信。随着嵌入式设备的广泛应用,越来越多的设备之间需要使用CAN总线进行通信。为了减少片上系统(System on Chip,SOC)芯片的面积和功耗,需要在SOC芯片上集成CAN总线控制器。

CAN总线可以在节点之间实现自由通信,每个节点可以在任意时间向总线上发送数据。节点采用标识符代替传统的地址编码,每个节点的标识符由11位或29位组成。发送节点向总线发送的数据帧包含标识符,接收节点可以根据标识符接收相应的数据帧。数据帧的数据位最高有8位,可以满足工业控制的应用需求。针对工业应用的需求,本文提出了一种实时高速率的CAN总线控制器IP设计方法。

1 CAN协议和特点

CAN总线控制器需要完成数据从物理层、传输层到对象层的传输[1-2]。其中,物理层是数据传输的重要媒介;传输层,即数据链路层是CAN总线的核心部分,负责把从物理层接收到的数据提供给对象层,以及把从对象层需要发送的数据转换成数据帧提供给物理层。CAN总线控制器需要完成CAN2.0协议的全部内容。

CAN2.0协议的报文帧类型分为:数据帧、远程帧、错误帧和过载帧[3-4]。数据帧从发送端传递数据到接收端,一个数据帧由7个不同域组成:帧起始域、仲裁域、控制域、数据域、CRC域、应答域和帧结尾域;远程帧作为数据接收端的站通过其资源节点对不同的数据传送进行初始化设置;错误帧由两个不同的域组成,第一个域是不同站提供的错误标志的叠加,第二个域是错误界定符[5-6]。

CAN总线信息以不同格式的固定报文发送,报文长度可以自由配置。当总线空闲时,任何连接的节点都可以开始发送新的报文。CAN节点可以灵活添加到CAN网络中,不需要改变其他信息。CAN节点报文具有优先级,当多个节点同时向总线发送信息时,优先级低的节点会主动退出,高优先级的节点不受影响,继续发送信息。CAN总线允许在报文滤波中将识别符设置为可屏蔽的内容,从而不接收这组报文。CAN总线具有严格的错误检测功能,包含位错误、填充错误、形式错误、应答错误和CRC校验[7-8]。

2 CAN总线控制器的整体结构

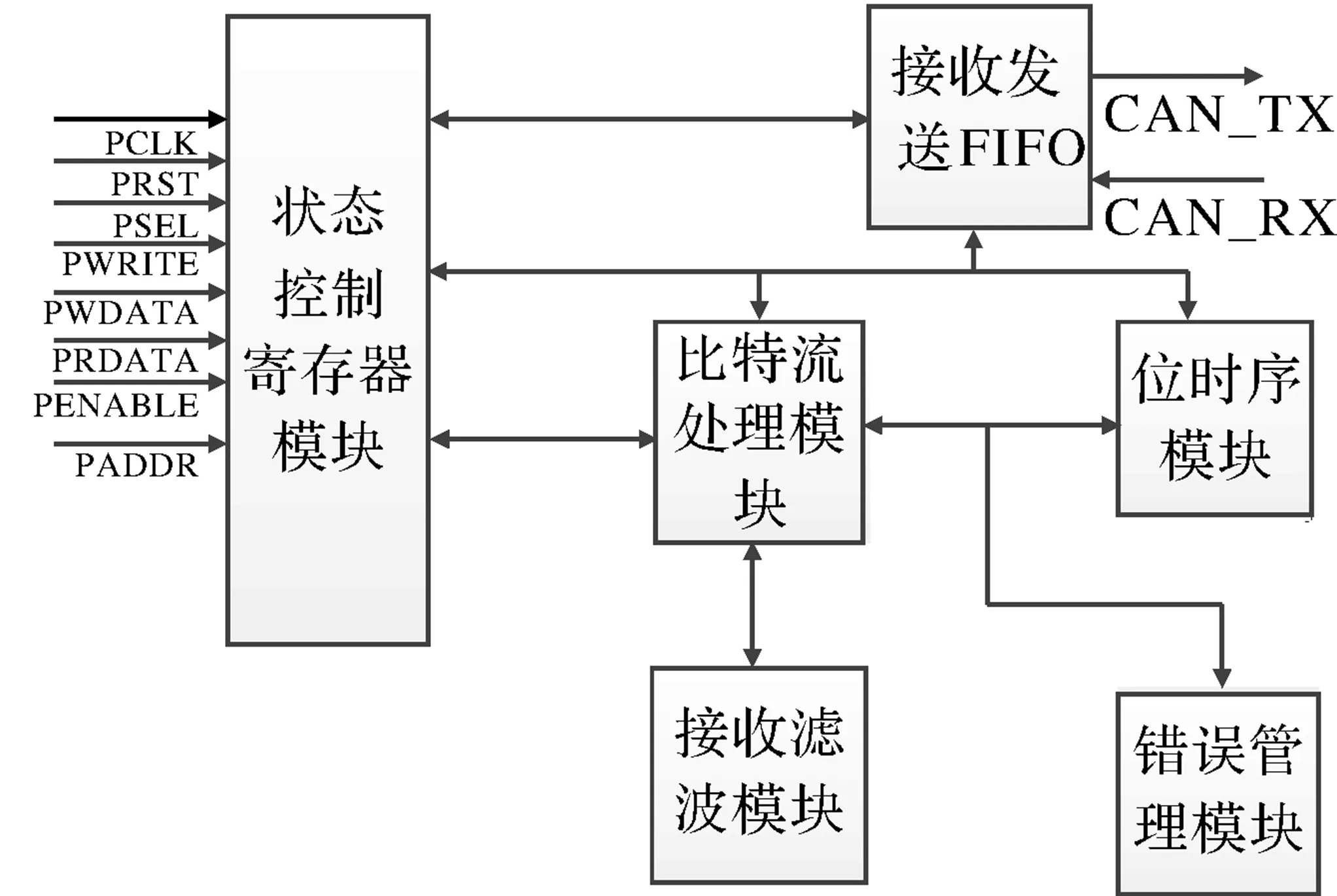

CAN总线控制器主要由状态控制寄存器模块、比特流处理模块、位时序模块、接收滤波模块、错误管理模块、接收发送FIFO模块组成。如图1所示,状态控制寄存器模块包含状态控制寄存器和数据寄存器;比特流处理模块主要完成发送和接收状态机的数据传输,完成数据流的处理;接收滤波模块屏蔽不想被接收的数据,实现数据选择;错误管理模块用于检测发送和接收的比特流是否会出现错误;接收和发送FIFO模块将需要发送和接收的数据缓存在FIFO中,使数据传输高效进行。

图1 CAN总线控制器的设计结构

3 CAN总线控制器的模块设计

3.1 状态控制寄存器模块

CAN总线控制器是一个低速模块单元,挂载在AMBA总线的APB总线上,其接口与APB总线接口相互连接。状态控制寄存器模块定义了CAN总线控制器的状态位、控制位、数据寄存器位和其他信号位。软件和硬件的交互通过查询、等待状态寄存器的状态位进行;发送和接收的数据通过访问数据寄存器进行。

3.2 比特流处理模块

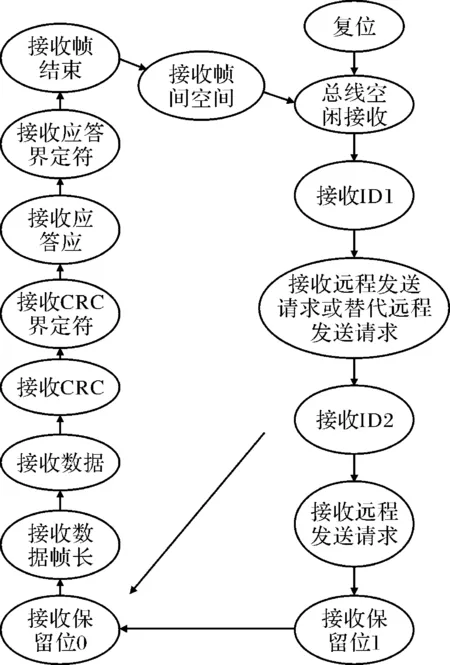

CAN总线控制器发送和接收数据(比特流)通过发送和接收状态机进行,如图2所示。

图2 比特流处理状态机

发送数据由发送状态机控制。每帧数据的标识符和优先权信息决定着每帧数据发送的先后顺序。CAN总线控制器的发送缓冲区使能后,发送状态机把缓冲区的数据,根据发送控制逻辑和移位控制逻辑,按照CAN2.0协议的数据帧格式,将发送数据转换成电平信号,最后由发送端发送出数据。

接收数据由接收状态机控制。接收起始位之后,进入接收起始状态,根据帧的标识符信息,判断是标准帧还是扩展帧。控制域信息控制接收数据的长度,把接收域的数据存储在数据寄存器中,将接收到的数据进行CRC校验,检查接收的数据是否正确。数据被正确接收后,发送接收应答信息,接收结束之后,发送结束标志,一个完整的数据帧被接收。

3.3 位时序逻辑模块

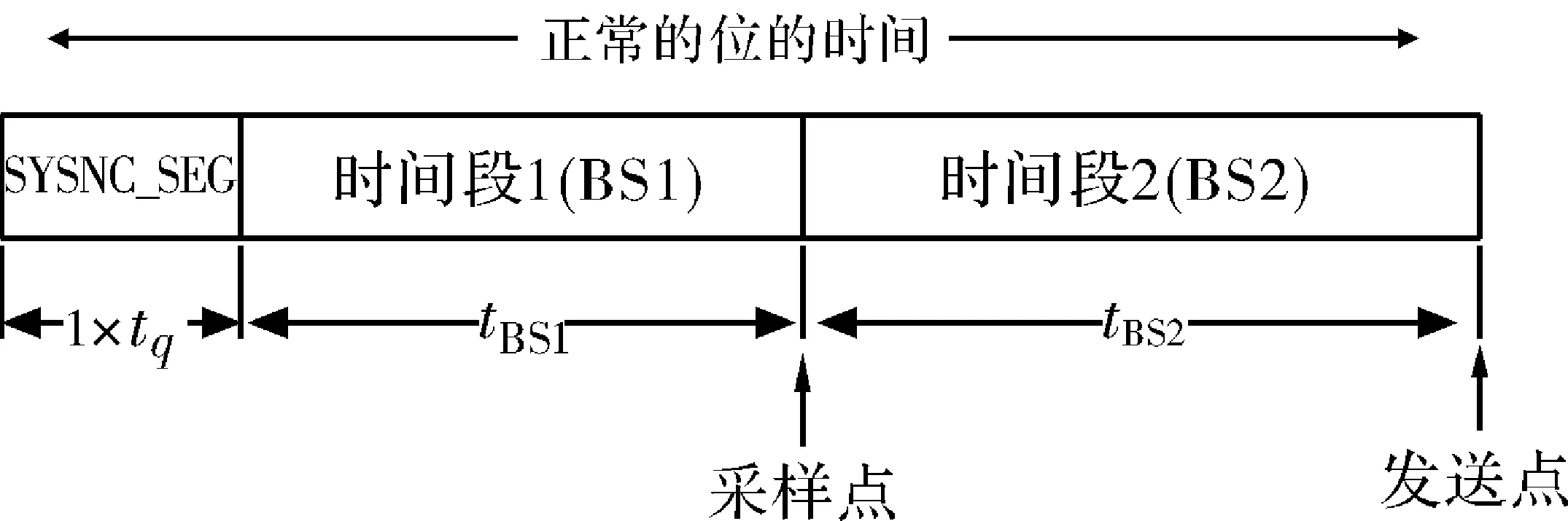

同步分为硬同步和重同步。硬同步方式是在起始信号沿时刻,将同步段平移至该信号沿的同步方式。硬同步方式只能作用于帧的起始信号时刻。重同步方式是通过比较总线时序与节点时序相位误差大小,调整节点相位缓冲段的大小,使得节点时序与总线时序同步[9-10]。

CAN协议把一个CAN数据的长度分解成SS段(同步段)、PTS段(传播时间段)、PBS1段(相位缓冲段1)、PBS2段(相位缓冲段2)。一个最小的时间单位Tq,它是系统时钟的整数倍。

图3 位时序

3.4 错误管理模块和接收发送FIFO

CAN总线控制器会检测5种错误类型:位错误、填充错误、CRC错误、形式错误和应答错误。位错误:发送单元在发送位的同时,也会对发送的位进行检测。如果检测到的位和发送的位不相同,则发送一个位错误。

填充错误:如果使用位填充法的编码信息中,检测到6个连续相同的电平,则发送填充错误。CRC错误:在数据接收端接收到的CRC校验码和发送的CRC校验码不相同时,检测到CRC错误,发送CRC错误标志[11-12]。

为了提高数据发送和接收速率,控制器在发送端和接收端均采用8位深度的FIFO设计。构造FIFO的深度为N(N=3),FIFO指针地址为N+1位。读指针和写指针采用二进制格雷码表示,当读指针的最高位和写指针的最高位相反,其余位相等的时候,此时FIFO为满,FIFO满标志置1;当读指针和写指针的N+1位全相等的时候,FIFO为空,FIFO为空标志置1。

3.5 接收滤波模块

报文滤波取决于整个识别符。允许在报文滤波中将任何的识别符位设置成屏蔽的内容,可以选择多组识别符,使之被映射到对应的接收缓冲器中。如果使用屏蔽寄存器,它的每一个位必须是可编程的,即它们能够被允许或禁止报文滤波。屏蔽寄存器的长度可以包含整个识别符,也可以仅包含部分的识别符[13-15]。

4 CAN总线控制器的FPGA原型验证

4.1 FPGA验证平台搭建

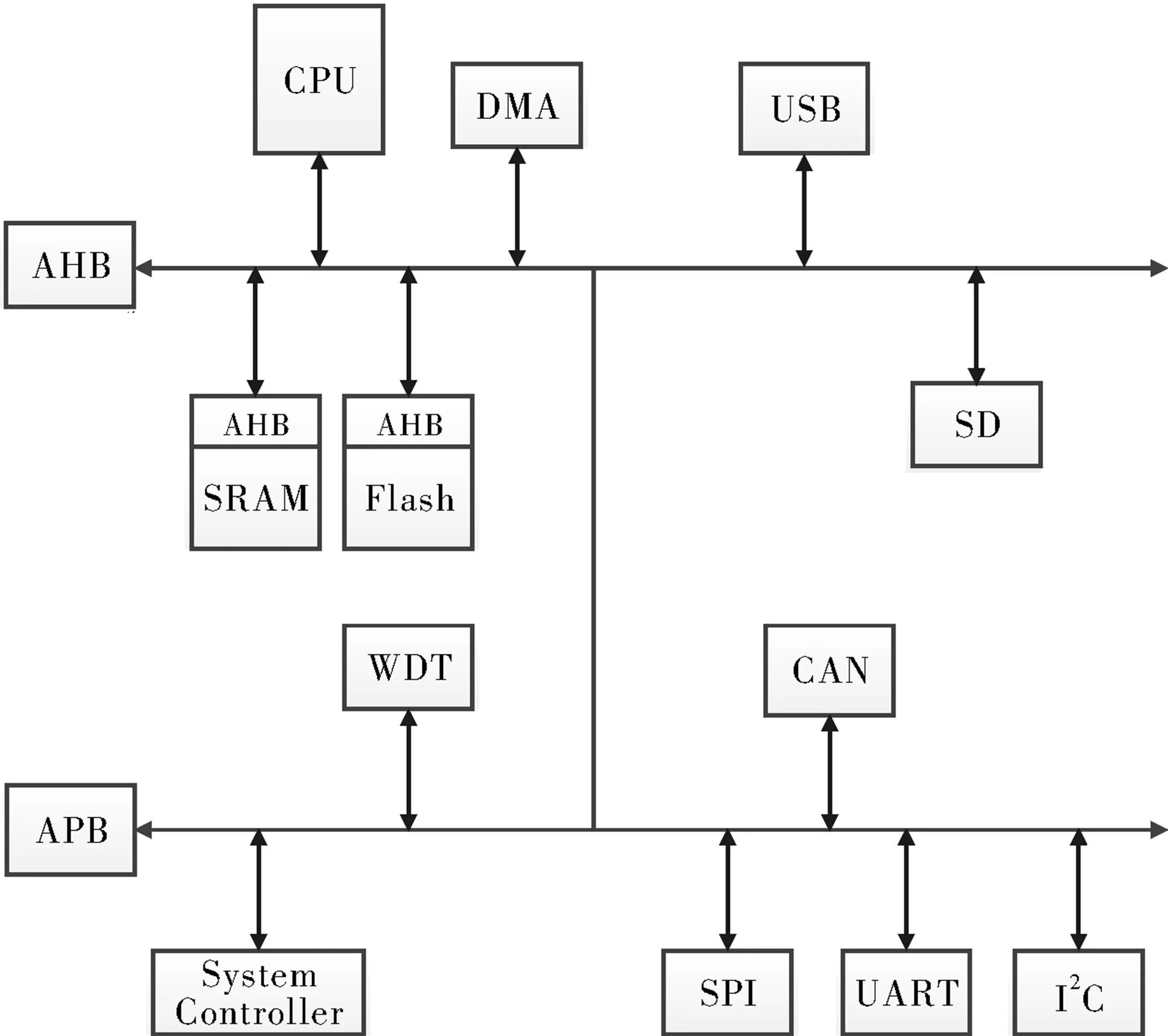

为验证CAN总线控制器,通过搭建集成CAN总线控制器的MCU的FPGA原型验证平台,采用CAN仿真器来验证CAN控制器的正确性。如图4所示, CAN总线控制器集成在Cotex-M0内核的MCU上,MCU包含CPU、DMA、SRAM、Flash、AMBA总线、通用串行接口、CAN总线等模块。 CPU是整个模块的核心部件,指令通过CPU发出,控制AMBA总线上的各个模块有序的工作。SRAM和Flash是MCU的存储模块,用以存储数据和程序。通用串行接口、CAN控制器作为MCU外设挂载到AMBA总线上。

图4 集成CAN总线控制器的MCU验证平台

将集成了CAN总线控制器、M0内核的MCU的RTL代码经过FPGA综合工具综合、约束、布局布线,生成bit文件,随后将bit文件下载到FPGA验证平台,CAN仿真器连接电脑和FPGA。CAN仿真器作为CAN总线上的一个节点,既可以接收控制器发送的数据,又可以向控制器发送数据。CAN仿真器的调试软件CANTest作为上位机,可以显示CAN仿真器发送和接收的数据,图形化接口可以方便调试。

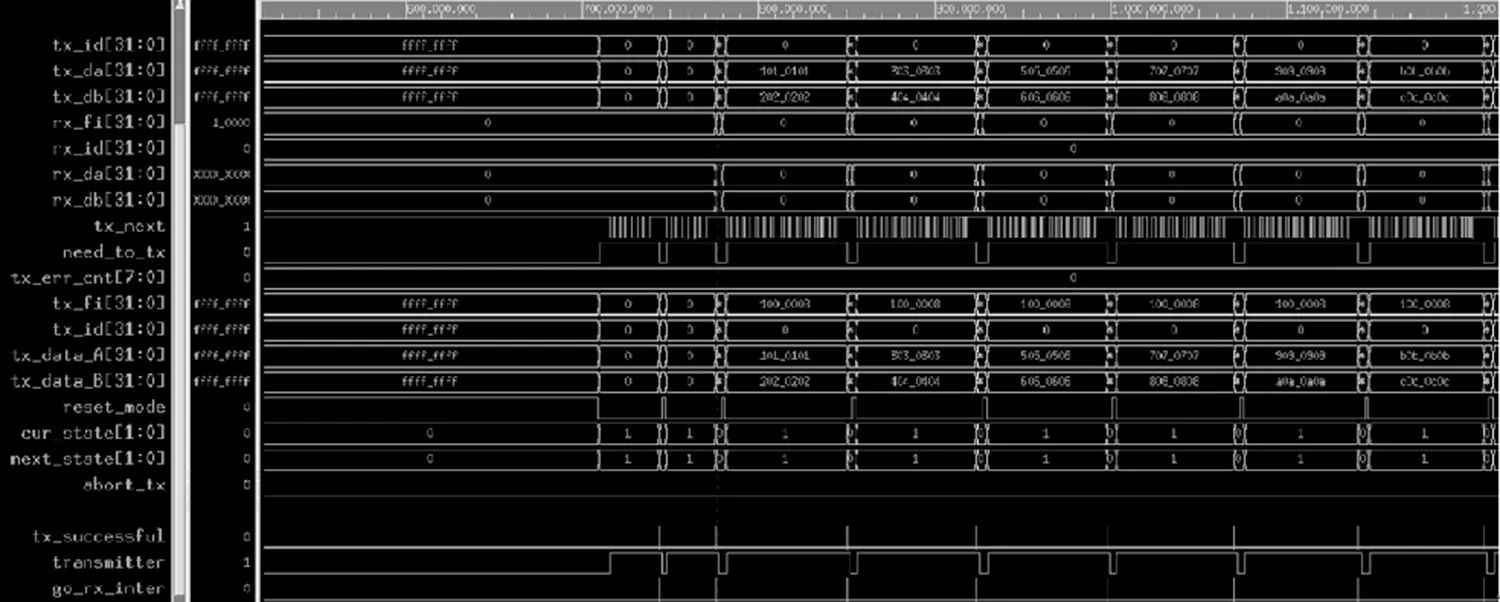

图5 仿真波形图

4.2 实验结果

CAN总线控制器的端口上是发送和接收数据的电平信号,通过VCS仿真工具,观察端口上的波形,如图5所示。

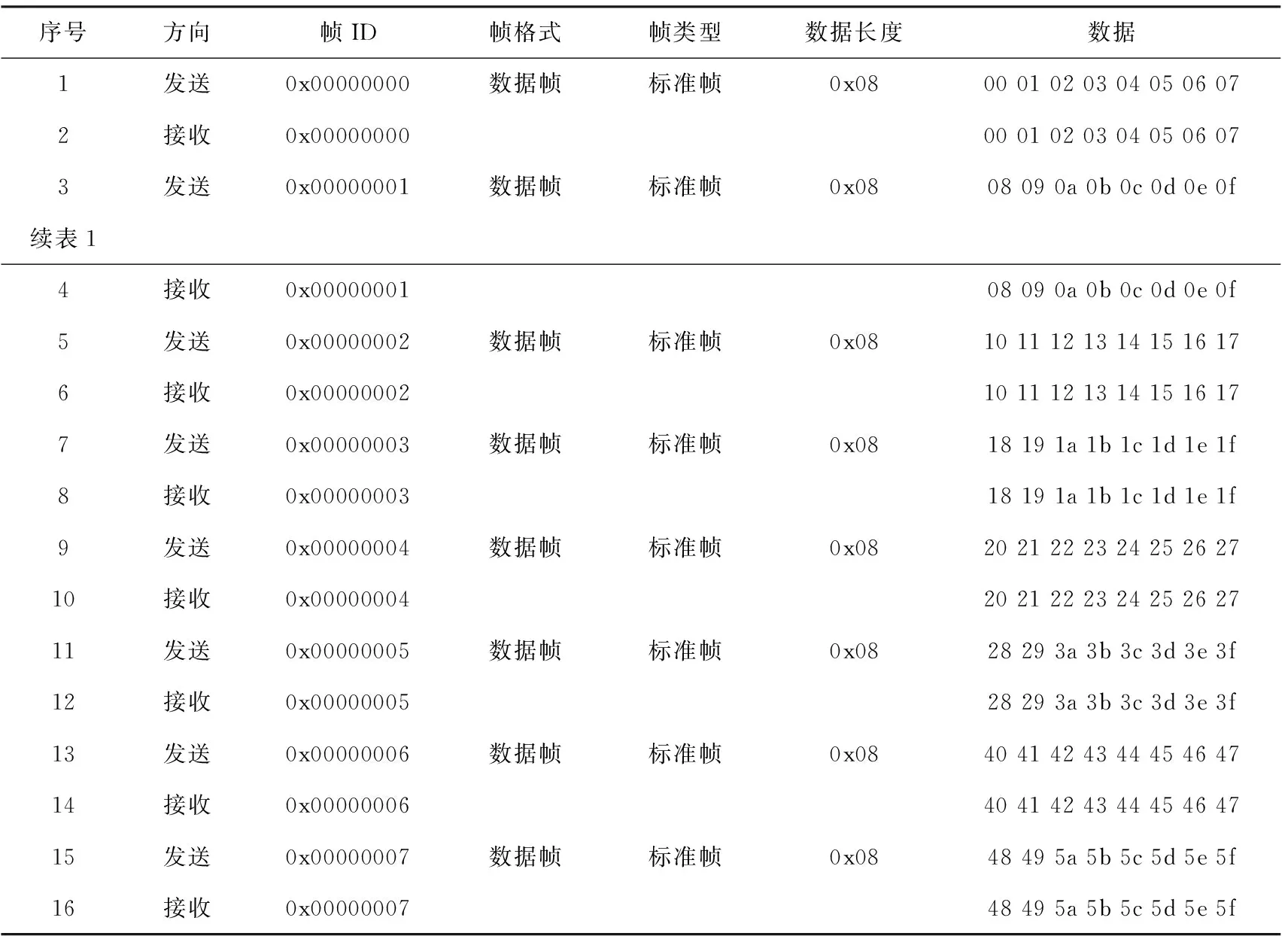

CANTest是致远电子开发的一款与CAN仿真器配套的软件,可以直接采集CAN总线上接收和发送的数据,并在终端上显示采集到的数据。连接FPGA与CAN仿真器,将驱动程序下载到FPGA上,进行复位运行,记录端口上发送和接收的实验数据,如表1所示。

表1 数据发送和接收传输结果

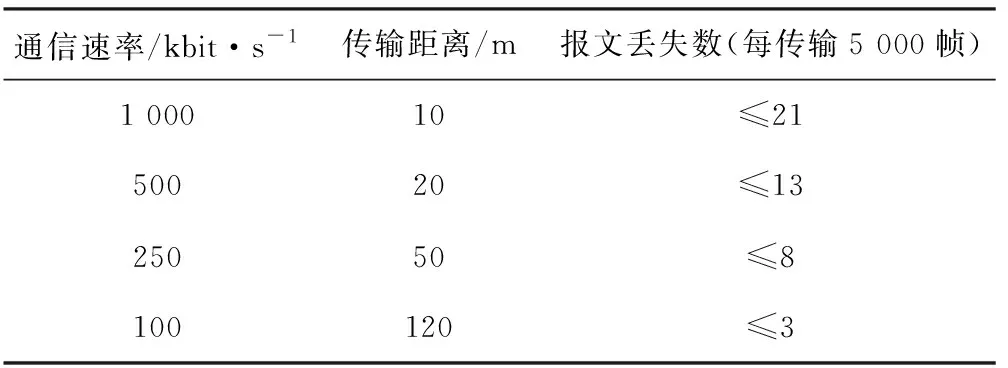

数据传输距离受到通信速率的影响,如表2所示:在通信速率1 Mbit·s-1下,在规定的距离内,数据可以正常的收发;120 m距离传输的条件下,采用100 kbit·s-1速率可以实现正常的数据传输。FPGA验证结果表明,CAN总线控制器的设计满足设计的需求,可以兼容通用的CAN总线控制器,正常完成通信的功能。对多次实验中报文丢失数量进行统计后发现,CAN总线控制器报文丢失率低,可以满足应用需求。

表2 传输数据结果

5 结束语

本文对设计的CAN总线控制器进行了充分验证,结果表明其功能满足设计需求,能够在1 Mbit·s-1速率下进行可靠传输,远距离传输报文丢失率低。CAN总线控制器接口挂载在AMBA总线上,可以方便地移植到其他SOC系统中。