硅通孔耦合抑制方法的研究综述

中国电子科技集团公司第三十八研究所 刘建峰

1.硅通孔三维互连耦合途径及等效模型

硅通孔(Through Silicon Via,TSV)技术是一种实现三维集成电路的有效解决方案,其结构是由William Shockley于1962年在一篇专利中首次提出,该技术能够使芯片在三维方向堆叠的密度最大、芯片之间的互连线最短、外形尺寸最小,具有缩小封装尺寸、高频特性出色、减小传输延时、降低噪声、降低芯片功耗和热膨胀可靠性高等优点。但是,随着信号工作频率越来越高、系统功能愈加复杂、芯片工艺节点尺寸越来越小,TSV与周围器件的耦合噪声成为限制三维系统性能提升的瓶颈。因此,研究耦合抑制方法对提高系统灵敏度、改善信号完整性、优化电磁兼容性具有重要意义。

硅通孔在三维互连中的耦合途径包含三种:TSV与TSV之间、TSV与金属连线之间、TSV与有源器件之间,下面对此三种途径进行详细介绍。

1.1 TSV与TSV之间的耦合

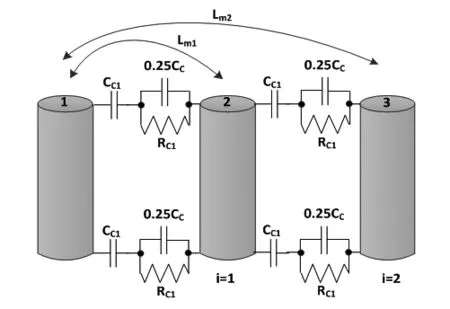

TSV与TSV之间的耦合关系可以用电容耦合、电阻耦合和电感耦合进行等效分析,图 1给出耦合等效模型,耦合强度与分布位置、分布方式以及TSV尺寸参数等相关。以5x5的TSV阵列为例,对于电容耦合和电阻耦合,除距离较近的TSV以外,其他TSV的耦合系数都很小;而对于电感耦合,耦合系数随距离下降较慢。原因在于,电容耦合由电场线形成,而电感耦合由磁场线导致,电场线会被周边的TSV金属填充屏蔽,而磁场线不会被屏蔽。

图1 TSV与TSV之间耦合等效模型

1.2 TSV与金属连线之间的耦合

TSV与金属互连线之间的耦合存在两种情况,一种是在via-f i rst工艺下金属连线位于TSV之上,TSV通过与之相连的金属层与上层金属形成纵向的耦合关系,另一种是在via-last工艺下TSV被互连线包围,形成以横向耦合为主的耦合模式。TSV与金属互连线之间的耦合电容受到它们之间的距离、线宽尺寸、数量和空间分布等多种因素的影响。

图2 不同工艺模式下TSV与金属互连线耦合关系示意图

1.3 TSV与有源器件之间的耦合

TSV通过具有一定电阻率的衬底将噪声耦合到有源器件中,在某些应用中信号的大小只有微伏量级,此时系统对耦合引起的开关切换噪声非常敏感,因此,理解TSV对MOS管的影响,以保证TSV的加入不会恶化有源电路的性能至关重要。图 3给出TSV与有源器件(MOS管)的耦合关系示意图,一种基于常规的Bulk衬底,另一种基于SOI衬底。以65nm CMOS工艺为例,TSV上的数字脉冲会引起衬底的尖峰噪声,尖峰噪声对会对CMOS管的饱和电流具有6μA/μm(沟道长度)的影响,对于泄露电流具有1.2μA/μm的影响。而SOI衬底具有更好的噪声隔离度,原因在于埋置氧化层对TSV与MOS管有源区之间的耦合起到了一定的隔离作用。

图3 TSV与有源器件(MOS管)的耦合关系示意图

2.耦合抑制方法国内外研究现状

近年来,国内外针对TSV互连耦合抑制方法研究的代表性成果如下:

美国西新英格兰大学的S.Adamshick等人在基于TSV三维集成进行在片天线的设计[1]中,对同轴TSV和传统TSV(S/G传输对)的隔离度进行了研究,测试结果表明,采用同轴结构,隔离度可以提高至少20dB以上,在20GHz左右时可以提高27dB。

挪威科技大学Hourieh Attarzadeh等人联合乔治亚理工大学对三维IC中堆叠策略进行了详细的研究[2],仿真结果表明,face-up集成策略对于耦合噪声具有优于face-down策略10dB的抑制度,并减小了23%的面积。

图4 基于接地屏蔽TSV建立等效模型仿真

图5 采用接地屏蔽TSV后耦合能量衰减仿真

日本松下公司Shinichiro Uemura等人于2012年发表了利用TSV进行衬底噪声隔离的成果[3],通过采用沟槽形状的TSV将SoC中的射频电路包围,测试结果表明,深槽TSV隔离技术与传统的保护环、深N阱、深槽隔离相比,可以在100MHz和1GHz处分别取得30dB和40dB的隔离度提升。

IBM公司Xiaoxiong Gu和Keith Jenkins于2013年发表了SOI工艺中TSV衬底耦合噪声的抑制方法[4],通过增加衬底的接地连接点,可以在1GHz处获得20dB的衬底噪声抑制度。

韩国科学技术院(KAIST)Jaemin Lim等人于2015年发表了关于TSV与有源电路隔离方法的报道[5],研究表明,5um宽的保护环可以降低30.4dB的相位噪声,8根接地屏蔽TSV可以降低24dB的相位噪声,二者结合可以降低30.7dB的相位噪声。

中山大学Jia-Yi Wu等人联合新加坡国立大学对三维TSV IC中衬底耦合噪声隔离进行了研究[6],于2014年发表了采用P+连接点和网格接地平面抑制衬底耦合噪声的研究成果,通过使用P+连接点抑制低频噪声、使用网格接地平面抑制高频噪声,通过简化模型分析与HFSS仿真验证,结果表明,在DC至50GHz之间,此种组合结构可以实现60dB的噪声抑制。

来自中科院微电子所得孟真等人对基于TSV封装的互连结构,进行了差分串扰建模研究[7],仿真表明,在10GHz~30GHz频段内,接地硅通孔能够降低8dB以上的临近硅通孔串扰。

来自北京大学微/纳米制造技术国家重点实验室Xin Sun等人,对硅基转接板的TSV阵列耦合进行了建模分析[8],仿真表明,近端串扰随距离增加而下降,在1GHz频点,通过增加距离可以提高40dB的抑制度。

北京大学Runiu FANG等人联合北京信息技术大学对20nm节点以上的TSV耦合噪声进行了建模分析[9],仿真表明,与保护环、SOI埋氧化层相比,接地TSV阵列具有更好的噪声抑制度,在1GHz以上频段,5个GND TSV可以增加20dB以上的噪声抑制。

西安电子科技大学微电子学院的Zheng Mei和Gang Dong对TSV和临近金属互连线之间的耦合电容进行了等效建模[10],结果表明,在不同场景下TSV和金属互连线之间耦合度基本小于-60dB,说明TSV与金属互连线之间的耦合噪声是比较小的。

3.耦合抑制方法实例设计验证

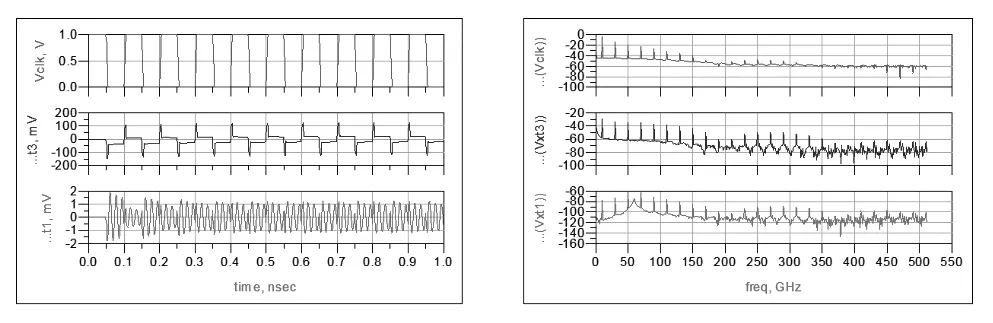

结合以上TSV耦合抑制方法的研究综述,本文针对TSV与TSV之间耦合抑制方法展开实例设计。基于接地屏蔽TSV的耦合抑制方法,如图4所示,在ADS中建立典型的仿真环境,接地TSV等效为电感串联电阻后与电容并联的网络,假设干扰源为10GHz的高速采样时钟,考虑硅衬底厚度为100nm,TSV直径为5um,长度为100um,TSV寄生电容为200fF,TSV之间的耦合电容为6fF,比较采用接地TSV前后,耦合噪声能量的变化。

如图5所示,左边为时域波形,右边为频谱,由上至下分别为输入时钟干扰源、未加屏蔽TSV的耦合信号、加入屏蔽TSV的耦合信号。从时域观察,未加屏蔽TSV时,信号峰峰值在200mV(耦合系数0.2),加入屏蔽TSV后,信号峰峰值为4mV(耦合系数0.04),耦合系数降低为1/50。从频谱观察,未加屏蔽的耦合信号频谱最大峰值为-30dB左右,加入屏蔽TSV后的频谱最大峰值降低为-60dB以下,即屏蔽TSV在全频带范围内实现了近30dB的噪声耦合抑制。从加入屏蔽TSV后的频谱趋势变化来看,屏蔽TSV对频谱两侧的噪声抑制更高,屏蔽网络具有带通的效果,对于10GHz以下的噪声耦合,噪声耦合具有大于70dB的抑制效果。

4.总结

硅通孔是超越摩尔技术路线中的重要方法之一,具有极大缩短互连长度、提高集成度、支持异构集成等优点,硅通孔使得三维系统或芯片尺寸急剧减小,在提高集成度的同时也增加了系统内部的耦合,多种途径的耦合严重影响了信号的完整性,因此针对硅通孔三维互连的耦合抑制方法成为研究热点。国内外的多家研究机构、高校、公司等对耦合抑制方法展开了研究,包括TSV与TSV、TSV与金属连线以及TSV与有源器件的耦合建模与测试分析,提出一系列针对性的耦合抑制方法,形成了基于硅通孔三维芯片或三维系统的设计准则。本文针对TSV与TSV之间的耦合抑制方法展开了实例设计验证,仿真表明接地屏蔽TSV可有效抑制高速数字信号的高频分量,有利于减小其对模拟电路的干扰,该结果可为基于TSV的三维混合信号微系统开发提供设计指导。

[1]Adamshick S,Johnson A,Moriarty K,et al.Antenna on Chip Design Utilizing 3D Integration for Mixed Signal Applications[J].

[2]Attarzadeh H,Lim S K,Ytterdal T.Stacking integration methodologies in 3D IC for 3D ultrasound image processing application:A stochastic flash ADC design case study[C].IEEE ISCAS,2015:1266-1269.

[3]Uemura S,Hiraoka Y,Kai T,et al.Isolation techniques against substrate noise coupling utilizing through silicon via(TSV)process for RF/mixed-signal SoCs[J].IEEE JSSC,2012,47(4):810-816.

[4]Gu X,Jenkins K.Mitigation of TSV-substrate noise coupling in 3-D CMOS SOI technology[C].IEEE EPEPS,2013:73-76.

[5]Lim J,Lee M,Jung D H,et al.Shielding structures for through silicon via(TSV)to active circuit noise coupling in 3D IC[C].IEEE EMC Compo,2015:248-251.

[6]Wu J Y,Zhang M S,Tan H Z,et al.Substrate noise coupling isolation using P+ contact array and grid ground plane in RF/mixedsignal 3D TSV ICs[C].IEEE EPEPS,2014:183-186.

[7]孟真,张兴成,刘谋,等.TSV 封装中互连结构的差分串扰建模研究[J].微电子学与计算机,2017,9:001.

[8]Sun X,Zhu Y,Ma S,et al.Electrical modeling,simulation and SPICE model extraction of TSVs in Silicon Interposer[C].IEEE EPTC,2011:171-174.

[9]Fang R,Sun X,Jin Y,et al.Modeling and analysis of TSV noise coupling and suppression methods for 20nm node and beyond[C].IEEE ICEPT,2014:783-787.

[10]Zheng Mei,and Gang Dong.Analysis of Coupling Capacitance between TSV and Adjacent RDL Interconnections.2017 IEEE CPMT Symposium.