一种低功耗8位300 MS/s异步SAR ADC

钱 正,赵 新,龚 敏,高 博,谭 萍,王堋钰

(四川大学物理科学与技术学院,成都 610064)

1 引言

在各种类型的ADC中,逐次逼近模数转换器(SAR ADC)的主要优势在于功耗方面[1],而传统SAR ADC在速度方面有所制约。为了提高SAR ADC的转换速率,主要有两种设计单通道高速SAR ADC(采样速率在100 MS/s以上)的方法被提出。一种结构是一次循环比较出2~3位的数字码[2~3],可以成倍增加ADC的速度。另一种结构是通过增加比较器的个数,从而实现异步SAR ADC的转换[4],这种结构大幅度减少了比较器的置位时间,增加了模数转换的速度。然而,由于增加了比较器的个数,使得电路的功耗也有所增加。

SRA ADC的延迟主要由DAC的置位时间、比较器的延迟时间以及SAR逻辑的延迟时间组成,从而限制了ADC的整体转换速率。本文设计中为了平衡速度与功耗,依旧采用每循环比较一位数字码的结构,使用异步时钟电路提高SAR ADC整体的工作速度,并且采用了高速DAC的时序、改进后的高速比较器以及动态SAR逻辑单元,分别对三部分延迟时间做了优化。

2 ADC结构与异步时钟

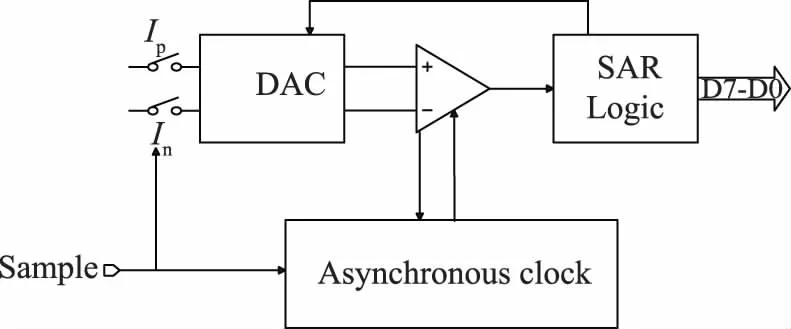

本次设计的SAR ADC结构框图如图1所示。此电路包括DAC电容阵列、一对自举开关、高速比较器、SAR逻辑单元以及异步时钟单元。在采样过程中,自举开关对输入信号Ip和In进行采样,此时时钟电路为低电平,比较器处于复位阶段。采样过程结束后,DAC根据做出相应的反应,将信号传输到比较器的输入端。时钟产生上升沿触发比较器进行比较。高速比较器的结果输出到SAR逻辑单元,生成该位的数字码,并且反馈到DAC阵列的开关时序中,从而实现逐次比较的循环。比较器的比较结果也会反馈到时钟电路中,从而使时钟电路产生稳定的时钟信号控制比较器。

图1 高速低功耗SAR ADC结构图

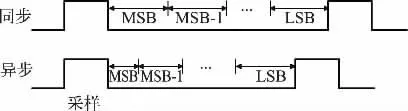

由于输入电压差不同,比较器响应时间会有所改变,如图2所示,异步时钟不需要划分相同的时间周期完成比较,而是根据比较时间自动分配时钟。因此采用异步时钟可以节约大量的时间,从而提高SAR ADC的整体速度。

图2 异步时钟与同步时钟时序对比

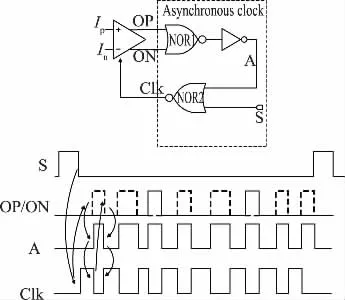

如图3所示,当采样信号为高电平时,时钟信号被或非门NOR2置为低电平,使比较器处于复位阶段,此时比较器两端输出均为低电平,A节点为低电平信号。当采样结束时,由于A节点和采样信号同时为低电平,则Clk时钟产生高电平,使比较器处于比较阶段,并且比较器其中一端的输出为高电平,此时A节点为高电平,从而使得时钟信号Clk再次变为低电平,比较器再次进入复位阶段。在ADC工作阶段,时钟电路会产生稳定的异步时钟信号,直到下一次采样信号的到来。

图3 本设计异步时钟电路以及时序图

3关键电路设计

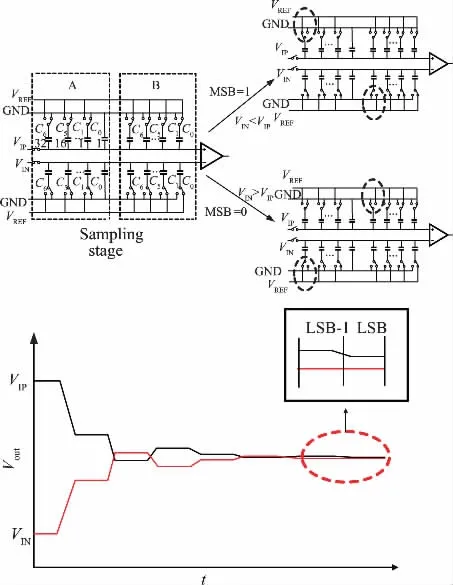

3.1 分裂式顶端采样DAC

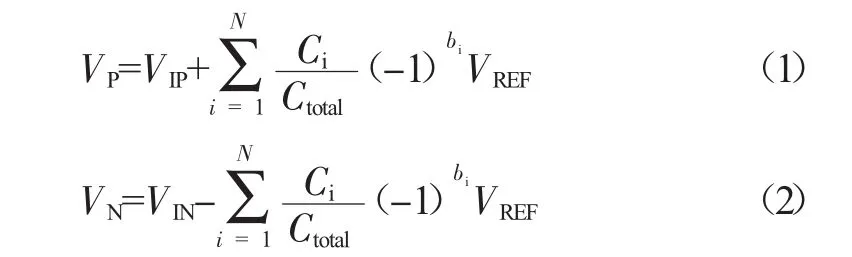

分裂式顶端采样DAC[5]结构以及DAC时序如图4所示。分裂式顶端采样电容阵列将传统的上极板采样DAC电容阵列[6]的每一位电容拆分成了大小相等的子电容,这种电容结构可以改善传统上极板采样DAC的共模电平移动的问题,同时可以减少DAC的置位时间。在采样过程中,A部分电容的下极板接地,B部分电容的下极板接基准电压,与此同时,自举开关对输入端Vip和Vin进行采样。采样结束后,根据最高位的比较结果,电容阵列做出相应的变化。以最高位电容为例,若Vip端的电压高于Vin端的电压,最高位MSB=1,则Vip端B部分的最高电容C5的下极板由接基准电压变为接地,Vin端A部分的最高位电容C5由接地变为接基准电压;若Vip端的电压低于Vin端的电压,最高位MSB=0,则Vin端B部分的最高电容C5的下极板由接基准电压变为接地,Vip端A部分的最高位电容C5由接地变为接基准电压。但是最低位电容只由B部分的单位电容C0连到地所决定,除了最低位变换其他位的时序变换均由上述变换方式工作。最低位的转换只由B部分的电容C0从基准电压到地完成。除最低位转换,DAC的输出由式(1)和(2)表示,i=[7,6,5,4,3,2]。

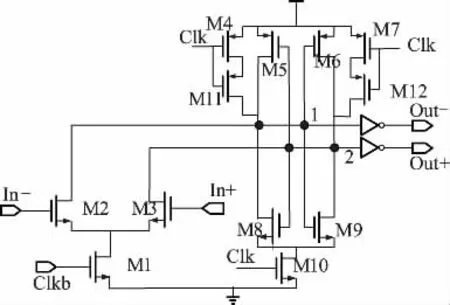

3.2 高速比较器

本次设计的高速比较器如图5所示。该比较器包含一级预放大级,且该放大级没有单独的负载,而是将锁存器的PMOS作为负载[7]。根据文献[8]给出的分析,比较器输出由复位到比较结果完成的延迟时间分为两部分,分别为电压由输出电压从复位电压拉至管子的阈值电压Vt的时间t0和输出电压从Vt直至正反馈完成的时间tlatch。两者的公式见式(3)和式(4)。

其中,CL是比较器输出端的负载电容,Vcharge是复位电压到阈值电压的电压差,IEq是锁存器中NMOS管的电流。

其中,gmeff为锁存器中MOS管(M4和M7)的跨导,ΔVOUT为寄存器可以识别的电压差,G为放大级的增益,ΔVIN为从DAC输出到比较器的电压差。

图4 DAC开关时序图

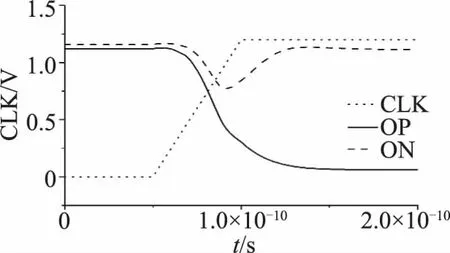

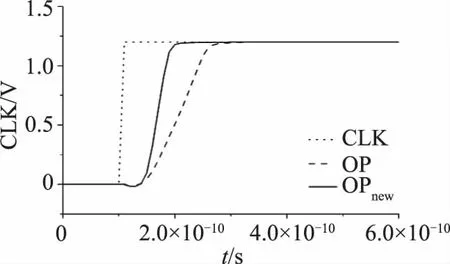

比较器中节点1和节点2的输出波形图(反相器输出前的波形图)如图6所示。由(3)式可以看出,Vcharge的减小可以减小延迟时间,所以本设计采用预放大级和锁存器共用PMOS作为负载的结构,可以使得节点1和节点2的复位电压略低于VDD,从而使得Vcharge减小。由(4)式可以看出,适当增加M4和M7的跨导也可以减小延迟时间。但是,如果增加过多,会增大输出的节点电容,本设计在负载管M4和M7的基础上串联了PMOS管M11和M12,由于电容串联会使得总电容减小,从而负载管在输出节点的寄生电容有所降低。图7为输入为9.3 mV(1 LSB)时两种比较器的输出电压(输出比较器后),虚线和实线分别为串联了负载管M11和M12前后的高电平输出结果,由仿真结果可以看出,改进后的延迟时间减少了20 ps。

图5 高速比较器

图6 比较器中节点1和节点2的输出波形图

图7 串联负载管M11和M12前后输出波形图

3.3 高速自举开关

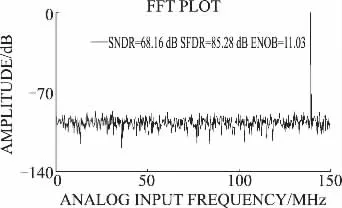

在高速低压的情况下,普通CMOS传输门的线性度严重下降,因此需要自举开关来减小开关的导通电阻,从而提高开关的线性度[4]。采样开关电路图如图8所示,当采样信号为低电平时,M3为导通状态,M5为关断状态;M8管为导通状态,地信号通过M8管到节点2;M1管和M2管为导通状态,从而使M4导通,节点1被升到VDD。M6、M7、M9和M10均为关断状态,使得电容C的上下基板的电压差为VDD。当采样信号为高电平时,M1、M3、M4、M8 管关断,M5、M6、M7、M9和M10处于导通状态,这样在采样阶段,开关管M10的栅端被自举到VDD+VIN,使得VGS稳定在1.2 V,提升了开关的线性度。在采样频率为300 MHz(采样时长为0.5 ns)、输入信号频率为140.5658 MHz时的输出频谱如图9所示,有效位数达到11位,能满足8位模数转换器的要求。

图8 自举采样开关

图9 采样开关频谱图

3.4 低功耗SAR逻辑电路

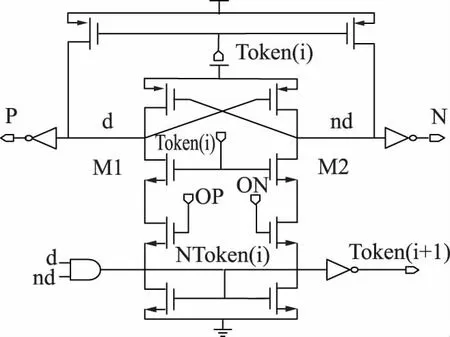

SAR逻辑部分由8个控制单元组成,每个控制单元负责储存一位的数字信号,并且控制DAC的时序[9],SAR逻辑控制单元如图10所示,时序图如图11所示。每一个控制单元的Token(i)信号在该次比较进行之前产生高电平,当Token(i)信号为低电平时nd和d端信号均为高电平。Token(i)信号产生高电平之后,当比较结果从OP和ON端输入时,nd信号和d信号会随之做出反应,并且经过与门将NToken(i)拉到地锁住控制单元,同时输出端P和N会产生高低电平,并将之储存起来。NToken(i)会再经过一级反相器产生下一个控制单元的Token信号(最高位的Token信号为采样信号的反)。由于Token信号的存在,使得在该次比较到来之前,没有电流从M1和M2流过,大幅度减少了不必要的功耗。并且当比较信号来临时,nd和d经过一条支路就可以在第一时间做出反应,减少了储存数据所需要的时间。

图10 SAR逻辑控制单元

图11 逻辑单元时序图

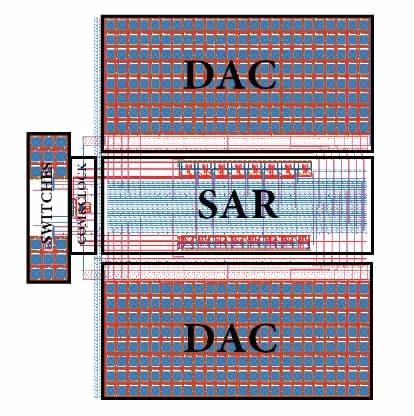

4 版图与仿真结果

本次设计的版图及验证基于SMIC 65 nm 1P5M CMOS工艺,如图12所示,版图有效面积为180 μm×201 μm,基于1.2 V电源电压,在采样频率300 MS/s下的奈奎斯特输入频率进行测试。经过测试,在1.2 V电源电压下,整个8位SAR ADC的功耗为0.84 mW,其中SAR逻辑部分和异步时钟部分为功耗的主要来源,比例分别为47%和37%,其余功耗来自DAC部分与比较器部分,比例分别为9%和7%。

图12 SAR ADC版图

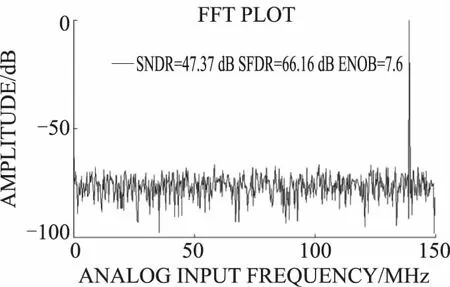

奈奎斯特输入下的频域测试结果如图13所示,结果显示当输入信号频率为140.5658 MHz时,SNDR为47.37 dB,SFDR为66.16 dB,有效位数为7.58位。根据公式(5)计算出品质因数(FOM)为16.6 fJ/conv。

对应不同输入频率,相应的SNDR和SFDR如图14所示。在输入频率较低时,SNDR略有升高,根据公式(6),有效位数也会相应升高,SFDR基本没有影响。

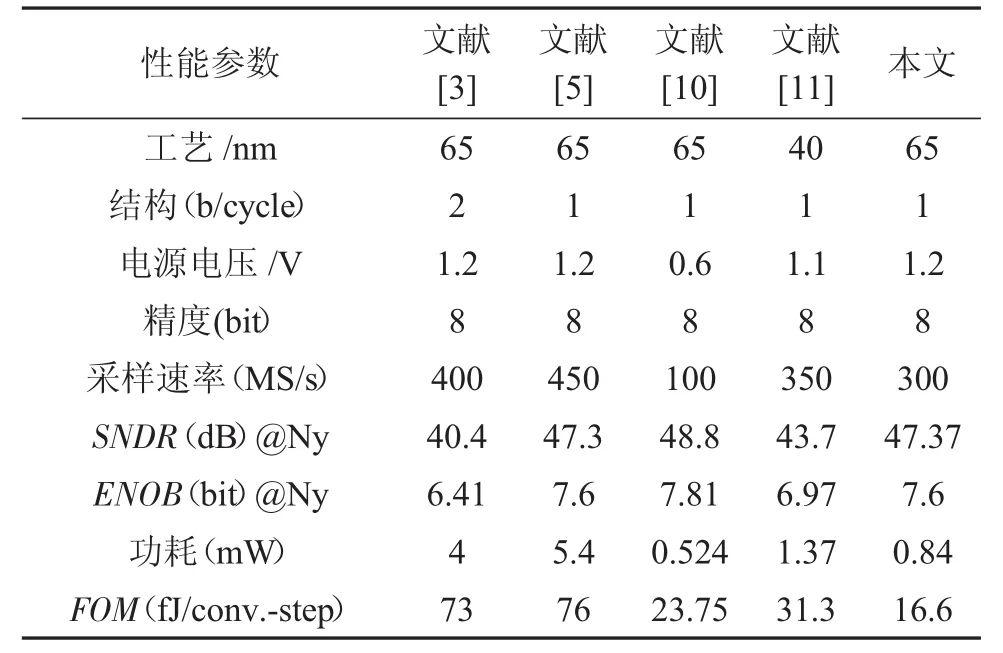

表1给出了本设计与近年来发表的SAR ADC进行的对比。在65 nm工艺下,本设计的1位/循环的ADC在保证有效位数的情况下,速度上达到了先进的水平。由于采用了很多低功耗的设计方案,本设计在同等水平采样速率的ADC中功耗有着明显的优势。文献[10]采用低压的方式,在功耗上有着明显优势,但是由于本文在速度上高于文献[10],因此本设计有着很低的功耗效率(FOM)。特别指出,在65 nm工艺下,文献[5]为包含一个比较器的SAR ADC中速度最快的,在该设计中,为了提高速度使用了两级预放大的比较器。在本文的设计中,为了降低功耗采用一级预放大的改进型高速比较器,虽然速度略有下降,但是功耗方面优势显著。

图13 SAR ADC输出信号频谱(fin为奈奎斯特频率)

图14 不同输入频率下ADC的SNDR和SFDR

表1 SAR ADC性能比较

5 结论

本文基于SMIC 65 nm 1P5M CMOS工艺,设计了一种1 bit/循环的高速低功耗逐次逼近模数转换器。经版图后仿验证,在1.2 V电源电压以及300 MS/s的采样频率下,总功耗为0.84 mW。ADC的信噪失真比(SNDR)达到47.9 dB,有效位数(ENOB)达到7.6位,品质因数为16.6 fJ/Conv。与其他参考文献进行对比,本文设计的SAR ADC在高速下同时有着很低的功耗,具有很大优势。

[1]J L McCreary,P R Gray.All-MOS charge redistribution analog-to-digital conversion techniques—Part I[J].IEEE J.Solid-State Circuits,1975,10(12):371-378.

[2]Z Cao,S Yan,Y Li.A 32 mW 1.25 GS/s 6 b 2 bit/step SAR ADC in 0.13 μm CMOS[J].IEEE J.Solid-State Circuits,2009:862-873.

[3]H Wei,C-H Chan,U Chiao,S W Sin.An 8-b 400-MS/s 2-b-per-cycleSARADCwithresistiveDAC[J].IEEEJ.Solid-State Circuits,2012:2763-2772.

[4]T Jiang,W Liu,F Y Zhong,C Zhong,K Hu,P Y Chiang.A single-channel,1.25-GS/s,6-bit,6.08-mW asynchronous successive-approximation ADC with improved feedback delay in 40 nm CMOS[J].IEEE J.Solid-State Circuits,2012:2444-2453.

[5]V Tripathi,B Murmann.An 8-bit 450-MS/s Single-Bit/Cycle SAR ADC in 65 nm CMOS[J].ESSCIRC,Sep.2013:117-120.

[6]C-C Liu,S-J Chang,G-Y Huang,Y-Z Lin.A 0.92 mW 10-bit 50-MS/s SAR ADC in 0.13 μm CMOS Process[J].Symp on VLSI Circuits,2009:236-237.

[7]M Abbas,etc.Clocked comparatorforhigh-speed applications in 65 nm technology[C].IEEE Asia Solid-State Circuits Conf,2010:1-4.

[8]B Wicht,T Nirschl,D Schmitt-Landsiedel.Yield and speed optimization of a latch-type voltage sense amplifier[J].IEEE J.Solid-State Circuits,2004:1148-1158.

[9]J-H Tsai,Y-J Chen,M-H Shen,P-C Huang.A 1-V,8b,40MS/s,113 μW Charge-Recycling SAR ADC with a 14 μW Asynchronous Controller[J].Symp.on VLSI Circuits,2011:264-265.

[10]Wen-LanWu,Yan Zhu,Li Ding,Chi-Hang Chan,UFatChio,Sai-WengSin,U Seng-Pan,RuiPaulo Martins.A 0.6 V 8 b 100 MS/s SAR ADC with minimized DAC capacitance and switching energy in 65 nmCMOS[C].ProceedingsofIEEE InternationalSymposium On Circuitsand Systems,ISCAS,2013:2239-2242.

[11]K Ragab,N Sun.A 1.4 mW 8 b 350 MS/s Loop-Unrolled SAR ADC with Background Offset Calibration in 40 nm CMOS[C].ESSCIRC Conference,2016:417-420.