基于UltraFlex系统的FPGA直流参数补偿测试方法

陈 诚,陈 龙,肖艳梅

(1.中国电子科技集团公司第五十八研究所,江苏无锡 214035;2.江南大学物联网学院,江苏无锡 214062)

1 概述

现场可编程集成电路FPGA是在信息产业中硬件、软件和系统集成三位一体、不可取代的高端处理芯片,可通过软件编程实现不同的硬件功能,具有超强的灵活性,可实现各领域逻辑控制、信号处理、数据运算等功能,对电子信息系统的先进性、安全性、可靠性等起着决定性作用。

对于FPGA等较大规模或管脚数多的器件,在测试时需要选择支持多通道数和更大向量深度的测试系统。泰瑞达公司的UltraFlex测试系统是用于高性能数字和片上系统的测试解决方案,适用于200 MHz以上高速度、高精度、高性能和多site测试。

2 FPGA测试原理

在UltraFlex测试机上对FPGA进行测试主要分为3个步骤:首先,通过测试系统将测试向量配置进FPGA,在配置FPGA的过程中,测试向量为时序控制器提供了配置文件存储器的片选信号和页选信号,并为FPGA提供了配置模式选择信号和编程信号;其次,测试系统为FPGA提供激励信号;最终,通过检测器件的响应信号和理想情况进行比较,判断FPGA的功能和性能。这一系列测试过程的正常运行需要依赖于FPGA和自动测试系统连接的DUT板。基本原理框图如图1所示。

图1 测试系统连接图

3 补偿方案

3.1 补偿方案原理

在对FPGA进行测试的过程中,由于FPGA电路引脚数量多、驱动电流大,所以对测试设备的直流参数测试能力提出了更高的要求。例如Xilinx公司的V4/V5系列FPGA的IO端口数量可达上千个,并且此系列FPGA支持LVTTL/LVCMOS/HSTL/SSTL/PCI等三十多种直流参数电平。其中在HSTL_IV_1.5 V和HSTL_IV_1.8 V电平模式下对直流参数进行测试时,需要满足每个IO端口为48 mA的驱动要求。在GTLP电平模式下对直流参数进行测试时,需要满足每个IO端口为36 mA的驱动要求。

由于V4/V5系列FPGA的BGA封装引脚数较多,插座与DUT板多采用pogopin精密连接器的方式进行连接,此种连接方式不可避免地会使得弹簧针与测试板PAD接触时引入通路电阻的问题,并且基于对测试成本和测试时效性的考虑,现在UltraFlex测试多采用子母板方案,子母板使用的100 pin高频接插件也会引入一部分通路电阻。在测试驱动电流较小的直流参数时,这些通路电阻对测试输出高低电平的影响不明显,但也影响了测试结果的精确性。在测试驱动电流为36 mA和48 mA等非常大的直流参数时,这些通用电阻对输出高低电平会产生较大的误差,严重时甚至会使原本符合规范的直流参数超出规范上下限,从而导致测试失效。由于测试硬件环境不可避免地引入了通路电阻,因此在测试大电流负载直流参数时需要对这些通路电阻进行修正,从而消除这部分电阻引入的测试误差。

3.2 自带模板介绍

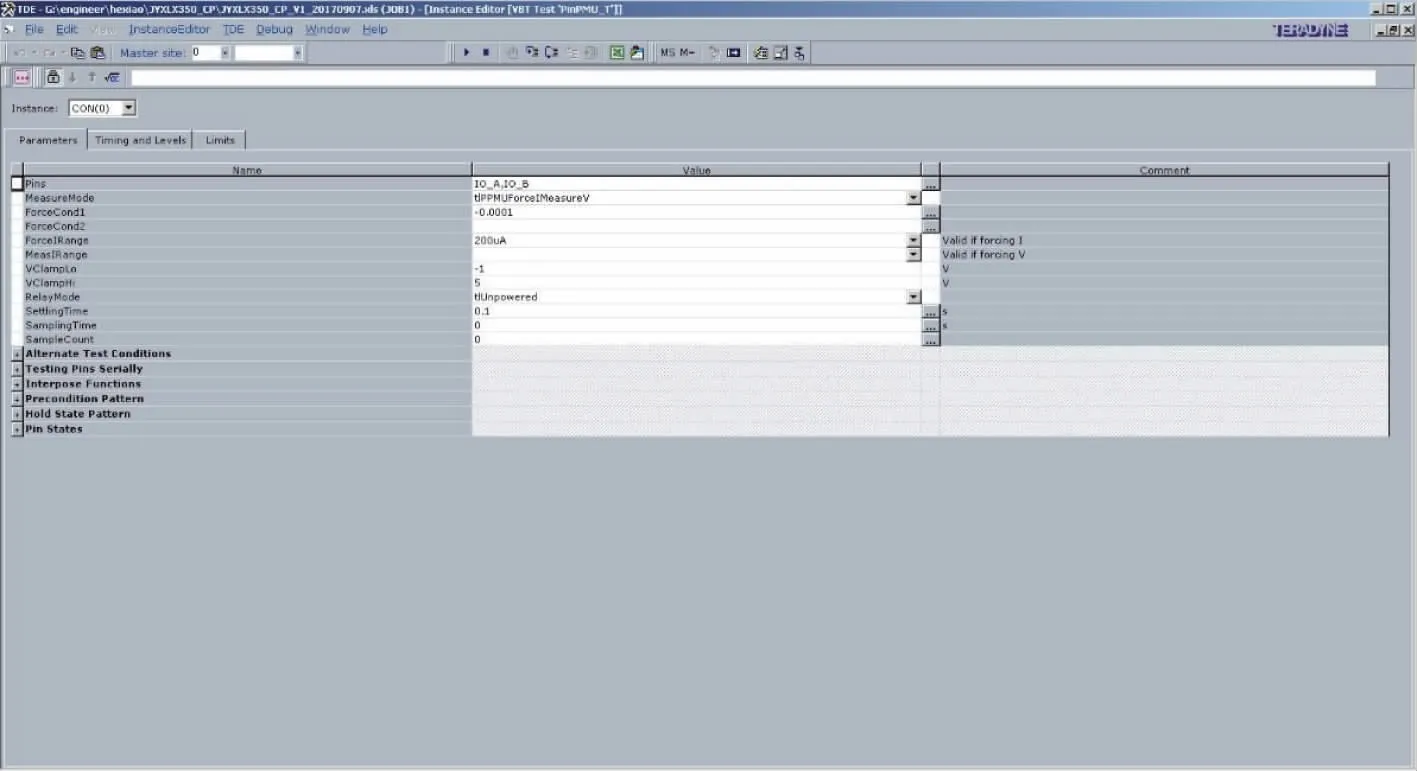

在对IC电路的直流参数进行测试时,一般使用UltraFlex的IG-XL测试软件自带的PPMU模板。由于泰瑞达公司提供用户使用的PPMU模板是固定格式的模板,因此无法在此模板上对通路电阻引入的误差进行修正,PPMU模板界面图如图2所示。

图2 IG-XL PPMU测试界面图

3.3 改进模板介绍

针对通路电阻引入的误差问题,本文提出一个自主编写改进模板的办法,可以修正通路电阻引入的误差。

改进模板是在泰瑞达IG-XL的PPMU模板的基础上进行编写。泰瑞达IG-XL的PPMU模板有很多可供选择调试的功能,在测试FPGA的过程中有一些调试功能是多余的,改进模板去除了PPMU模板中的多余调试功能,只编写了我们所需要的调试功能。改进模板包括测试引脚、测试预加载向量、预加载向量起始位置、预加载向量停止位置、检查PAT正确性、测试电流值和测试电流量程范围等。同时,为了提供程序编写的便利性,原本需要在flowtable中单独填写的参数值测试上下限也集成到了改进模板中。

在测试VOH时,负载电流IL的方向是由电路引脚流出外部,在测试机软件中以负值标注,此时IL<0,因此乘测试通路电阻RB后计算出的通路压降ΔV<0。在测试VOL时,负载电流IL的方向是由外部向电路引脚流入,在测试机软件中以正值标注,此时IL>0,因此乘测试通路电阻RB后计算出的通路压降ΔV>0:

测试VOH高电平驱动时,测试通路电阻RB带来的误差会使得修正前VOH测试值VOHP偏低,若想要消除这部分误差,应该加上通路压降ΔV得到修正后VOH的测试值VOHT。而此时通路压降ΔV<0,使用修正前测试值减去通路压降ΔV(此时为负值)即可达到加上通路电阻压降的效果。

测试VOH低电平驱动时,测试通路电阻RB带来的误差会使得修正前VOL的测试值VOLP偏高,若想要消除这部分误差,应该减去通路压降ΔV得到修正后VOL的测试值VOLT。而此时通路压降ΔV>0,使用修正前的测试值减去通路压降ΔV(此时为正值)即可达到减去通路电阻压降的效果:

通路电阻阻值采用实际测量子板插座引脚到母板底部之间电阻的方式得到,经过实测确定通路电阻阻值约为2~4 Ω,改进模板选择3 Ω进行修正。

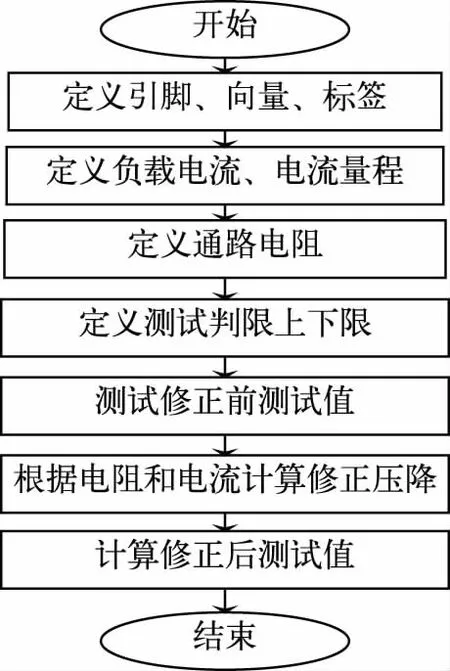

本文使用VB语言编程将以上通路电阻压降消除原理进行了实现,流程图如图3所示。

图3 程序流程图

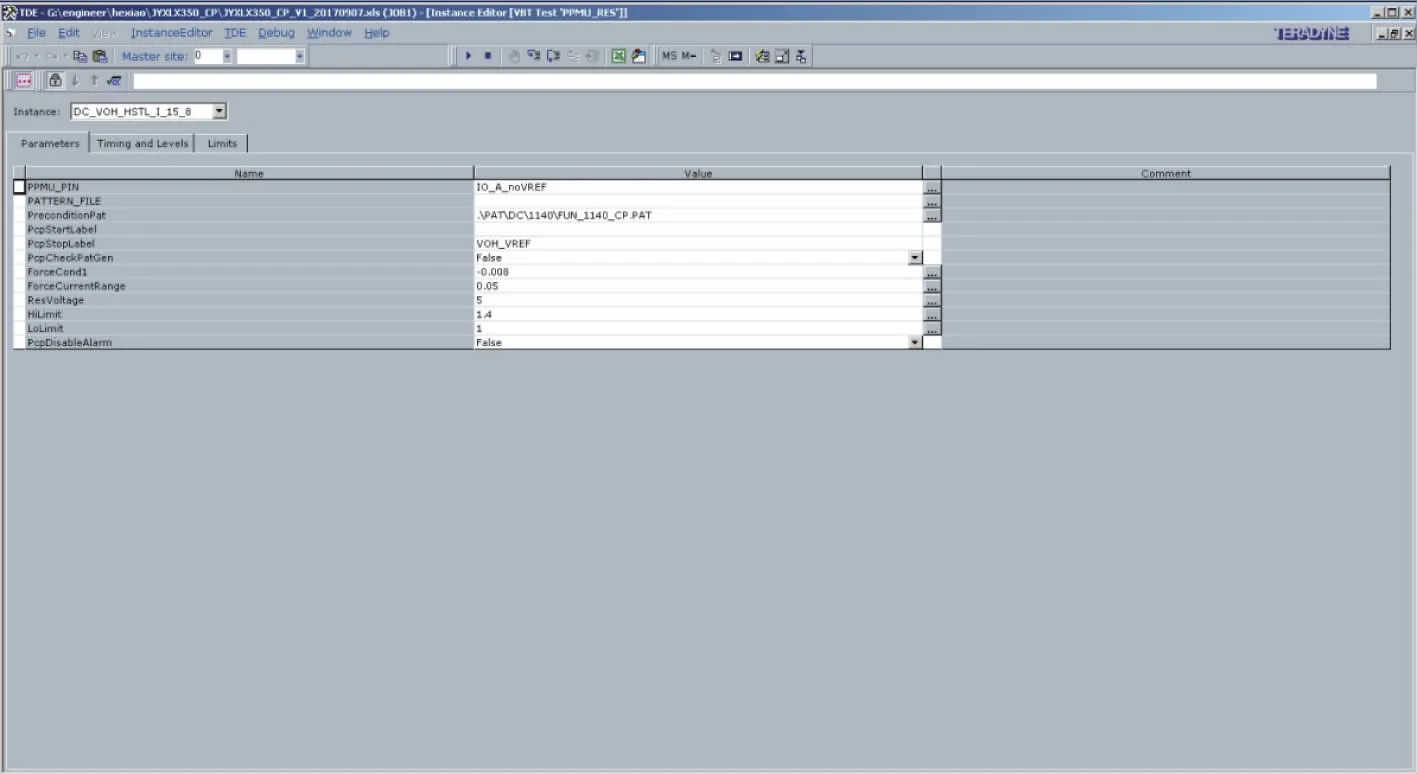

以下是改进模板的VB代码,改进模板测试界面图如图4所示。

图4 改进模板测试界面图

4 测试实例

为了验证该VBT改进模板的使用效果,本文以Xilinx公司Virtex-4系列FPGA中的XC4VSX25为例,在HSTL_IV电平模式下对封装为BGA668的XC4VSX25进行直流参数测试,测试条件为负载电流48 mA。

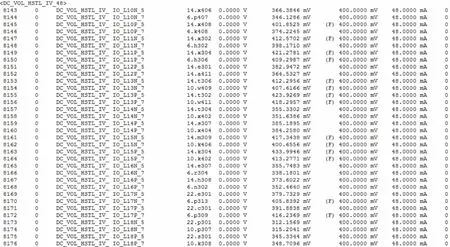

使用IG-XL自带PPMU直流参数测试模板测试时发现几十个引脚超标失效,测试值与实装板验证值不一致,测试结果明显不正常,测试结果受到通路电阻带来的压降影响很大。实验数据如图5所示。

图5 PPMU模板测试数据

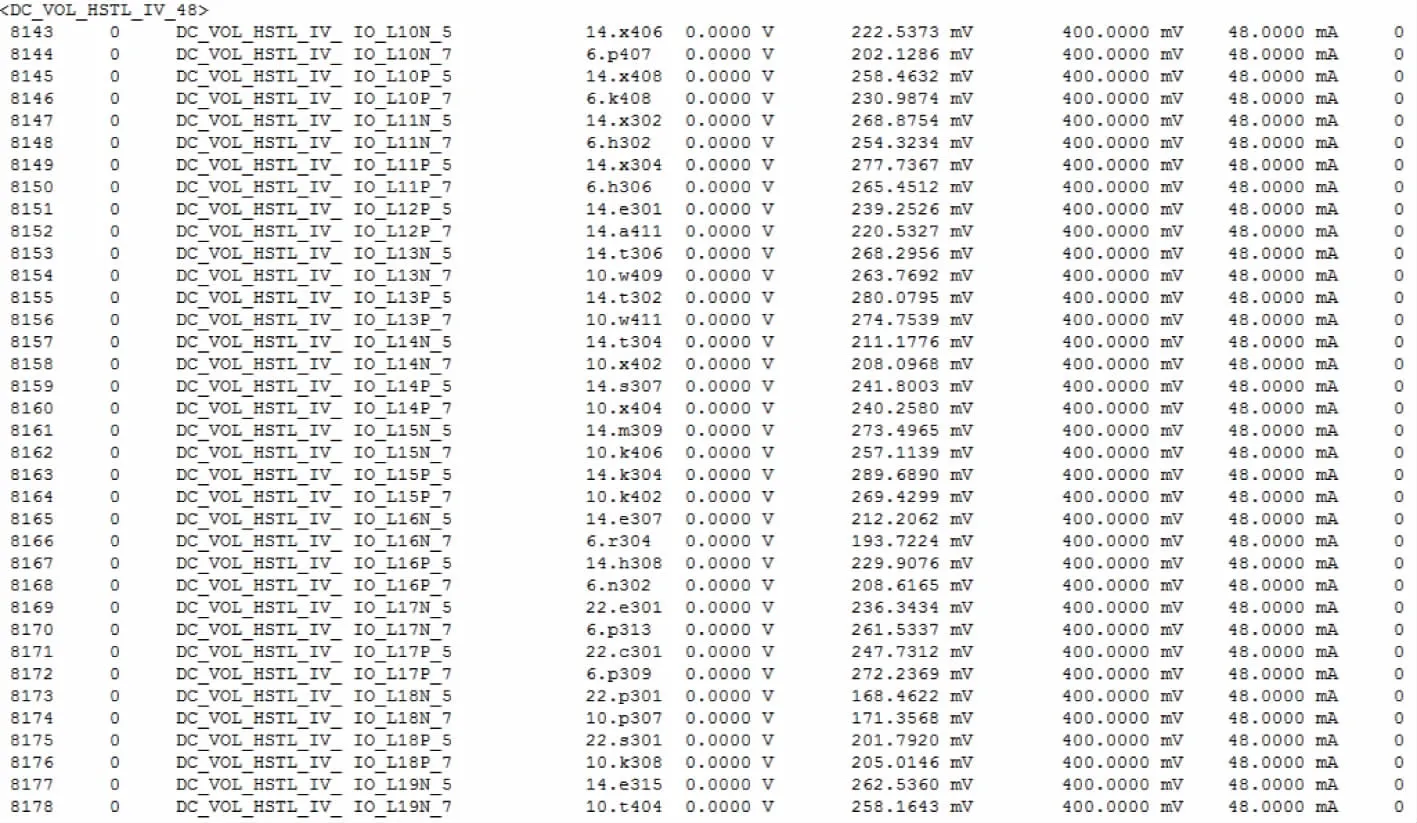

使用我们编写的带阻值修正的VBT模板的测试效果显示,所有引脚正常通过,测试值与实装板验证值一致,测试结果正常,改进模板对于修正引入电阻带来的误差具有很好的效果,实验数据如图6所示。此改进模板不仅可以应用到FPGA的测试中,也可以应用在其他类型的集成电路测试中。

图6 改进模板测试数据

5 结束语

本文主要叙述了在测试FPGA过程中不可避免产生引入电阻和消除引入电阻的原理,在泰瑞达IG-XL的PPMU模板基础上自主编写了一种改进模板来消除引入电阻对测试结果的影响。在对FPGA的实际测试应用中,该改进模板可以大大提高对于FPGA直流参数测试的准确性,同时对其他类型的电路测试也有借鉴作用。

[1]孟宪元.可编程ASIC集成数字系统[M].北京:电子工业出版社,1998.

[2]Xilinx.Using Serial Vector Format Files to Program XC9500/XL/XV Devices In-System[P].XAPP067,2002.

[3]Xilinx.利用嵌入式微控制器实现Xilinx在系统编程[P].XAPP058,2007.

[4]Xilinx.The Programmable Logic Data Book[M].1999.