基于FPGA的高速光纤传输卡

朱 琛,崔 镭,邵春伟,王小龙

(中国电子科技集团公司第五十八研究所,江苏无锡 214072)

1 引言

随着现代通信技术的飞速发展,光纤通讯得到了广泛应用。光纤通讯是一种利用光与光纤传递资讯的方式,具有频带宽、损耗低、传输数据量大等优点,因而应用越来越多,其发展也日趋成熟。在业内公司中,安捷伦在数据采集与测量方面都处于技术领先地位,安捷伦公司推出的U1080A系列高速数据采集卡,其配备的MR0LI2类型的光模块有12路并行光通路,每条通路的传输率可以达到2.7 Gbit/s,最大传输速率可以达到30 Gbit/s[1]。美国内达华州的4DSP公司致力于开发坚固的高性能数据处理板卡用于满足军事、航空航天等科学应用的具体要求。4DSP开发的FM482数据处理板支持1 Gbit/s的采样率,8 bit位输出的数据采集卡;在数据传输方面,板卡可以通过光纤连接远端主机处理系统或者数据存储系统,共有4条光纤传输通路,每条光纤通路的最大传输速率2.5 Gbit/s[2]。光纤数据采集技术最先在国外发展起来,国内近些年也开始慢慢发展起来,但技术还不够成熟,尤其在一些军工领域缺乏运用。

本文设计实现了一种基于FPGA的高速光纤传输卡,将雷达数据有效快速地通过光纤传输到FPGA传输卡上,再通过PCI Express接口发送到PC机上。

2 系统组成

总体设计如图1所示。本系统选用了Xilinx公司的XC7K325T进行逻辑设计。采集数据经由光纤模块传输进入FPGA中并缓存在大容量DDR3 SDRAM中,通过总线DMA的控制,将数据通过X4通道的PCI Express协议以不低于320 MB/s的速度传输到主机的存储设备。在主机端,使用C++语言开发PCIe光纤接口卡应用程序界面以提供操作方式,通过驱动程序间接控制板卡实现数据传输控制和工作。最后,在主机端上设计应用程序界面以实现对前端数据量的控制和监测。

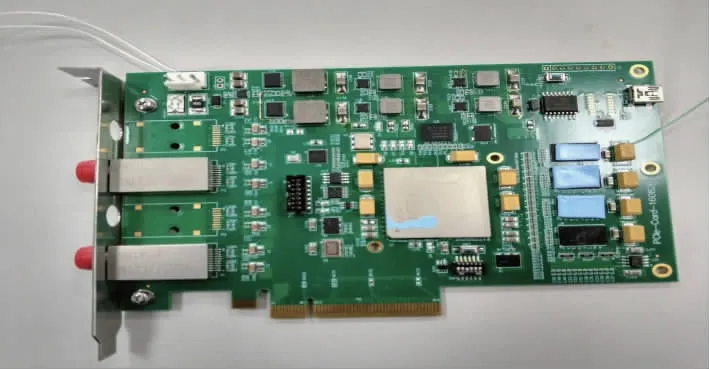

本系统能够以双工模块进行高速串行数据传输,保证传输的实时性。它主要包括PCI-e金手指、PCI Express模块、DDR3存储器控制模块、光纤传输模块以及外部的电源管理(见图2)。PCI Express模块支持PCI Express传输协议,并与其他模块交互,控制内部并行数据的转换,实现串行数据传输。DDR3存储模块用于与其他模块进行交互,缓存数据。

图1 硬件架构图

图2 实物图

3 系统设计

整个高速光纤传输系统设计的关键在于硬件逻辑设计、驱动层与应用层设计,整体架构如图3所示。

图3 整体系统架构图

3.1 PCI Express模块

为了减少开发时间,选用Xilinx官方提供的PCIe的IP核(架构如2-2),IP核允许使用数据包在其子模块间相互交换。在发送分层设备部分通过装配信息机制生成数据包。包中附带了数据传输通过的设备层所必需的信息。数据包通过链路传输在接收端被接收,接收设备层会对包中的必要信息进行拆解和读取,剥掉相应的字段,将待处理的包发往下一处理层,直到转换成能够被相应的核心设备和应用层读取和处理的信息。

链路选用4 lane(x4),理论速度可达到5 Gb/s(Gen2)。核例化以后的接口包括系统接口、PCI Express接口、传输接口、配置接口。系统接口主要提供系统复位和系统时钟信号。PCI Express接口主要用于数据传输,以多个差分队的形式组成。事务接口用于实现对TLP传输机制的控制。配置接口用于配置内部寄存器,保证PCI Express协议正常工作。

3.2 PCIe-DMA控制逻辑设计

PCI Express端点有PIO和DMA两种数据传输方式。本设计采用DMA传输方式直接读写内存。DMA 控制器主要有 TX_Engine、RX_Engine、DMA 控制/状态寄存器和中断控制器等部分。CPU会初始化DMA控制器(DMA通道、数据传输源地址、目的地址、传输字节数、传输模式),然后启动DMA传输。传输完成之后,DMA控制器会向CPU提出DMA中断,这时DMA再回应该中断,将目标地址中的数据取走。

图4 PCI Express内核结构

PCIe IP核支持MSI中断和传统的legacy中断(以读中断为例),当DMA中断处于空闲状态INT_IDIE,如果接收到RX_Engine发出的中断信号,则进行判断读写中断类型;如果读中断,进入读中断处理状态RDint_TYPE,该状态下告知PCIE核中断事件并根据中断模式选择转移状态RD_MSI_PRO或RDint_END,若是RD_MSI_PRO处理状态下,等待接收PCIe IP核的中断确认信号;进入读中断待结束状态RDint_end等待中断结束信号返回空闲状态INT_IDIE,再次等待下次中断的触发[4]。

3.3 DDR3逻辑设计

DDR3 SDRAM是易失性存储器件。在每次上电或复位后都要进行初始化才能实现存取操作。DDR3上电后等待200 ns,才能发出命令NOP或Deselect命令保持生效至少200 ns;预充电所有的命令;依次执行扩展模式寄存器2(EMR2)和扩展模式寄存器3(EMR3)命令;执行复位DLL模式寄存器进行命令设置,持续至少200个时钟周期才能锁定DLL;再次预充电所有的命令;执行两个自动刷新命令;执行模式寄存器进行命令设置,用于初始化器件操作[5]。选用4片MT41K128M16-15H,DDR3内核工作频率为200MHz,数据传输速率为800 MHz。DDR3逻辑控制发送命令给控制器,实现对DDR3 SDRAM进行读写数据访问相关操作(DDR3逻辑结构图如图6所示)。根据系统需求,此通道用于接收缓存大容量高速率的光纤数据,进而传输至主机。

图5 PCIe-DMA逻辑结构图

图6 DDR3逻辑结构图

3.4 Aurora IP逻辑设计

Aurora协议是由Xilinx公司开发,定义为串行数据传输的一个链路层协议,它具有高宽带以及可扩展性等特点[6]。此外,该协议的帧结构非常简单,打包效率很高。Aurora 64B/66B顶层模块例化了Aurora 64B/66B通道模块、TX和RX本地链路模块、全局逻辑模块以及GTP/GTX收发器。Aurora逻辑结构如图7所示。

3.5 驱动层与应用层设计

PCIe光纤接口程序可以划分为2个层次:一是用户驱动层,在Linux上使用内核API函数开发;二是应用面层,为用户设计的应用程序。

图7 Aurora逻辑结构图

驱动程序是控制PCIe板卡的底层程序,在Linux下使用C开发。驱动程序运行在系统内存的内核空间上,与应用程序的交互通过驱动提供的read、write以及ioctl等函数接口来完成[7]。

上位机应用程序实现用户操控和监控PCIe光纤接口卡的功能,程序一般用C或者C++在Linux系统上实现,本系统界面在Linux下采用QT开发,使用户获得所见即所得的直观感受。

操作系统通过驱动程序完成对光纤卡的初始化、读写、控制等操作。驱动程序首先被加载到内核并启动,由外部采集而来的数据通过光纤存放到DDR3内存并依序进入DMA缓存区,当板卡满足DMA中断条件时向CPU提出中断,此时等待获取数据的应用程序将通过驱动程序提供的接口函数read读取采集数据(图8)。

图8 驱动层和应用层读取程序流程图

4 测试结果

上位机通过发送大小为126697 Bytes的文件,经过PCIE接口传输到板卡,经由DDR3缓冲后传输到光纤接口,光纤口作回环处理,上位读取光纤口数据与原文件进行比对,并监测其传输速率。测试结果显示:传输速率达到4 Gbit/s,无丢包现象。上位机监控界面如图9所示,捕捉光纤口回环测试如图10所示。

图9 上位机监控界面

图10 光纤口回环测试结果

5 结论

本雷达数据传输系统采用高性能的FPGA芯片作为核心,利用FPGA内嵌的高速串口完成光纤传输,采用上位机实时控制和监控数据传输,该系统具有抗干扰性强、传输距离远、实时监控等特点。

[1]李攀,田泽,蔡叶芳,等.基于FPGA的双通道FC数据采集卡设计[J].计算机技术与发展,2013,23(7):179-182.

[2]黎小玉,田泽,王泉,等.基于SoC_FC芯片电源管理系统设计与实现[J].计算机技术与发展,2010,20(8):247-249.

[3]马萍,唐卫华,等.基于PCI Express总线高速数采卡的设计与现实[J].微计算机信息,2008(09).

[4]成立涛.基于FPGA的高速PCIe光纤接口卡设计与实现[D].哈尔滨:哈尔滨工业大学硕士学位论文,2015.

[5]王剑宇,苏颖.高速电路设计实践[M].北京:电子工业出版社,2014.

[6]侯春雷,唐碧华,等.基于PCI Express和Aurora协议高速光纤通信板卡的实现[J].微计算机应用,2010(1).

[7]刘仁峰.基于PCI总线的嵌入式设备驱动程序设计与研究[D].武汉:华中科技大学硕士学位论文,2004.