一种基于SRAM型FPGA的配置芯片设计

庄雪亚,李蕾蕾

(中国电子科技集团公司第五十八研究所,江苏无锡 214072)

1 引言

基于SRAM结构的FPGA,上电时要将配置数据读入到片内SRAM中,配置完成就可以进入工作状态。掉电后SRAM中的配置数据丢失,FPGA内部逻辑关系随之消失。正常使用SRAM型FPGA时必须配一个配置芯片用来存储配置数据,上电后FPGA能快速从配置芯片内加载到配置数据,使FPGA正常工作。随着设计工艺的飞速发展,FPGA规模也越做越大,配置容量也呈几何倍数增长,因而对配置芯片的配置便捷性、加载速度、存储容量提出了更高的要求[1]。本文基于SRAM型FPGA,设计一款改进型配置芯片,该芯片兼容传统的配置芯片。

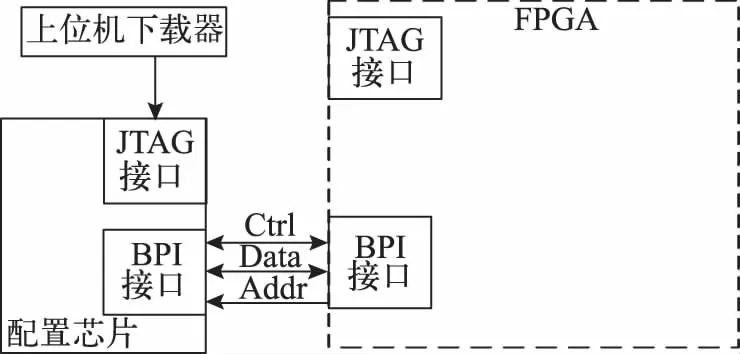

2 配置芯片下载方式

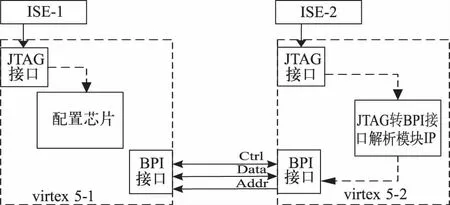

配置芯片都是与SRAM型FPGA搭载使用,一般一片SRAM型FPGA会搭载一片配置芯片或多片配置芯片级联使用。因此我们在对配置芯片加载数据时可以借助FPGA来完成。普通配置芯片下载方式[2]如图1所示,通过上位机软件建立FPGA工程、编译、布局布线后生成配置数据,连接JTAG下载至配置芯片,FPGA再通过BPI接口从配置芯片中加载配置数据。改进型配置芯片下载方式如图2所示,配置芯片去除了JTAG模块,通过例化一个JTAG转BPI的软核在FPGA内部实现。上位机可以通过连接FPGA的JTAG再通过软核转换为BPI格式的数据下载配置芯片,这样可以在不提供额外硬件资源的前提下,实现用JTAG接口对配置芯片的读写。上位机也可以通过BPI接口直接对配置芯片读写数据,BPI的数据总线为16位宽,数据传输量大,最高配置速度为800 Mb/s。配置芯片的下载方式决定了配置芯片的架构设计。

本设计的优点如下:

(1)不需要JTAG模块,省去配置芯片的大部分控制逻辑,减少流片风险;

(2)在不增加硬件资源的前提下,直接通过设计一个JTAG接口转BPI接口的软核,通过FPGA生成对应的电路,仍能保留JTAG下载及调试配置芯片的功能;

(3)兼容以往配置芯片的功能。

图1 普通配置芯片下载框图

图2 改进型配置芯片下载框图

3 设计与实现

3.1 配置芯片架构设计

如图3所示,配置芯片由初始化模块、JTAG接口模块、BPI命令解析模块、Flash读写模块、接口数据处理模块及Flash组成。上电后由内部时钟供给初始化模块,读取Flash的一些配置信息,保证每个Flash地址都可以正确读写。当初始化结束后,就可以根据JTAG接口或者BPI接口接收数据。JTAG接口模块是一种符合JTAG接口协议、能解析数据命令、下载、调试配置芯片的一个接口模块[3]。BPI接口数据处理模块通过BPI控制信号获得数据总线及地址总线上的数据。通过两个接口接收到的数据和地址由BPI命令解析模块解析具体对Flash的操作并传给Flash读写模块[4],能产生有效的读写时序对Flash进行读写。本文把图3中用虚线画的JTAG接口模块省去,把这部分逻辑改为用FPGA的软核实现。

图3 配置芯片架构

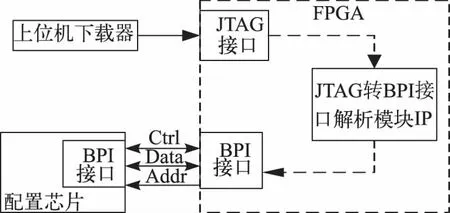

3.2 软核设计

如图4所示,软核设计思路是:开始TMS信号经过状态机解析当前TDI是数据还是命令,根据数据或者命令分别把TDI的数据存储到数据寄存器和指令寄存器;再进一步根据指令和数据解析成BPI对应的地址或者数据,还有BPI的控制信号线。当解析到是读数据命令或者读状态命令,可以根据BPI接口的DATA总线读到数据缓存器通过TDO输出。

图4 软核框图

3.3 配置命令定义

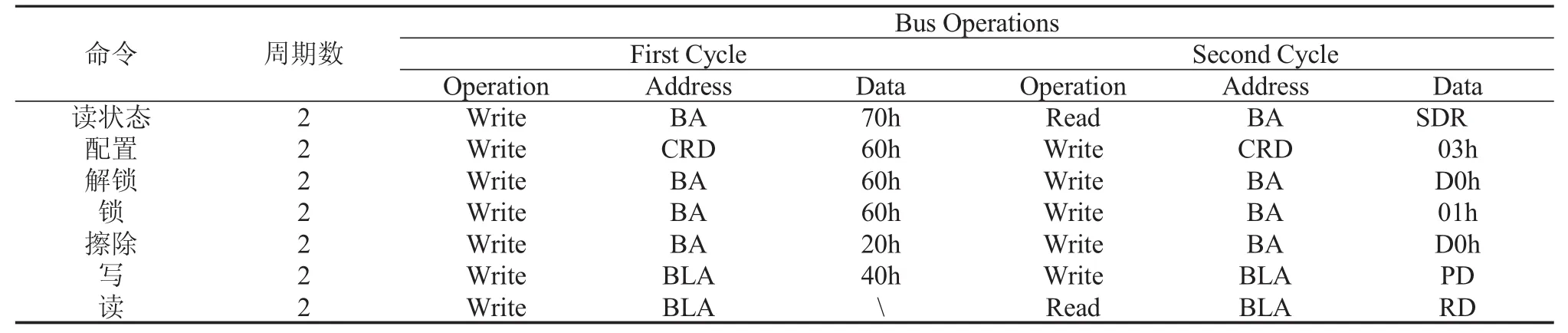

如表1所示,BA是指块地址,一个块地址包括1 Mbits;BLA是指一个单位的地址,一个地址存储16 bits;CRD是指配置数据;SDR是指返回的状态数据;PD是指写命令时每个地址对应写入的数据;RD是指读命令时读出的数据。每个命令都需两个有效周期完成,读命令不需要具体的命令值,只要BPI接口的FOE信号直接拉低就可以,这样做是为了方便FPGA上电完自动去加载配置芯片内的配置数据,省去发读命令的操作。

表1 配置芯片命令

3.4 擦除时序设计

如图5所示,第一个写周期数据总线发送20h命令,地址总线发送对应要擦除的区域地址,第二个写周期数据总线发送D0h命令,地址总线不变,当擦除完成后数据总线会返回一个80h的状态,如未擦除完成会返回00h的状态。

图5 擦除时序

3.5 写时序设计

如图6所示,第一个写周期数据总线发送40h命令,地址总线发送对应要写数据的地址,第二个写周期数据总线发送要写入的数据,地址总线不变,当写入完成后数据总线会返回一个80h的状态,如未写完成会返回00h的状态。

图6 写时序

3.6 读时序设计

如图7所示,第一个写周期FOE_B拉低,FEW_B为高,就说明是读命令,每一个地址都需立即返回一个该地址的数据。

图7 读时序

4 仿真验证

采用基于verilog行为级描述的RTL代码,建立整个仿真验证环境,利用Cadence公司仿真工具NC进行设计仿真验证[5],对配置芯片进行BPI接口数据仿真,对配置芯片接软核进行FPGA原型验证。

4.1 配置芯片加载FPGA EDA

如图8所示,通过配置芯片与FPGA对接,通过仿真波形看到done信号已经由低变高,说明配置芯片内的数据已经正确无误地加载到FPGA内。

图8 配置芯片加载FPGA时序

4.2 配置芯片原型验证

如图9所示,通过用两片xilinx virtex5 95T芯片来完成整个配置芯片的FPGA验证。先通过ISE-1软件把设计好的配置芯片工程load到Virtex5-1中,此时virtex-1就实现了配置芯片的功能,再通过ISE-2软件下载一个JTAG转BPI接口的软核给virtex5-2,再通过ISE-2建立一个工程,通过JTAG接口下载给virtex5-2,下载的数据通过转换后对virtex5-1进行写入配置数据,当把全部数据写完后,ISE-2对virtex5-2进行复位,放开对virtex5-2的控制权限,再重新上完电后,virtex5-2会自动从virtex5-1内加载配置数据,直到加载结束Done接的灯亮。Done信号变高代表配置数据已正确无误地下载到FPGA内,FPGA对应的工程可以正常启动。

图9 配置芯片FPGA验证框图

5 结论

本文基于SRAM型FPGA设计的配置芯片,设计结构简单,Flash容量大,通过BPI接口访问速度快,在不需要更多硬件资源的情况下能兼容以前版本的配置芯片。通过EDA验证和FPGA原型验证,结果符合预期。

[1]石雪梅,计贤春.FPGA配置芯片测试方法的研究与实现[J].计算机与数字工程,2010,38(09):77-79,87.

[2]刘笑嫘,何广平.FPGA芯片的配置与下载[J].科技信息,2011,(15):109-110.

[3]吕彩霞.JTAG的设计与研究[D].北京:北京交通大学,2006.

[4]潘立阳,朱钧.Flash存储器技术与发展[J].微电子学,2002(01).

[5](美)Rabaey,J M.数字集成电路-电路、系统与设计(第二版)[M].周润德,等译.北京:电子工业出版社,2004:319-357.