一种Mbist新型算法March 3CL的设计

陈之超,李小进,丁艳芳,李玲玲

(华东师范大学信息科学技术学院,上海,200241)

一种Mbist新型算法March 3CL的设计

陈之超,李小进,丁艳芳,李玲玲

(华东师范大学信息科学技术学院,上海,200241)

制造工艺的不断进步,嵌入式存储器在片上系统芯片中的集成度越来越大,同时存储器本身也变得愈加复杂,使得存储器出现了一系列新的故障类型,比如三单元耦合故障。存储器內建自测试技术是当今存储器测试的主流方法,研究高效率的Mbist算法,是提高芯片成品率的必要前提。以SRAM的7种三单元耦合故障为研究对象,通过分析故障行为得到三单元耦合的72种故障原语,并且分析了地址字内耦合故障的行为,进而提出新的测试算法March 3CL。以2048X32的SRAM为待测存储器,利用EDA工具进行了算法的仿真,仿真结果表明,该算法具有故障覆盖率高、时间复杂度低等优点。

SRAM;存储器內建自测试;三单元耦合故障;March算法;可测性设计

0 引言

随着深亚微米技术的不断发展,工艺尺寸不断缩小,存储器中各个单元之间的距离越来越近,出现了更为复杂的故障,如三单元耦合故障。存储器內建自测试是DFT(design for test)中重要的一项内容,目的是为了检测SOC(system on chip)中的嵌入式存储器是否存在故障。当下主流的Mbist设计工具是Mentor公司的Tessent Mbist,它可以检测到所有的单个单元故障、双单元故障和少部分三单元耦合故障[1],存在的缺陷是无法全面的覆盖三单元耦合障。当工艺达到28nm及以下时,这种三单元故障的影响会逐步加深,测试算法是存储器测试的核心内容[2],因此根据故障模型研究新的测试算法,以备更好地保证芯片的良率,成为行业所需。

1 三单元耦合故障分析

1.1 三单元耦合故障类型

当下的IC设计中,由于单端口静态存储器使用更为广泛,所以这里只针对它的三单元耦合故障进行研究分析。所谓耦合故障,就是两个或两个以上的存储单元之间存在紧密配合和相互影响,导致其中某几个单元的存储值发生改变从而使芯片产生故障的现象[3],而相邻单元出现耦合故障的概率比非相邻单元要大好几个数量级,所以这里只针对相邻的三个存储单元进行分析。

为了能够定义存储器的故障,功能故障模型以及故障原语被提出[4][5],故障原语的形式如下:=

根据不同的故障类型,可以把三单元故障分为7种[6],分别是:

(1)状态耦合故障(State coupling faults,CFst)

(2)扰动耦合故障(Disturb coupling faults,CFds)

(3)跳变耦合故障(Transition coupling faults,CFtr)

(4)写破坏耦合故障(Write Destructive coupling faults,CFwd)

(5)读破坏耦合故障(Read destructive coupling faults,CFrd)

(6)伪读破坏耦合故障(Deceptive read destructive coupling faults,CFdrd)

(7)不正确读耦合故障(Incorrect read coupling faults,CFir)

1.2 三单元耦合故障原语的建立

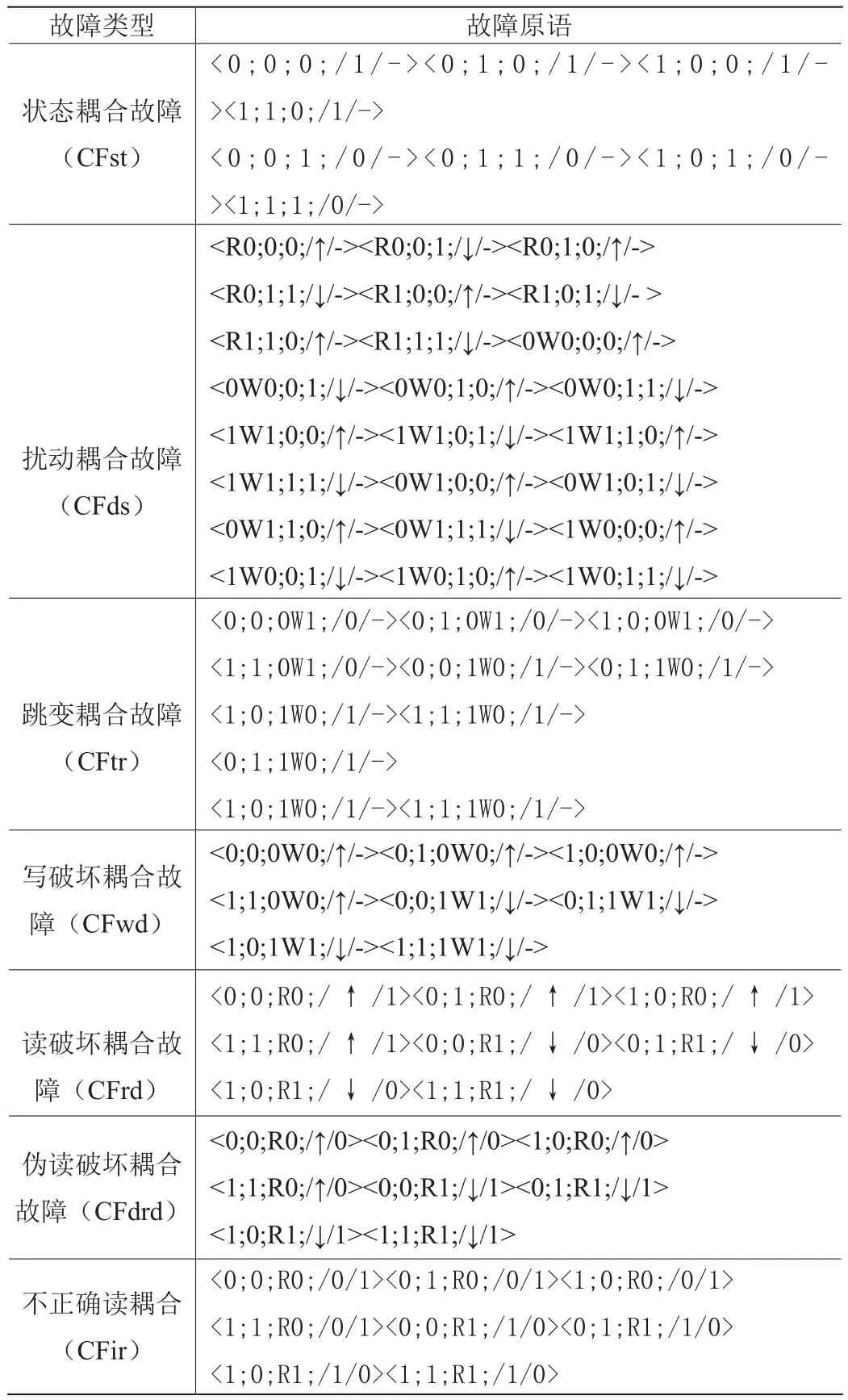

通过分析三单元耦合的各种故障行为,结合上文提到的8种敏化操作,得到三单元耦合故障的72种故障原语[7],如表1所示。

表1 三单元耦合故障原语

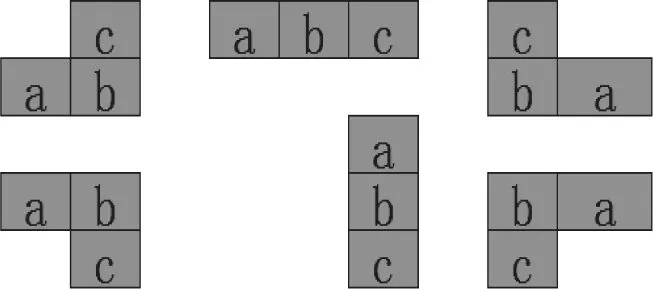

1.3 故障复杂性分析

表1列出了72种故障原语,从逻辑上对存储器中的故障进行了分类,由于这里的研究对象是三个单元,而三个单元中的任意两个都可以成为施主单元,剩下的一个作为受主单元,所以每种故障下又多了6种出现故障单元的方式。另外,考虑实际情况下相邻三个故障单元在存储器中的物理排布,会有如图1所示的6种不同排列形式。因此,综上所述,需要检测的三单元耦合故障共有2592个。

图1 相邻三单元排列方式图

对于这么多的故障而言,所设计的算法不仅要保持较高的故障覆盖率,还要保证较低的时间复杂度,所以最合适的方法是以March算法基于地址的测试思想来设计算法。

2 新型算法March 3CL的设计

2.1 算法背景初始化设计

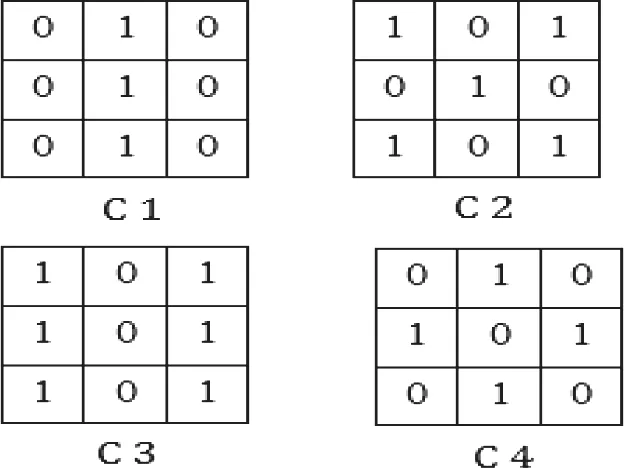

在对存储器进行测试之前需要对其存储单元的值初始化,这样做的目的是为了避免由于数据的偶然性而误导测试结果,从而保证测试的正确性。对存储器进行初始化,也就是对存储器写入逻辑值0或者1。三单元耦合故障算法的设计是针对存储器中的三个相邻的单元(a,b,c),每个单元上的逻辑值为0或1,因此这三个单元的逻辑组合有 8 种,分别是(0,0,0)、(0,0,1)、(0,1,1)、(1,0,0) 、(1,1,0)、 (1,1,1)、(0,1,0)、(1,0,1),前 6 种都可以由(0,0,0)经过一些写操作得到,(0,1,0)和(1,0,1)这两种故障组合,只能通过另外的背景初始化设计才能覆盖到。为了能够覆盖全部的逻辑组合,就有了下面的4种新的初始化背景设计C1—C4,如图2所示。

图2 背景初始状态排列图

初始化步骤C1、C3和C2、C4是两两互补的,配合后面的敏化操作,能全面覆盖三个单元的各种逻辑组合。

2.2 March 3CL算法设计

测试过程中,存储器是以地址为单位输入测试数据,默认的背景数据是“0”和“1”,因此每个地址上的位间只能形成00和11两种状态,同一地址内位间缺少01和10两种状态,所以无法覆盖同一地址内位间的耦合故障,这种形式称为字内故障[8]。为了让算法能够覆盖这种故障,我们增加测试数据类型“5”和“A”,通过增加形如“0101“和“1010”的测试数据,就可以覆盖字内故障。为了配合测试存储器,在工具中人为加入背景数据“5”和“A”,在字内即可形成“0101”和“1010”的二进制数据,从而覆盖字内故障。

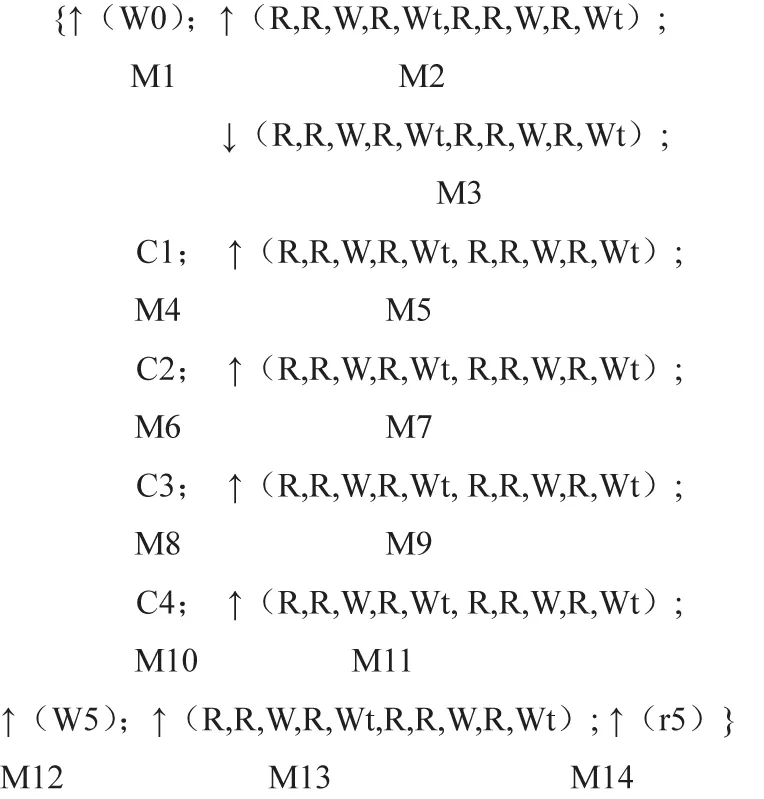

综上分析得到最终的March 3CL算法,如图3所示。

March 3CL算法设计过程中,为了使时间复杂度尽可能小,把一些观测步骤和敏化步骤整合到了一起,得到了最终的14个算法步骤。

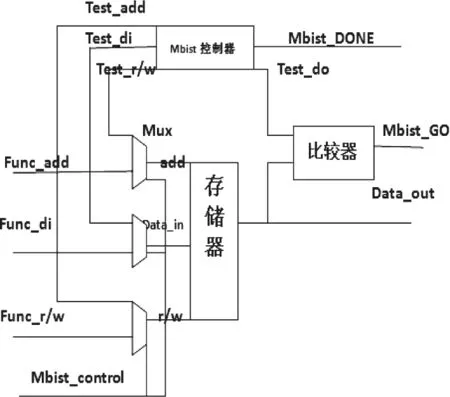

3 存储器內建自测试电路原理

存储器內建自测试就是在存储器周围建立测试电路,实现对存储器输入输出数据的控制,并把存储器的输出结果与期望值进行比较,若两者结果一致,则说明没有故障,若不一致,则表明存储器存在故障[9]。基本电路结构如图4所示,核心单元是MBIST控制器,由它控制电路进入相应的模式,当进入测试模式时,Function模式下的3个操作控制信号Func_r/w,Func_di,Func_add被切断,存储器的测试路径被接通,此时MBIST controler中产生的数据通过三个多路选择器Mux输入进Memory,从而直接控制存储器的读写操作。MBIST controler能够产生理想的输出结果Test_do,并将其输入进比较器Comparator,使其与存储器的实际输出数据进行比较,如果两者不一致,则故障标志位Mbist_GO信号会被拉高,说明存储器存在故障。整个过程完成后,信号MBIST_DONE会被拉高,表示存储器自测试完成,可以进入其他测试模式或功能模式。

图3 March 3CL算法步骤

图4 基本的Bist电路结构

4 算法仿真与验证

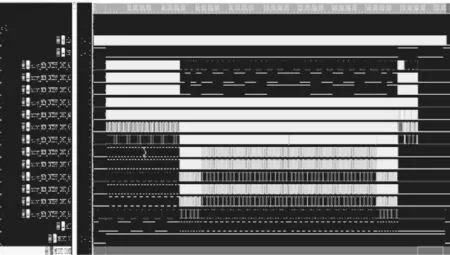

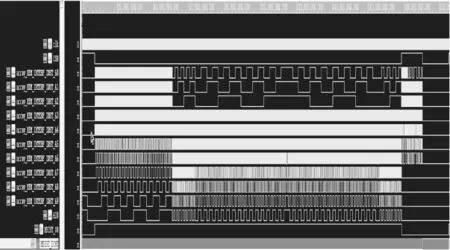

本文采用大小为2048X32的SRAM作为待测存储器,以March 3CL算法作为测试算法,采用Mentor公司的Tessent Mbist作为代码生成和插入工具,利用synopsys公司的VCS作为功能仿真工具,最后通过Novas公司的Verdi查看得到的波形图。按照工具提供的用户自定义算法模板来编写算法过程,得到最终的算法文件,并将其导入工具中。

图5说明了March 3CL算法的测试过程,该存储器共有11条地址线,最后两个信号MBIST_GO和MBIST_DONE是用来判断测试结果的。在整个算法测试阶段,由于使用的SRAM是理想的模型,图中倒数第二个信号MBIST_GO没有发生跳变,一直处在高电平,说明没有故障发生,最后一个信号MBIST_DONE在测试最后阶段跳变为高电平,标志着整个测试过程的结束。对于算法有效性的验证,这里采用的方法是在存储器库文件模型内人为注入故障,即在存储器RTL上直接改写其行为,产生符合要求的故障模型。由图6可以看出,在最后一个信号MBIST_DONE变为高电平之前,倒数第二个信号MBIST_GO跳变为低电平,说明算法检测到存储器存在故障。本文提到的72种三单元耦合故障以及字内耦合故障,都可以通过这种人为故障注入的方法来验证算法的有效性。

图5 无故障存储器算法仿真波形图

图6 检测到存储器故障仿真波形图

5 结语

嵌入式存储器的测试面临越来越多新的挑战,本文深入分析了三单元耦合以及字内耦合的各种故障行为,在此基础上设计了新型算法March 3CL,算法推导过程中在故障覆盖率和算法复杂度上进行了折中,最后利用EDA工具进行了仿真验证,结果证明该算法可以覆盖上述提到的所有故障,并且该算法具有较低的时间复杂度。

[1]R. Nair,S. Thatte,J. Abraham.Efficient algorithms fortesting semiconductorrandomaccessmemory[J].IEEE Trans.Comput.C-27(6)(1978)572-576.

[2]V.A.Vardanian,Y.Zorian.A March-based Fault Location Algorithm for Static Random Access Memories[C].Proceedingsof the 2002 IEEE International Workshop on Memory Technology,Design and Testing,2002:63-67.

[3]申志飞,梅春雷,易茂祥.基于MarchC +改进算法的MBIST设计 [J],电子科技,2011,24(10):67-70.

[4]Ad J. van de Goor,Issam B.S.A Systematic Method for Modifying March Tests for Bit-Oriented Memories into Tests for Word-Oriented Memories[J],IEEE TRANSACTIONS ON COMPUTERS,2003,52(10):1320-1331.

[5]Alfredo Benso,Alberto Bosio.March Test Generation Revealed[J],IEEE TRANSACTIONS ON COMPUTERS,2008,57(12):1704-1703.

[6]石磊,王小力.一种基于存储器故障原语的March测试算法的研究[J].微电子学,2009,39(2):251-255

[7]刘储元. ARMcortexM3芯片嵌入式存储器內建自测试算法的设计[D].南京:东南大学.2016.

[8]郭明朝.基于March算法的SRAM内建自测试设计与验证[D].西安:西安电子科技大学.2015.

[9]郭双友.嵌入式存储器测试算法的研究与实现[D]. 西安:西安电子科技大学.2009.

Design for a new Mbist algorithm March 3CL

Chen Zhichao, Li Xiaojin,Ding Yanfang, Li Lingling

(Department of Electrical Engineering, East China Normal University, Shanghai, 200241)

As the manufacturing process continues to advance,embeded memories have higher level of intergration on SOC,and at the same time the complexity of the memory itself make memories generate new fault types,such as 3-cell coupling faults.Memory build in self-test has been the main methods of memory test,so an effective algorithm is an essential prerequisite to the yield improvement.This paper points at seven categories of 3-cell coupling faults, we receive 72 kinds of fault primitive by analyzing the behavior of the 3-cell coupling fault,and we also analyze the faults in the same address,so a new test algorithmMarch 3CL is proposed.A 2048X32 SRAM has been used for verifying March 3CL by EDA tools,the result shows that this algorithm has the advantage of high fault coverage and short test time.

SRAM; Memory built-in self test(Mbist); 3-cell Coupling Faults; Algorithm March; Design For Test

陈之超,华东师范大学硕士研究生,主要研究方向为数字集成电路设计。