基于FPGA的LVDS转千兆以太网适配器的设计及应用*

张云毅,王 煜,常 振,邱晓晗,田禹泽,张 泉,林 方,王文誉,鲁月林

(1. 中国科学院安徽光学精密机械研究所,合肥 230031;2. 中国科学技术大学,合肥 230026)

基于FPGA的LVDS转千兆以太网适配器的设计及应用*

张云毅1,2,王 煜1*,常 振1,2,邱晓晗1,2,田禹泽1,2,张 泉1,2,林 方1,2,王文誉1,2,鲁月林1,2

(1. 中国科学院安徽光学精密机械研究所,合肥 230031;2. 中国科学技术大学,合肥 230026)

星载光谱仪的数据接口为LVDS接口,为快速地将其转换为地面民用设备,设计了LVDS转千兆以太网适配器。适配器采用FPGA为主控芯片,接收光谱仪发送的串行的图像数据,并将其封装为以太网帧格式,然后通过网口芯片传输给上位机;同时适配器接收上位机发送的命令数据,并转发给光谱仪。实验结果表明,适配器在传输速率为43 Mbit/s时,连续运行48 h,误码率为0,在实验室条件和自然条件下均能稳定传输数据,可作为光谱仪的转换接口。

电子学;数据传输;FPGA;LVDS(Low Voltage Differential Signalling);Gigabit Ethernet;UDP

成像光谱仪是同时采集图像信息和图像中各点光谱信息的设备,多用于大气探测、地质选矿、航空测绘等领域。同时在工业排放检测、发动机尾焰分析等工业领域以及实验室的科研设备中也有应用。

在航空航天领域,成像光谱仪作为星载和机载设备,将图像数据输出给卫星平台和飞机数据存储平台[1]。目前通行的标准是低电压差分信号LVDS(Low-Voltage Differential Signaling)同步串行数据总线。在民用领域,光谱仪通常连接上位机,其常用的连接方式为采集卡、USB和以太网。

本课题所属课题组长期以来从事成像光谱仪成像电路的研制,已形成多种星载和机载光谱仪产品。针对目前工业领域和科研仪器的需求,计划在已有航空航天产品的基础上研制成像光谱仪的民用检测设备和科研设备。在民用领域的3种连接方式中,采集卡和USB的传输距离相对较短,适用于实验室环境,而在工业现场环境中多采用以太网线连接方式,为此设计了LVDS转千兆以太网适配器。

1 系统概况

1.1 性能指标

项目中用到的CCD成像电路传输数据的速率为43 Mbit/s~172 Mbit/s,所以适配器的数据传输速率应大于172 Mbit/s,因此采用千兆以太网。

由于成像电路的数据传输连续且速率固定,当传输协议采用传输控制协议TCP(Transmission Control Protocol)时,若传输过程中丢失数据包,该协议要求重发丢失的数据包,这时需要在适配器中开辟很大的缓冲区,也会导致传输时间不可控,且TCP协议的开销很大,也会降低有效的数据传输速率[2]。当采用用户数据报协议UDP(User Datagram Protocol)时,虽然有可能丢失数据包[3],但适配器的应用场合是点对点传输,电缆连接和电磁环境固定不变,误码可控,即使图像数据出现数据错误的现象,数据包也有校验功能,将对应的数据包舍弃,并不影响测量结果,因此本设计采用UDP协议。

1.2 整体设计

系统整体如图1所示。

图1 系统整体结构图

适配器接收成像电路发送的串行LVDS数据,经数据缓冲、UDP/IP协议封装后送入介质访问控制MAC(Media Access Control)芯片,此时MAC芯片会将IP数据包按MAC帧格式送入物理层PHY(PHYsical layer)芯片,经以太网口输出到上位机。同时上位机发送曝光时间、工作模式等控制命令,该命令由MAC芯片接收后送入现场可编程门阵列FPGA(Field-Programmable Gate Array),FPGA将其解码并通过通用异步收发传输器UART(Universal Asynchronous Receiver/Transmitter)模块转为异步串行数据经RS-422总线发送给成像电路。除此之外,成像电路将CCD的工作温度等状态信息也通过RS-422总线发送给适配器,适配器将其转换为UDP数据包发送给上位机。

2 硬件电路设计

2.1 方案设计

方案设计中有3种方案可供选择,如表1所示。

表1 方案描述

综合考虑性能要求、研发成本和研发周期等因素,FPGA+MAC+PHY的方案既能实现大于172 Mbit/s的传输速率,又能满足研发成本低和研发周期短的要求,因此本设计采用该方案。

2.2 芯片选型

适配器通过Xilinx公司生产的FPGA驱动MAC芯片和PHY芯片实现数据传输功能。FPGA为Spartan3系列的XC3S400-208,它有40万系统门,288 kbit的Block RAM,264个I/O口,116对差分信号I/O口[7],可以满足系统设计需求。

MAC层芯片为亚信电子的AX88180,该芯片为类SRAM接口,有16位和32位两种工作模式,支持10/100/1000 Mbit/s 3种速率,嵌入了32 kbyte的接收缓冲区和8 kbyte的发送缓冲区,支持TCP/UDP/IP功能,并能计算校验和,可以为FPGA减负[8]。

PHY芯片为Realtek公司生产的RTL8211E-VB-CG,支持10/100/1 000 Mbit/s 3种速率,具有自动协商功能与交叉检测和自动校正功能,与MAC芯片通过RGMII接口通信[9]。

3 硬件逻辑设计

硬件逻辑由Verilog语言编写,共分为3个模块:图像数据接收模块、UDP/IP模块及UART模块。

3.1 图像数据接收模块

图像数据接收模块分为串并转换模块和数据缓冲模块两部分。串并转换模块将串行的LVDS图像数据转换为16 bit的并行数据,然后存入数据缓冲模块。

LVDS即低电压差分信号,是美国国家半导体公司在1994年提出的一种信号传输模式。LVDS是一种电平标准,这种技术的核心是采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接。LVDS技术用于简单的线路驱动器和接收器物理层器件[10]。

光谱仪的LVDS总线是一种同步串行总线,由3个信号,6根线(3组差分线对)构成。类似串行外设接口SPI(Serial Peripheral Interface)总线,但是是单向传输[11]。

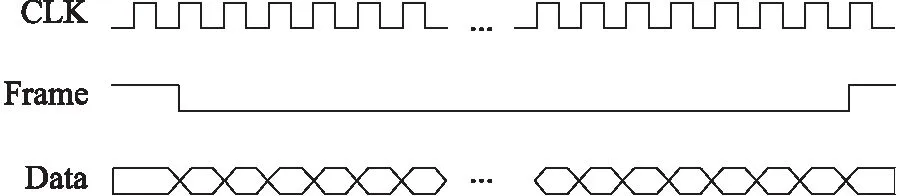

该模块接收数据的时序图如图2所示。

图2 数据接收时序图

图像数据接收模块在Frame信号为低电平时,每个CLK的上升沿读取一位数据。由于每个图像的像元为16 bit,因此每读满16 bit数据便存入数据缓冲模块。

考虑到LVDS信号的传输速率为43 MHz,而适配器系统时钟为50 MHz,所以设计了一个数据缓冲模块来负责信号跨时钟域的传输。数据缓冲模块由两个双端口RAM组成,写端口位宽为16 bit,读端口位宽为32 bit,采用乒乓缓存策略,当一个RAM写满之后才发送读使能信号,此时新接收的数据存入另一个RAM。由于读操作的速率和位宽都大于写操作,所以并不会出现RAM还没读完就有新数据写入的情况,这样就避免了对一块存储区域的同时读写,从而避免异步时序中冲突等问题。

3.2 UDP/IP模块

UDP/IP模块是适配器的核心部分,考虑到该模块既要完成与其他模块以及MAC芯片通讯的硬件接口功能,又要完成初始化MAC芯片、地址解析协议ARP(Address Resolution Protocol)协商、协议包的封装与解析等逻辑功能,并且这些逻辑功能又依赖于上述的硬件接口功能,因此引入了级层的概念,即上级的功能通过调用下级来实现,使其逻辑更清晰、代码更简洁。该模块分为3个级层,分别为端口级、功能级和状态级。各级之间的关系如图3所示。

图3 UDP/IP模块层次图

3.2.1 端口级

端口级实现的是与MAC芯片通信、与UART模块通信的功能以及从数据缓冲模块中读取数据的功能,这些功能实现较为简单,重点是需要满足读写时序的要求。为了便于上层模块的调用,端口级均用Verilog语言中的task来实现设计复用。

3.2.2 功能级

功能级通过调用端口级,完成了芯片初始化、功能配置、ARP协商、数据接收和发送等功能。芯片初始化的内容主要包括复位芯片、等待复位完成和设置MAC地址。功能配置包括配置PHY芯片工作模式、等待自动协商完成、配置MAC芯片工作模式、使能RX/TX功能以及开中断。ARP协商用于建立适配器与上位机的通信链路,数据接收与发送用于传输图像数据与控制信息。

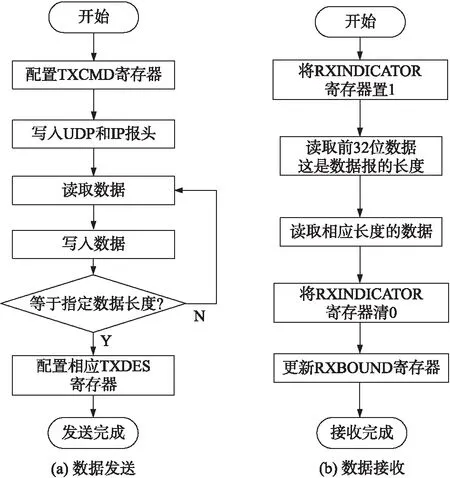

数据发送和接收流程如图4所示。

图4 数据发送与接收流程

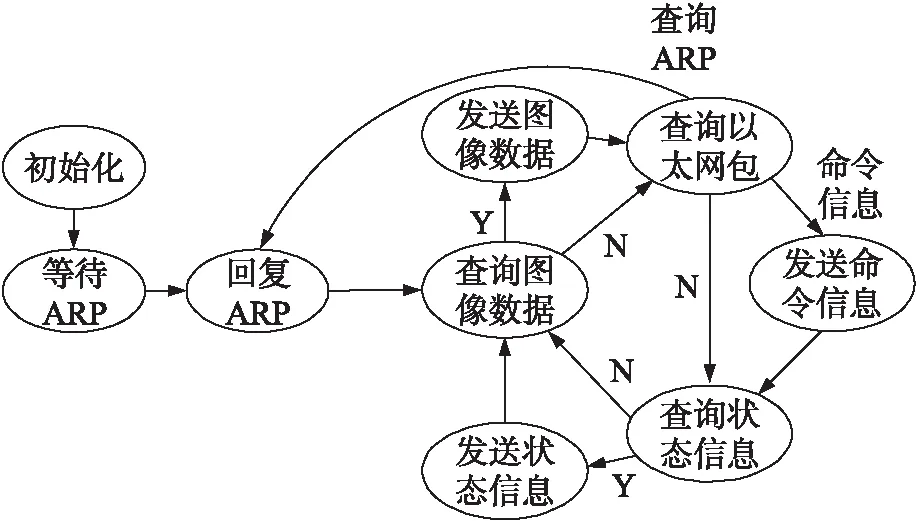

3.2.3 状态级

状态级由一个状态机负责UDP/IP模块的整体调度。FPGA首先进入初始化状态完成对MAC芯片和PHY芯片的初始化及功能配置,之后FPGA进入等待ARP状态。当接收到来自上位机的ARP查询包时,FPGA将保存上位机的IP地址和MAC地址,然后进入回复ARP状态,将自己的IP地址和MAC地址通过一个ARP回复包发送给上位机。至此,适配器与上位机的通信链路已经连接成功,可以开始传输数据。

在数据传输过程中,FPGA首先进入图像数据查询状态,若没有发现图像数据则直接进入以太网包查询状态;若发现有图像数据,便进入图像数据发送状态,将图像数据从数据缓冲模块中读出并通过网口发送至上位机,当数据发送完成后再进入以太网包查询状态。

进入以太网包查询状态后,FPGA询问MAC芯片是否有来自上位机的以太网包,当有以太网包时,需要判断包类型,若包类型为命令包,则进入发送命令状态,在该状态中,程序从MAC芯片中读出数据包,然后解析出数据包中的有效数据,并将其发送给UART模块,之后FPGA跳转至状态信息查询状态;若包类型为查询ARP包,则进入回复ARP状态并发送ARP回复包,重新开始传输数据。当没有以太网包或包类型为其他类型的数据包时,则直接跳转至状态信息查询状态。

进入状态信息查询状态后,程序询问UART模块是否有来自成像电路的状态信息,若有,则从UART模块读出状态信息,封装成UDP数据包后发送给上位机;若没有,则返回图像数据查询状态。

图5 UDP/IP模块状态机示意图

之后不断重复上述过程。该过程状态机示意图如图5所示。

3.3 UART模块

适配器除了要完成图像数据的传输,还要转发上位机对成像电路的命令信息和成像电路反馈的状态信息。这部分功能由UART模块实现。

UART模块采用RS-422接口与成像电路通信,通信波特率为115 200 bit/s[12]。该模块分为接收和发送两部分,其中接收部分接收状态信息,接收完成后向UDP/IP模块发送传输数据请求,当UDP/IP模块进入状态信息查询状态后,请求被响应,此时状态信息从UART模块进入UDP/IP模块并被发送给上位机。

发送部分等待UDP/IP模块的发送请求,响应请求之后,将命令信息从UDP/IP模块中读出,并以串行的方式通过RS-422接口发送给CCD成像电路。

4 产品设计

硬件逻辑设计综合后在Spartan3系列,型号为XC3S400-208的FPGA中的资源占用情况如表2所示。

表2 资源占用情况

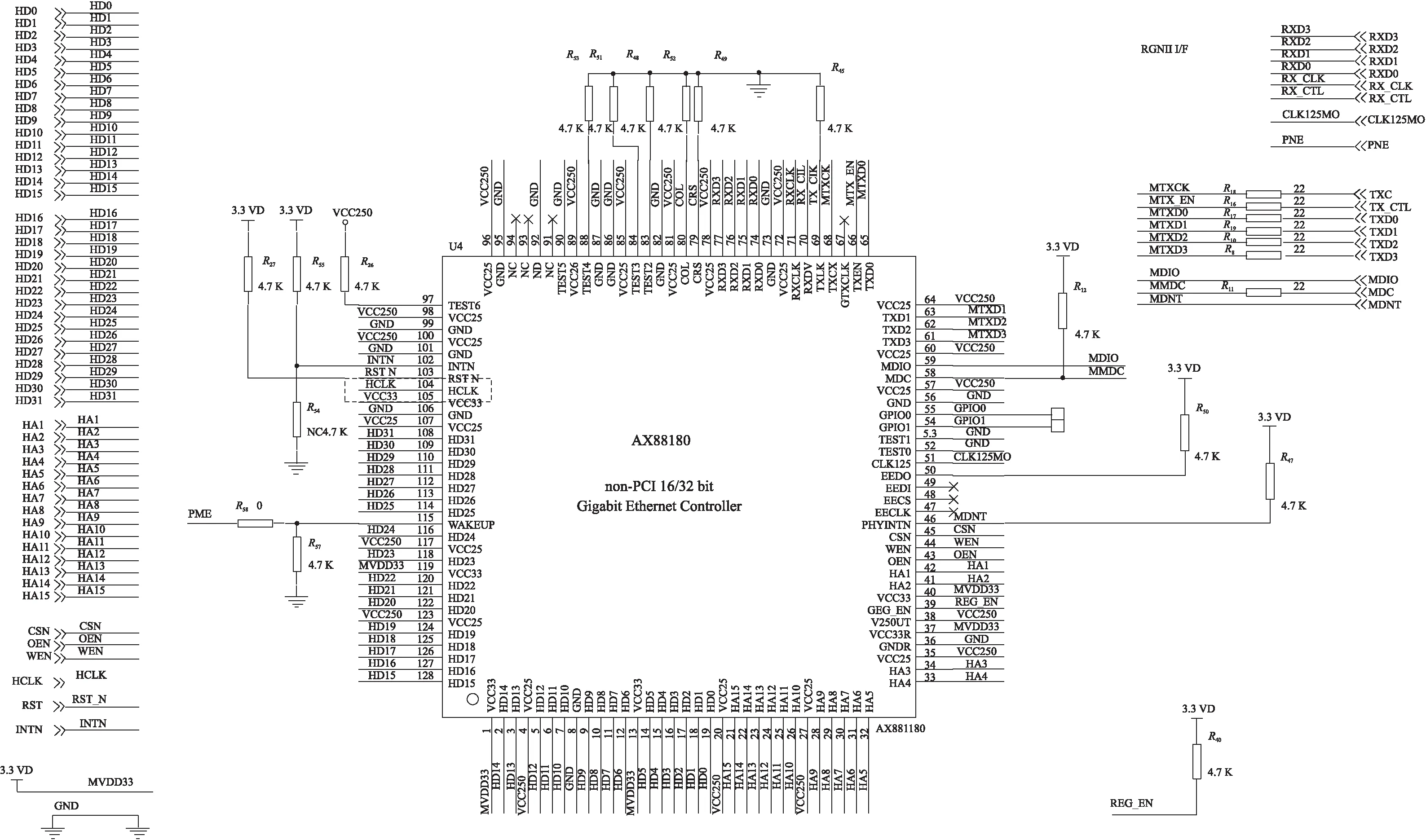

硬件电路设计为单板4层结构,其中MAC芯片原理图如图6所示。

图6 MAC芯片原理图

图6中,AX88180为MAC芯片,该芯片通过图左侧的离页连接符与FPGA通信,包括数据总线HD31~HD0、地址总线HA15~HA1以及6根控制总线;与PHY芯片通过图右侧的离页连接符相连,包括RGMII接口和PHY芯片寄存器访问接口。

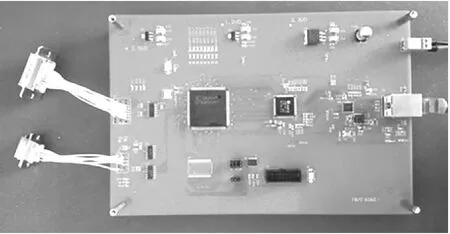

电路板实物如图7所示。

图7 电路板实物图

图中左上的接口为LVDS接口,左下的接口为RS-422接口,电路板中间从左往右依次是FPGA、MAC芯片和PHY芯片,接口为RJ45网口。

此外还编写了上位机软件,实现了图像数据的接收和显示,以及发送控制命令、显示状态信息、计算传输速率和误码率检测等功能。

5 测试结果

测试分为实验室测试和外场测试两部分。

在实验室测试中,测试系统由CCD相机、成像电路、LVDS转千兆以太网适配器和上位机组成。测试结果显示,在千兆以太网工作模式下,适配器的传输速率最高可达300 Mbit/s。当传输速度为43 Mbit/s,使用长度为50 m的超五类网线时,连续运行48 h,误码率为0。

外场测试在合肥某电厂附近进行,如图8(a)所示:测试系统由光谱仪、水平转台、成像电路、LVDS转千兆以太网适配器以及笔记本电脑组成。采用380 nm~500 nm波段的光谱仪对该电厂的废气排放情况进行观测,笔记本电脑控制光谱仪的工作状态,并实时显示光谱仪所观测区域的图像。图8(b)为440 nm波长对应的观测区域灰度图。测试结果表明,适配器在自然条件下可以稳定的传输数据,同时完成控制命令的接收与发送。

图8 外场测试及观测结果

6 结论

设计的适配器实现了将LVDS图像数据转换为以太网包传输的功能。该适配器可以将星载光谱仪连接至上位机形成地面民用设备,并且将短距离传输的LVDS转换为长距离传输的以太网,使光谱仪与上位机可以分开放置,即将光谱仪放在工业现场进行测量,而上位机放在设备间实时成像,使光谱仪成像系统更具灵活性。在LVDS转千兆以太网适配器的基础上,也可以方便地设计出其他通讯协议与以太网之间的转换模块,为军工科研成果向民用推广提供便捷。

[1] 王煜,陆亦怀,赵欣,等. 星载差分吸收光谱仪CCD成像电路的设计及实施[J]. 激光与红外,2015,45(6):663-668.

[2] 韩志峰,宋执环. 基于嵌入式网络的数据采集与分布式计算系统[J]. 传感技术学报,2006,19(3):885-889.

[3] Behrouz A Forouzan. TCP/IP协议族[M]. 第3版. 北京:清华大学出版社,2009:147-162.

[4] 赵志刚,郭金川,杜杨,等. COMS图像传感器LUPA-4000具有开窗读出功能成像系统的实现[J]. 传感技术学报,2010,23(5):670-675.

[5] 瞿鑫. 基于FPGA的嵌入式千兆以太网相机传输系统的设计[D]. 四川:电子科技大学,2014.

[6] 蒋沪生,柴志雷,钟传杰. FPGA中网络通信协议栈的裁剪及其全硬件实现[J]. 计算机工程与设计,2013,34(9):3074-3077,3083.

[7] Xilinx Inc. DS099 Spartan-3 FPGA Family:Complete Data Sheet[DB/OL]. [2004-08-24]. http://www.xilinx.com/support/documentation/data_sheets/ds099.pdf.

[8] ASIX Inc. High-Performance Non-PCI 32-bit 10/100/1 000M Gigabit Ethernet Controller[DB/OL]. [2014-06-23]. http://www.asix.com.tw/download.php?sub=briefdetail&PItemID=88.

[9] Realtek Inc. Integrated 10/100/1000M Ethernet Transceiver[DB/OL]. [2012-04-03]. http://www.realtek.com/downloads/.

[10] IEEE Project 1596.3 Working Group. IEEE Standard for Low-Voltage Differential Signals(LVDS)for Scalable Coherent Interface(SCI)[S]. IEEE Std 1596.3-1996,1996.

[11] Chang Zhen,Wang Yu,Li Sheng,et al. LVDS-USB-Adapter Applied to Spectrometers[J]. Light,Energy and the Environment,OSA Technical Digest(Online)(Optical Society of America,2014),paper JW6A.9.

[12] 刘伟,王红亮,张亮红,等. 基于FPGA的以太网-RS422转换器设计[J]. 自动化与仪表,2015(9):84-88.

DesignandApplicationofanLVDStoGigabitEthernetAdapterBasedonFPGA*

ZHANGYunyi1,2,WANGYu1*,CHANGZhen1,2,QIUXiaohan1,2,TIANYuze1,2,ZHANGQuan1,2,LINFang1,2,WANGWenyu1,2,LUYuelin1,2

(1.Anhui Institute of Optics and Fine Mechanics,Chinese Academy of Sciences,Hefei 230031,China;2.University of Science and Technology of China,Hefei 230026,China)

Satellite-borne spectrometers use LVDS interface,in order to transform them into industrial equipments,a LVDS to Gigabit Ethernet adapter was designed. The adapter uses FPGA as its main control chip,it receives serial image data sending from spectrometers,and encapsulates them into Ethernet frame formet,then transmits them to upper monitor through Ethernet chips;at the same time,the adapter receives commands from the upper monitor,and transmits them to the spectrometer. The test result shows that after running 48 hours at the rate of 43 Mbit/s,the bit error ratio of the adapter is 0,it can can transmit data steadily in both laboratory condition and natural condition,and can be used for interface conversion for spectrometers.

electronics;data transmission;FPGA;LVDS(Low Voltage Differential Signalling);Gigabit Ethernet;UDP

10.3969/j.issn.1005-9490.2017.06.028

项目来源:国家自然科学基金项目(41275037);安徽省自然科学基金项目(1408085MKL49)

2016-10-18修改日期2016-11-23

TP274

A

1005-9490(2017)06-1472-06

张云毅(1993-),男,汉族,河南辉县人,中国科学技术大学硕士研究生,主要研究方向光电子技术,数据通信技术,yyzhang@aiofm.ac.cn;

王煜(1971-),男,汉族,北京人,合肥物质科学研究院安徽光学精密机械研究所研究员,主要研究方向为CCD成像技术、光电子技术,yuwang@aiofm.ac.cn。