基于PCI-e和PCI-x总线的XMC/PMC载板设计*

胡彦君,高 枫,姜 威,张会新,张春恒,刘文怡*

(1.中北大学电子测试技术国家重点实验室,太原 030051;2.北京宇航系统工程研究所,北京 100076)

基于PCI-e和PCI-x总线的XMC/PMC载板设计*

胡彦君1,高 枫2,姜 威2,张会新1,张春恒1,刘文怡1*

(1.中北大学电子测试技术国家重点实验室,太原 030051;2.北京宇航系统工程研究所,北京 100076)

为了灵活地实现VPX系统中功能的扩展,设计了一种采用PCI-e总线和PCI-x总线的XMC/PMC功能载板。该载板通过P1-P6连接器与不同功能板卡连接,由HD68接口实现外界与载板之间数据通信,并介绍了以PCI-e开关模块和PCI-e转PCI-x模块为主的系统方案。对其中的转换模块、开关模块、存储模块、电源模块和时钟模块进行了详细介绍。在电路设计过程中,通过仿真保证高速电路的信号完整性。最后通过与AD板卡进行调试,验证了XMC/PMC设计可行性。

电路设计;PCI-e;PCI-x;XNC/PMC;信号完整性

VPX技术采用高速串行总线代替并行总线,最高数据传输率可以达到10 Gbit/s,通过RapidIO和Advanced Switching Interconnect现代工业串行交换结构,实现更高的背板宽度,支持PCI-e,SRIO等工业串行接口[1]。

在VPX系统中,XMC/PMC载板为通用模块,主要实现不同接口功能。不同功能的板卡都可以与载板组合,这样既能节约成本,也方便快捷,因此设计载板具有很大的意义[2]。

此载板与VPX背板之间通过PCI-e总线进行连接,从VPX背板的P1口引出两通道X4宽度的总线接口,一通道接到XMC接口上,另一通道通过PCI-x总线接到PMC接口上,进而完成载板设计。本文介绍了基于PCI-e和PCI-x总线的载板设计实现方法,并且通过信号完整性仿真实验,使设计变得更完整[3]。

1 总体设计方案

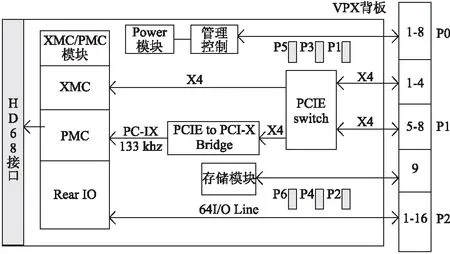

设计的XMC/PMC载板适用3U大小的机箱。载板的上行接口连接到VPX背板部分,下行接口分别通过PCI-e与PCI-x连接到XMC/PMC端口,详细的系统框图如图1所示。

图1 载板系统框图

VPX背板包括3部分接口,分别为P0,P1,P2。其中P0口实现电源功能,给载板供电;由于载板设计的标准为XMC模块支持4路(X4)PCI-e互联总线,PMC支持4路(X4)PCI-X总线,因此将P1口进行功能划分,连接片1~4采用PCI-e作为互连总线,连接背板与载板之间的数据信号,同时将信号与XMC相连,与外部进行输出控制,连接片5~8连接PCI-e转换PCI-X转换芯片,将转换生成的PCI-X总线连接到PMC模块,第9连接片实现存储功能。

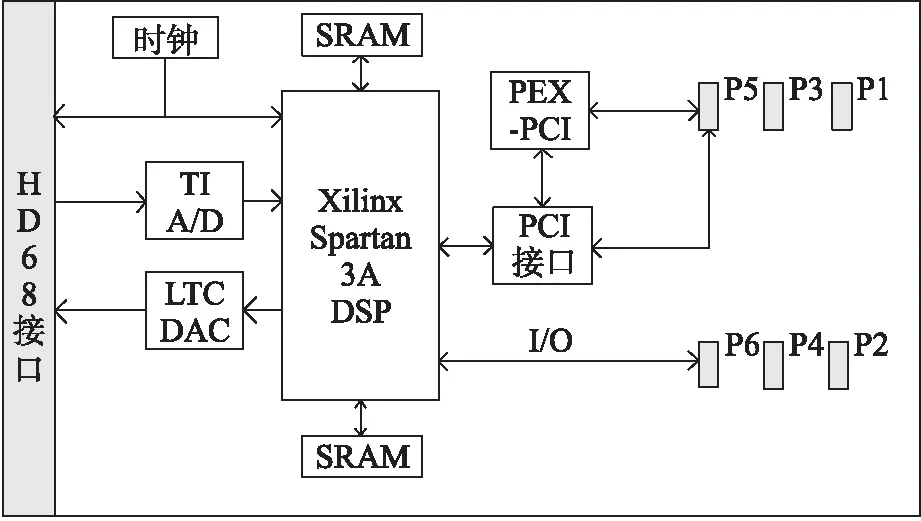

本载板可以通过连接器(P1-P6)负载功能板卡,为了后期测试载板的性能,记录了负载AD板卡的输出波形。其中连接器P5,P6实现与AD板卡之间的通讯。P5,P6连接器点的信号包括时钟、触发、16 bit ADC、DAC和GND信号。AD板的系统框图如图2所示。

图2 AD板卡系统框图

2 硬件设计

XMC/PMC载板作为功能板卡的承载,一方面要性能稳定,另一方面还必须实现板卡的功能[4]。由图1系统框图可以看出,设计主要包括PCI-e开关模块、PCI-e转PCI-x模块、存储模块、电源管理和时钟模块。下面将对这些模块进行具体的介绍。

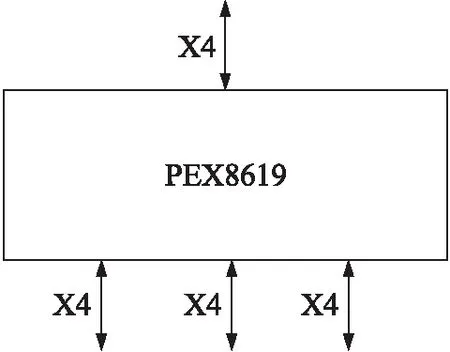

图3 PEX8619配置方式

2.1 PCI-e开关模块

PCI-e开关芯片选择的标准在于端口和信道。当前使用的端口为4个,信号需求为16个。可以选择PLX公司的4端口芯片PEX8619,它是专门用于PCI-e端口扩展的芯片,包含16 bit配置端口,配置方式有多种,这里选用的是4路X4的配置方式[5]。配置方式如图3所示。

每个PCI-e端口包括两部分信号—通讯信号和控制信号。通讯信号主要有Lane信道组成,而且每个Lane信道都包含一对差分对,控制信号包括时钟信号,电源信号等。PCI-e开关模块分别连接着VPX背板和XMC模块。

2.2 PCI-e转PCI-x模块

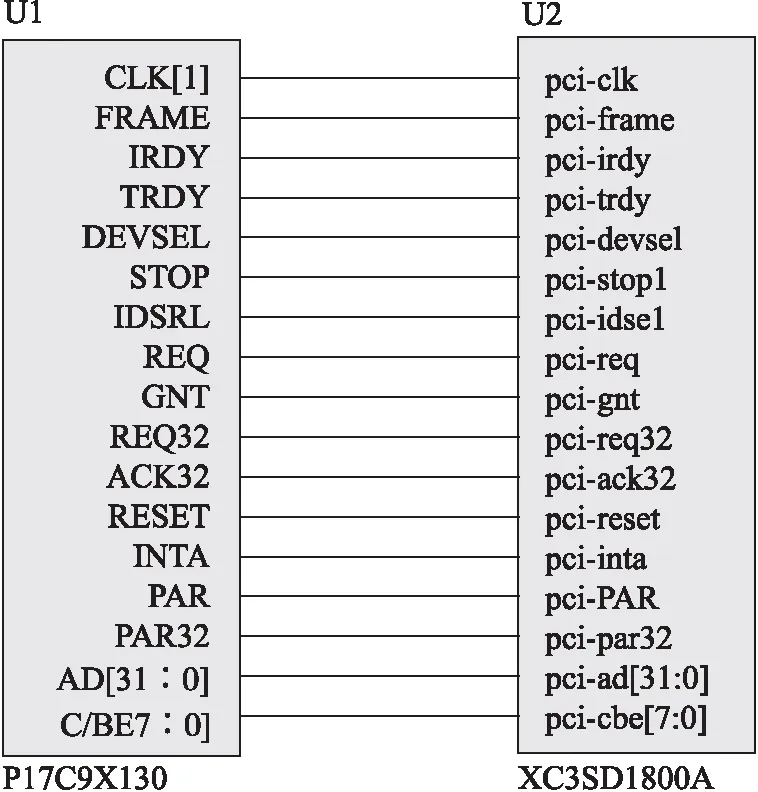

PCI-e转PCI-x芯片选用Pericom公司的P17C9X130,该芯片不仅兼容PCI-e 1.1版本规范,支持PCI-e总线X4端口,而且能够实现PCI-e和PCI-x端口之间的相互转化[6]。设计需要PCI-e总线经由芯片产生PCI-x,133 MHz的总线接口,进而通过PMC连接口将数据传输出去。转换芯片和AD板FPGA间的信号连接框图如图4所示。

图4 信号连接图

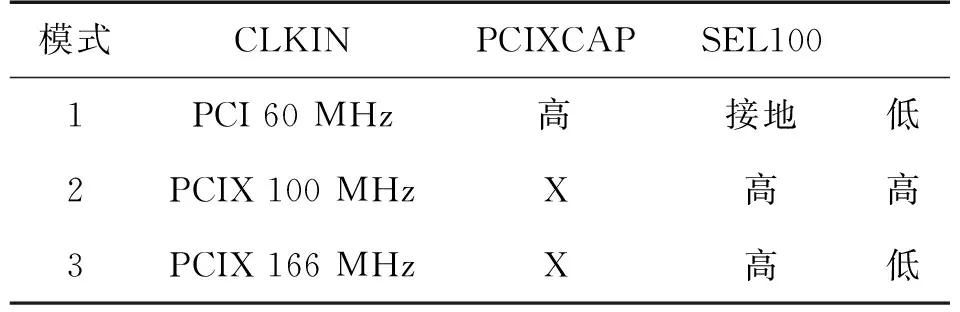

图4中,AD[31:0]是PCI总线32 bit双向数据、地址信号,C/BE[7:0]为使能信号。P17C9X130能够通过内部锁相环将PCI-e差分时钟生成7个时钟信号,驱动外围设备。P17C9X130通过3个控制信号产生3种工作模式,具体如表1所示。根据需求选用模式3-PCI-x,133 MHz的总线。

表1 P17C9X130工作模式

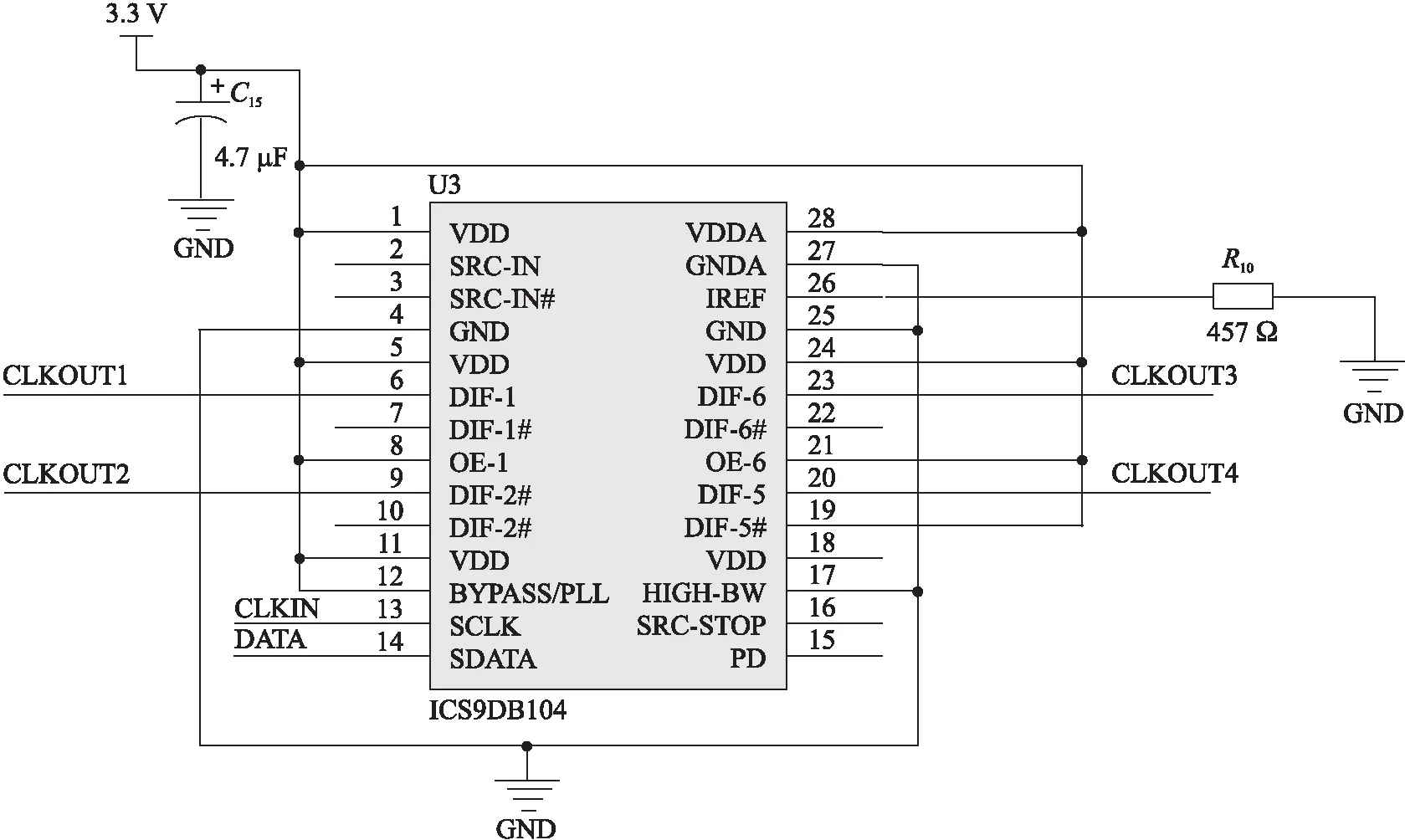

2.3 时钟模块

时钟的相位噪声和激励都能够直接耦合到输出,影响输出结果。因此时钟也是必须考虑的影响因素。时钟芯片选择ICS公司的ICS9DB104BF,它可以将一路时钟扩展为4路输出,分别给VPX背板、交换器芯片、PCI-e转PCI-x转换芯片和XMC/PMC提供时钟。具体如图5所示。

图5 时钟电路图

2.4 电源模块

由于本载板没有对噪声敏感的音频,射频模拟电路,所以只能采用DC-DC电路来减少功耗[7]。

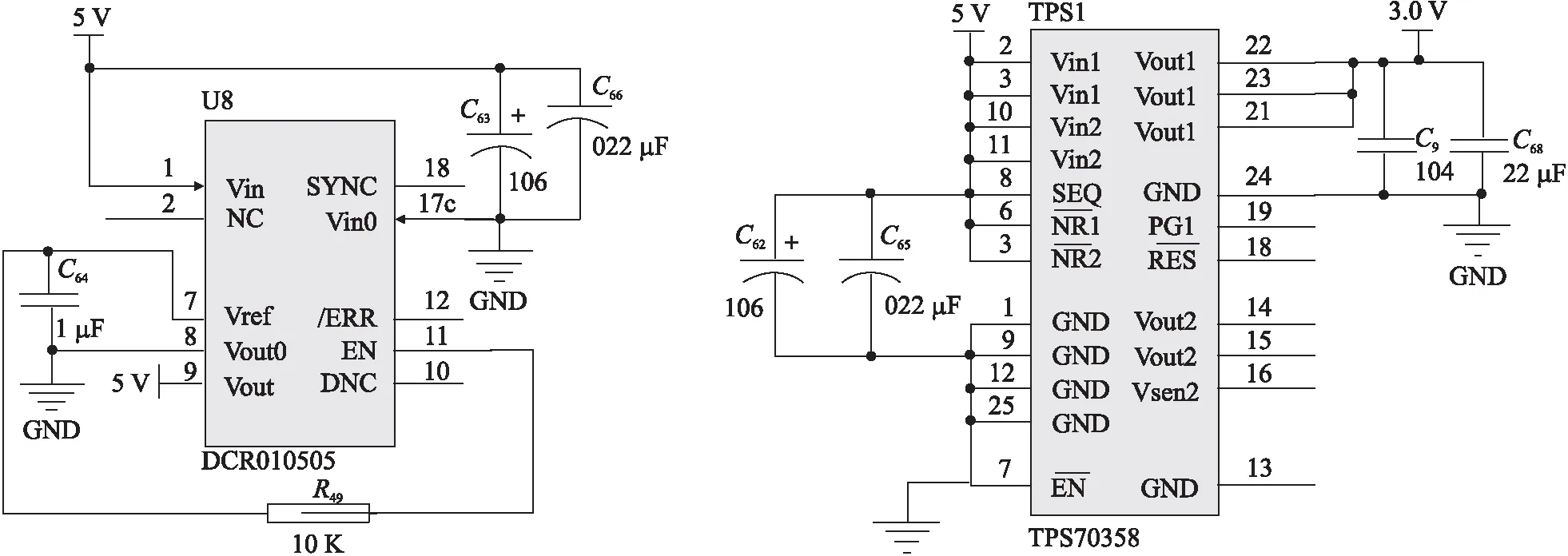

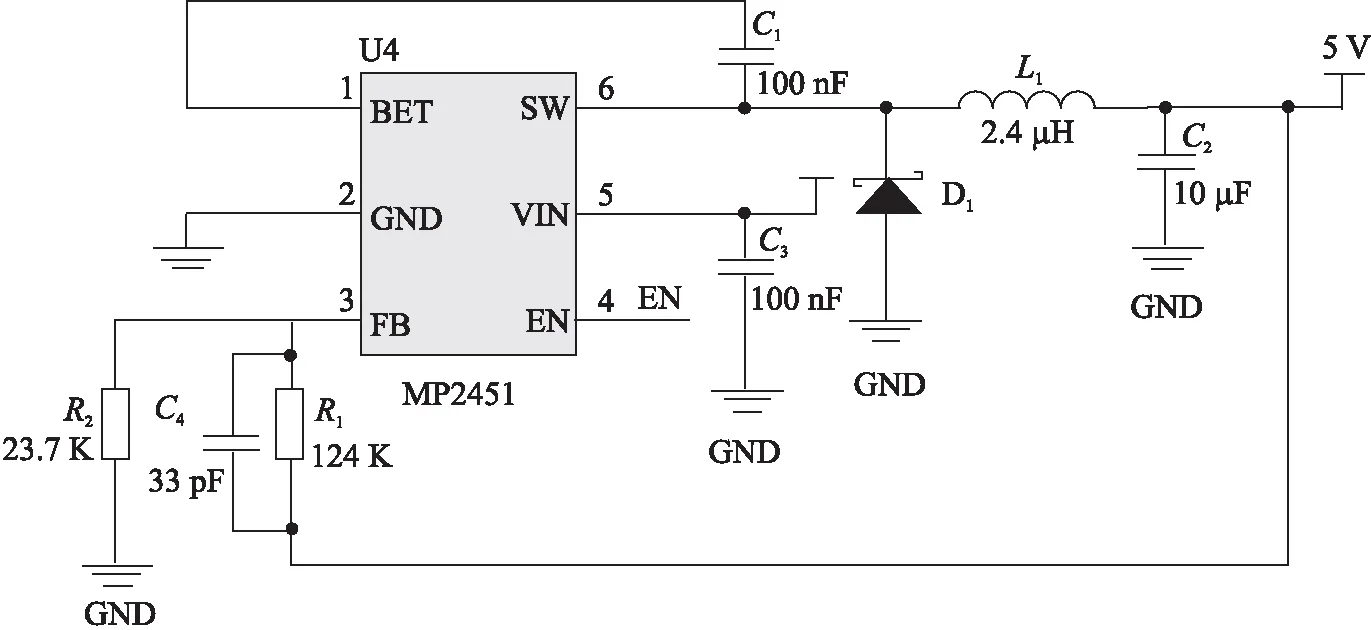

根据模块芯片需求,设计以下几种电源。一方面转换模块需要3.3 V电压,选取TPS79358作为5 V~3.3 V电压转换芯片,电路如图6所示;另一方面MAX662A需要5 V输入电压,选取MPS公司的MP2451作为12 V~5 V的转换芯片,原理如图7所示。

图6 5 V~3.3 V电路图

图7 12 V~5 V电路图

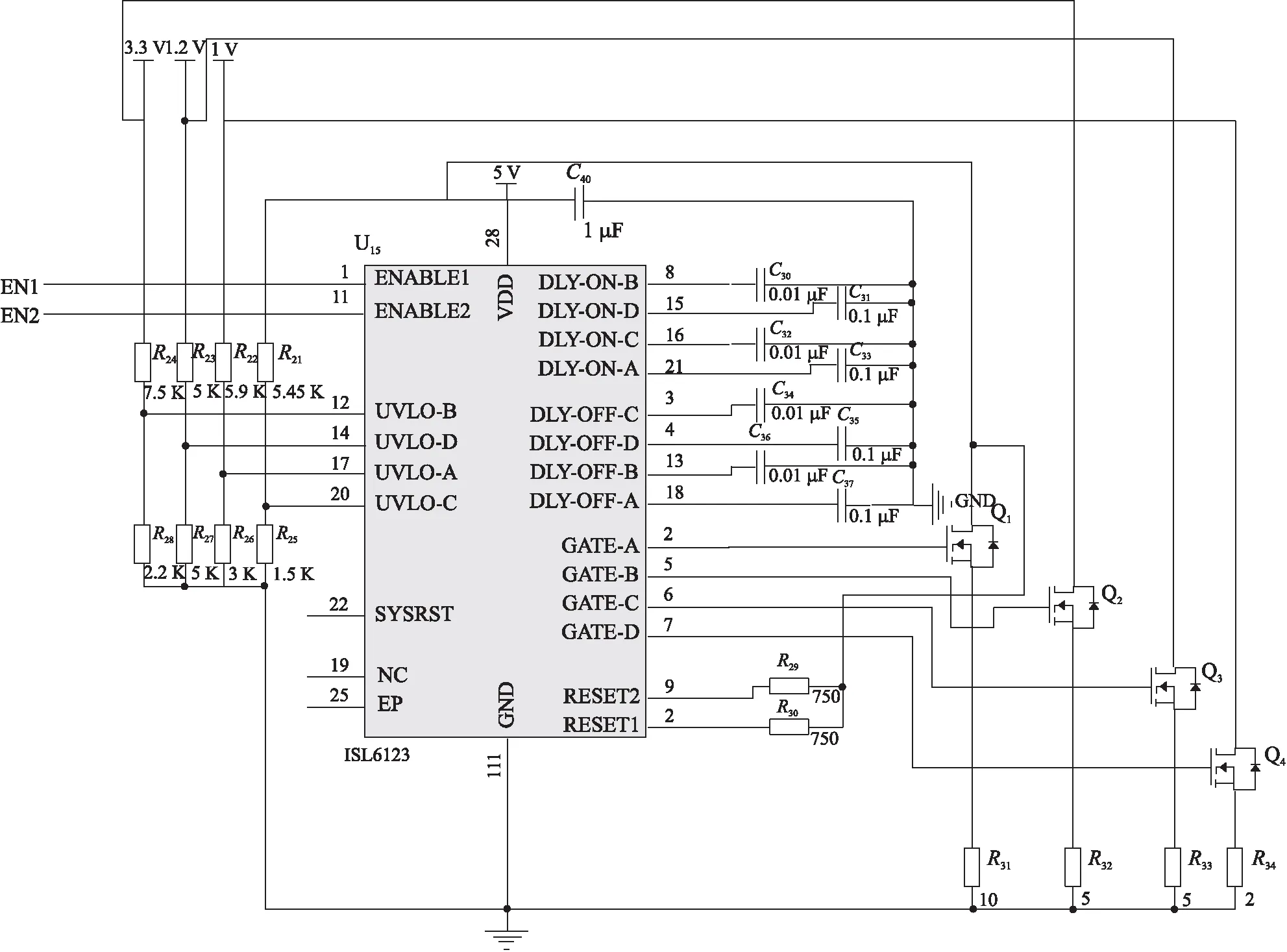

芯片PEX8619需要3.3 V,1.2 V,1 V 3种电压,最后选用PTH08T220W来提供12 V~1.0 V的电压,LP3964来实现3.3 V~1.2 V之间的电压转化。芯片PEX8619需要3种电压源,并且芯片对上电和断电的顺序有着严格的要求,上电依次为1.0 V、1.2 V、3.3 V,断电相反。采用ISL6123芯片控制上电顺序,该芯片通过对应引脚连接的电容不同来控制输出信号的时间,继而可以控制电压顺序[8]。具体电路图如图8所示。

图8 上电电路图

2.5 存储模块

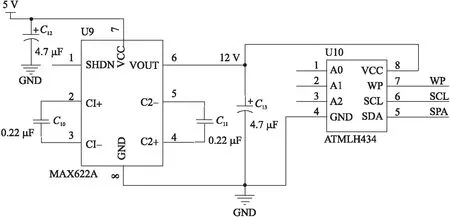

ATMLH系列芯片,两路串行接口存储器,通过施密特除法器,过滤输入,实现噪音抑制,具有双向数据传输协议。另外配置了MAX662A对其进行输入控制,通过输出12 V电压直接给Flash memory进行供电。具体的原理图如图9所示。

图9 存储模块

3 高速PCB仿真设计

由于电路设计包括PCI-e和PCI-x总线,其中PCI-e产生的差分信号属于高速信号。因此为了设计完整性,必须对电路进行信号完整性分析。根据前后仿真反馈,对设计进行优化[9]。

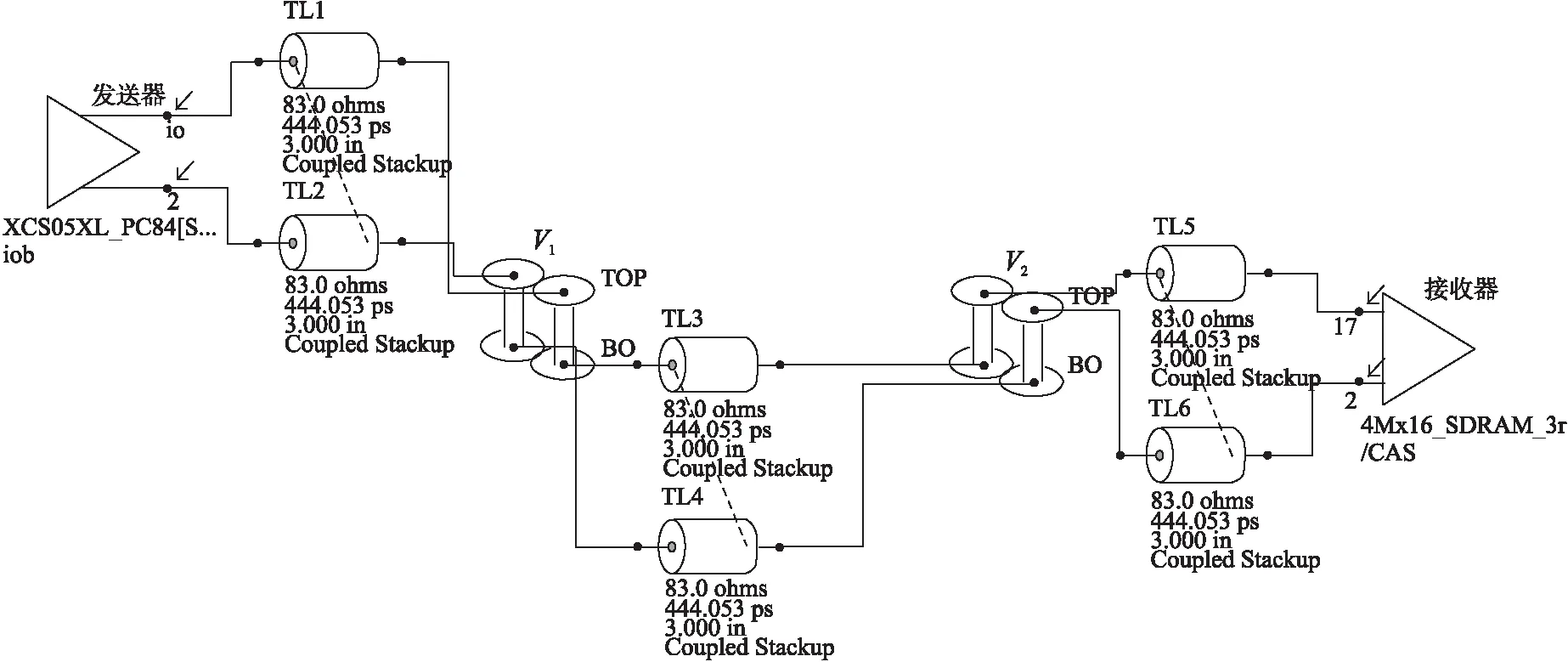

首先设计仿真原理图,如图10所示。图中是典型的PCI-e信号通道,信号发出后经过传输线再经过两次过孔,将信号传到传输层,最后经过电容接收[10]。

另外PCI-e标准阻抗要求为100 Ω,经过对线宽,介质层厚度,线间距,材料等因素的设置,最后的特性阻抗为83 Ω,满足设计要求。

图10 PCI-e仿真原理图

4 调试结果

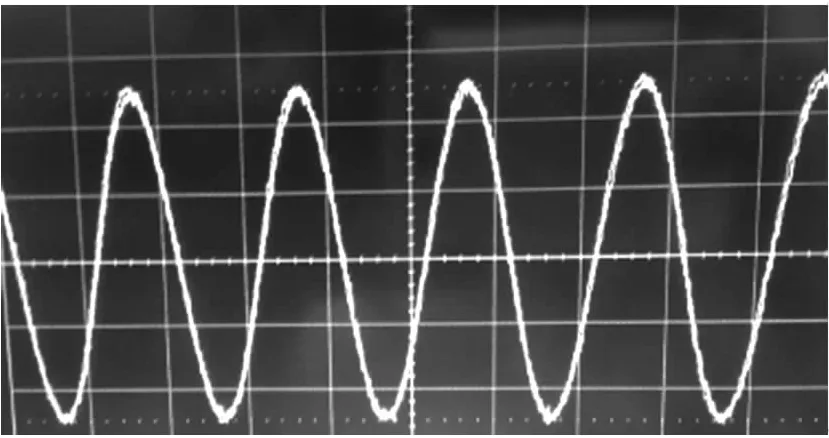

通过负载AD板卡来进行性能测试。首先FPGA连接的RAM将波形数据存入,再通过FPGA将数据输出到AD芯片中,最后由AD将产出的数据发送出去。示波器测试到输出的数据为正弦波,而且没有很大的毛刺和不规则波动。通过波形可以看出,两片AD芯片同步工作正常,基本满足技术要求,实验结果如图11所示。

图11 测试结果

5 总结

本文基于两种不同的总线标准PCI-e和PCI-x,设计出了满足使用要求的载板。XMC/PMC载板通过负载不同板卡来实现不同的功能,具有通用性,并

且使用范围广泛,适用于各种工业场合。并且随着技术的发展,VPX串行总线技术将逐步替代原有的并行架构,XMC/PMC载板将会被越来越多的使用。

[1] 王学宝. 基于VPX标准的PMC/XMC载板设计[J]. 计算机测量与控制,2010,18(8):1852-1854.

[2] 陈利彬,吴来萍,门涛. PCI Express接口200 MSps实时数据采集卡的设计[R]. 全国测控、计量、仪器仪表学术会议暨中国仪器仪表与测控技术大会,2011,32(12):39-43.

[3] 李宇. 基于FPGA的智能PMC通讯模块设计[J]. 计算机测量与控制,2011,19(11):2838-2840.

[4] 郭友洪,杨红官,尚林林. PCI Express交换器交换模块的设计及实现[J]. 微电子学与计算机,2009,26(9):114-117.

[5] 彭清泉. 基于PCI-E结构的交换转发技术研究与实现[D]. 北京:北京邮电大学,2012.

[6] 邓建廷. 基于架构高速交换系统设计和信号完整性分析[D]. 北京:北京邮电大学,2011.

[7] 胡善清,龙腾. 基于平台的串行网络系统的设计与实现[J]. 测控技术,2009,28(z1):163-165.

[8] MarkI,Montrose. 电磁兼容和印制电路板:理论、设计和布线[M]. 北京:人民邮电出版社,2002.

[9] 王屹臻.接口可重构的高速串行异构链路接入系统硬件设计[D]. 北京:北京邮电大学,2012.

[10] 李典,陈颖.下一代交换式总线技术的研究与设计[J]. 电视技术,2007,31(2):52-54.

DesignofXMC/PMCCarrierBoardBasedonPCI-eandPCI-x*

HUYanjun1,GAOFeng2,JIANGWei2,ZHANGHuixin1,ZHANGChunheng1,LIUWenyi1*

(1.North University of China,National Defense Key Laboratory For Electronic Measurement Technology,Taiyuan 030051,China;2.Beijing Aerospace Systems Engineering Institute,Beijing 100076,China)

In order to flexibly realize the function expansion in VPX system,the design uses PCI-e bus and PCI-x bus to complete the function of XMC/PMC carrier board. The carrier board is connected with different function boards through the P1-P6 connector,the data communication between the outside and the carrier board is realized by the HD68 interface,and the PCI-e switch module and the PCI-e switch PCI-x module are mainly introduced system solutions. The converting module,the switch module,the power module and the clock module are introduced in detail. In the circuit design process,the simulation is to ensure high-speed circuit signal integrity. Finally,by debugging with the AD board the XMC/PMC design is verified feasibility.

circuit design;PCI-e;PCI-x;XNC/PMC;signal integrity

10.3969/j.issn.1005-9490.2017.06.005

项目来源:国家自然科学基金项目(51425505)

2016-10-14修改日期2016-11-21

TP272

A

1005-9490(2017)06-1354-05

胡彦君(1991-),女,汉族,黑龙江牡丹江人,中北大学在读研究生,研究方向为电路设计与总线研究,18234125986@163.com;

刘文怡(1970-),男,汉族,山西岚县人,中北大学仪器与电子学院硕士生导师,教授,研究方向为微纳传感与测试技术,liuwenyi@nuc.edu.cn。