基于LPM模块的DDS波形发生器的设计

姚 宁

(许昌学院 电气(机电)工程学院, 河南 许昌 461000)

基于LPM模块的DDS波形发生器的设计

姚 宁

(许昌学院 电气(机电)工程学院, 河南 许昌 461000)

波形发生器在各类测试和相应实验中有着较为普遍的应用。本文利用DDS原理在QuartusⅡ 9.0软件上实现了一种波形发生器的设计与仿真验证,并在含有Cyclone Ⅱ系列FPGA芯片的实验开发平台上利用嵌入式逻辑分析仪(SignalTap Ⅱ)完成硬件验证。本方法设计的波形发生器能较容易的实现四种波形(正弦波、方波、三角波和锯齿波)的转换,原理简单、结果清晰、输出波形好、扩展方便,具有很大的研究意义和实用价值。

LPM;DDS;SignalTap Ⅱ;波形发生器

波形发生器在各种测试和实验领域中有着较为普遍的应用,尤其是在仪器仪表的测试、通讯系统的设计和研究过程等方面有着不能替代的作用,所以,信号发生器的设计和研究有着重要的实际意义和应用价值[1]。

随着大规模集成电路的发展,电子电路的设计方法也由“自底而上”的设过程转换成“自上而下”的设计方法,进入EDA时代(Electronic Design Automation——电子设计自动化)。EDA时期对设计者经验的依赖大大减小,设计者不必了解器件的制造工艺,只要会用相关软件画原理图或会用硬件描述语言(如VHDL、Verilog HDL),就可以在大规模可编辑逻辑器件的开发软件及实验开发系统上完成电路的设计和调试,使电子产品的设计周期变短,上市速度加快。当今的EDA技术更多的是指SOC(System on a Chip)[2]——芯片内电子系统设计自动化,所以,当代电子产品的更新换代较快。

本文以Quartus Ⅱ 9.0为设计软件,利用Altera公司提供的参数可设置模块库(LPM),应用DDS原理完成一种简易波形发生器的设计和仿真验证。硬件验证在装有Cyclone Ⅱ系列FPGA芯片(EP2C35F672C8)的实验开发系统上完成利用嵌入式逻辑分析仪(SignalTap Ⅱ)完成。

1 波形发生器简介

波形发生器可以产生四种波形——正弦波、方波、三角波、锯齿波,通过波形选择模块来实现波形的转换,原理框图如图1所示。设计过程中采用混合输入方式,累加模块(计数模块、寄存器模块)和波形存储模块采用图形编辑方式完成,波形选择模块采用文本的方式完成。优势在于,图形编辑方式输入能较快的完成设计而且设计过程明了、易于实现。此波形发生器可以在在输入信号改变的条件下选择不同的波形结果输出[3]。

图1 波形发生器原理图

2 DDS原理

美国学者J. Tierney、C. M.Rader和B. Gold在1971年提出了直接数字频率合成(Direct Digital Synthesis,DDS)技术,它是第三代频率合成技术[4],此技术以数字信号为根本,从相位的角度出发直接合成所需波形的一种新的全数字频率合成技术[5]。与传统的频率合成技术对比,DDS 具有频率鉴别率高、频率切换快和相位连续变化等优点[5]。

DDS技术结构原理如图2所示,有系统参考时钟(fclk)、相位累加器(位宽N=32)、ROM存储器(位宽9)和DAC组成。在系统参考时钟(fclk)的控制下对相位累加器、ROM存储器和DAC进行时序控制,相位累加器有加法器和寄存器级联组成,在系统参考时钟的控制下对频率控制字(B[31..0])对应的二进制代码累加,本文中将累加结果的高9位作为ROM查找表的地址,查找ROM进行寻址,经由DAC变换后再滤波就可以得到所需要的波形。输出波形频率与参考频率之间的关系[6]为

(1)

所以,通过公式(1)可知,频率控制字一定时,输出波形的频率与参考频率成正比。输出频率与频率控制字和系统参考时钟频率有关,可通过改变频率控制字和系统参考时钟来得到不同频率的输出波形。

输出波形的最小频率间隔[6]

(2)

由公式(2)可见,输出波形的精度取决于累加器的位数及系统参考时钟的频率。本文设计的波形发生器的频率误差为1‰以下。

图2 DOS原理图

3 系统设计

FPGA(Field Programmable Gate Arrays,现场可编程门阵列)是EDA技术中普遍应用的一种可编程信号处理器件[7]。FPGA的优点开发周期短、设计灵活性大、可重复编程、集成度高、内部具有丰富资源等等。运用DDS原理结合FPGA系统开发平台建立波形发生器原理简单、操作灵活、更新方便、系统体积小,且系统开发趋于软件化、自定义化[8-9]。

在此选用Altera公司的FPGA芯片——Cyclone I I系列(EP2C35F672C8)完成波形发生器的设计实现,波形实现简单,调节方便,波形发生器电路原理图如图3所示。

图3 波形发生器原理图

(1)相位累加器

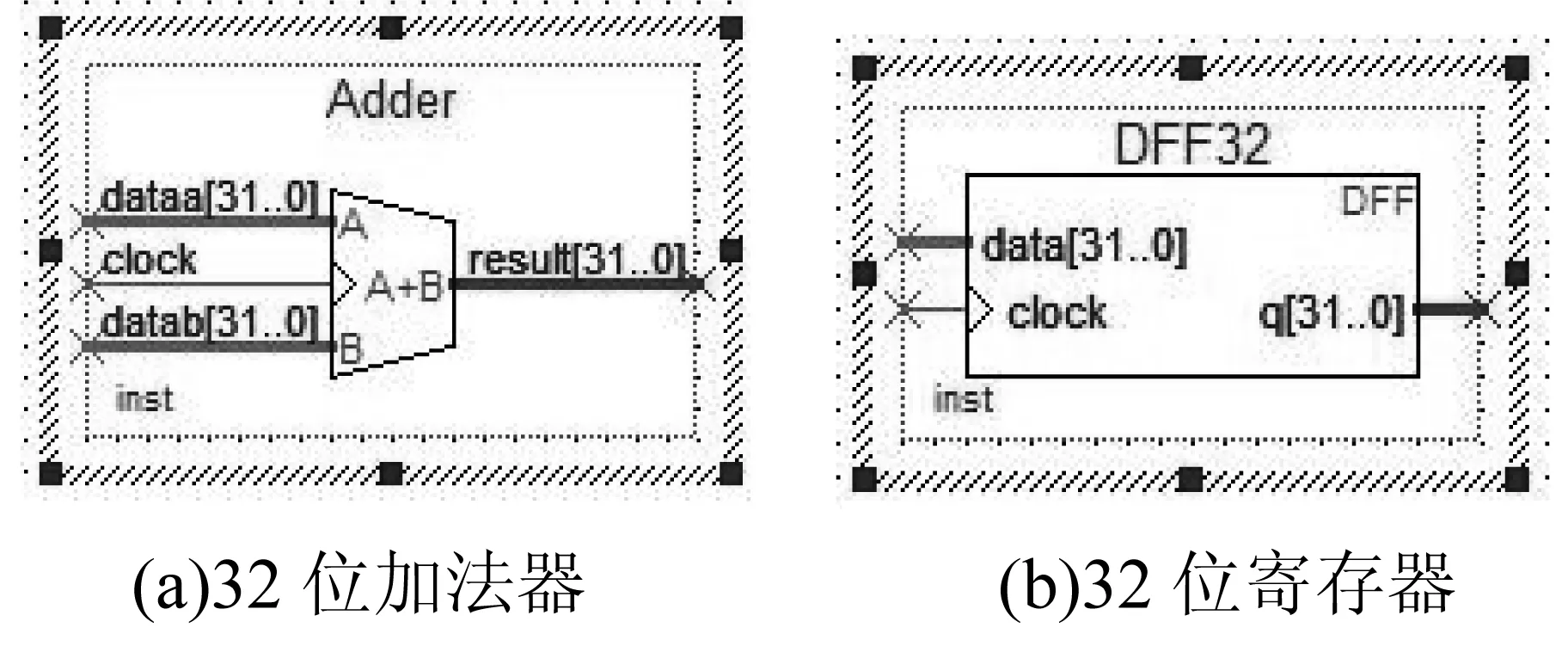

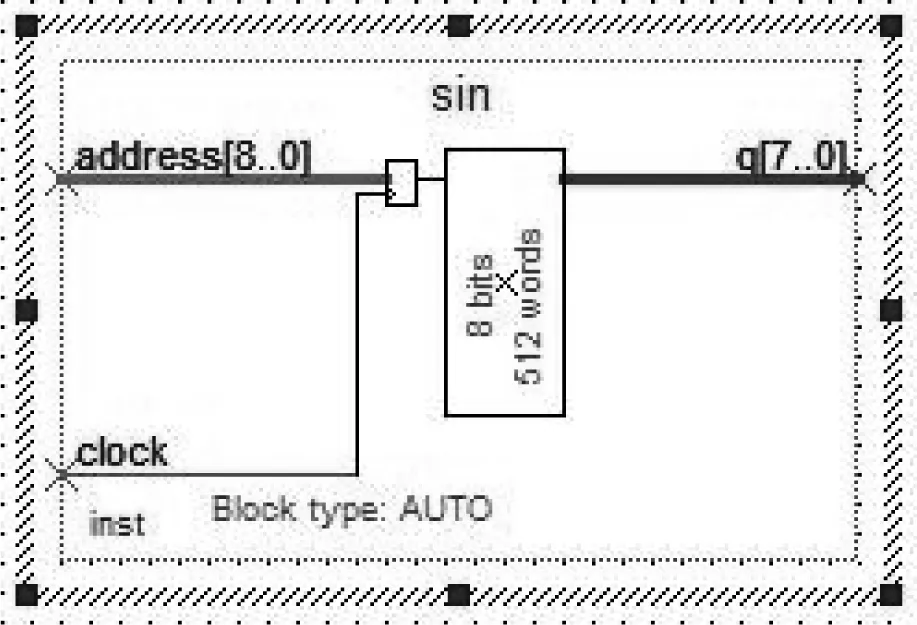

相位累加器的位宽N=32,由加法器和寄存器电路实现,分别采用LPM_ADD_SUB模块和LPM_FF模块编辑实现,如图4所示,寄存器输出的高9位A[31..23]是波形数据ROM模块的地址。

(2)波形数据ROM

波形数据ROM的地址线位宽9位、数据线位宽8位,用LPM_ROM模块单元实现,以正弦波模块为例,如图5所示。ROM中所需的初始化文件采用mif格式文件。mif格式文件采用专用mif文件生成器——MIF_Maker2010自动创建4种波形,保存后调入ROM。

图4 相位累加器模块图

图5 正弦波模拟ROM结构图

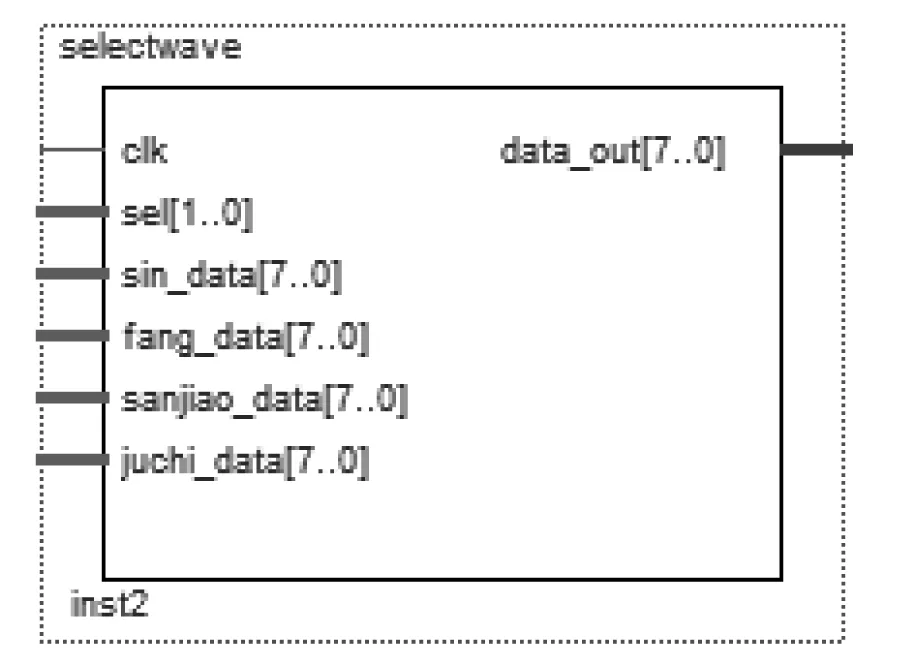

(3)多路选择器

波形选择由4选1多路选择器实现,采用文本输入方式(VHDL语言)实现。主体部分程序如下:

…

entity selectwave is

port(clk:in std_logic;

sel:in std_logic_vector(1 downto 0);

sin_data:in std_logic_vector(7 downto 0);

fang_data:in std_logic_vector(7 downto 0);

sanjiao_data:in std_logic_vector(7 downto 0);

juchi_data:in std_logic_vector(7 downto 0);

data_out:out std_logic_vector(7 downto 0));

end ;

architecture sel of selectwave is

begin

with sel select

data_out<=sin_data when "00",

fang_data when "01",

sanjiao_data when "10",

juchi_data when "11";

end;

编译完成后,多路选择器的元件封装图如图6所示。

图6 4选1多路选择器原理图

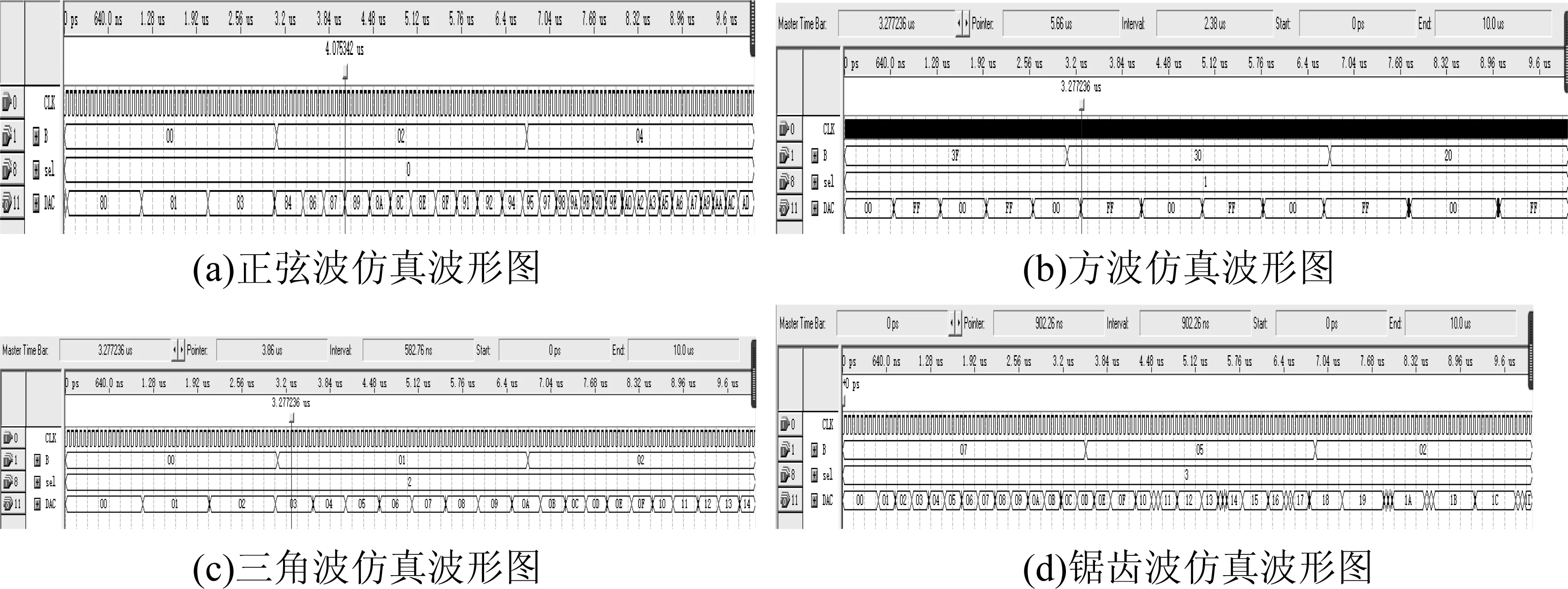

(4)仿真验证

波形发生器仿真波形如图7所示,图7中(a)为正弦波仿真波形图,(b)为方波仿真波形图,(c)为三角波仿真波形图,(d)为锯齿波仿真波形图,与mif文件中的数据能完全对应,可是对波形来说不直观,同时也不利于观察。所以在此调用逻辑分析仪——SignalTap Ⅱ验证。

图7 波形仿真图

4 SignalTap Ⅱ——逻辑分析仪验证

逻辑分析仪(SignalTap Ⅱ)是一种测试硬件系统的高效的测试手段。将波形发生器的引脚锁定在Cyclone Ⅱ系列FPGA芯片(EP2C35F672C8)的实验箱上,调入逻辑分析仪,4种波形的显示结果如图8所示。为了验证方便,在此将频率控制字B的低20位设为高电平,高6位设为低电平。当波形控制键Sel取00、01、10、11时输出波形分别对应正弦波、方波、三角波、锯齿波,其中(a)、(c)、(e)、(g)是频率控制字时对应的4种波形的显示结果,(b)、(d)、(f)、(h)是频率控制字B=226时对应的4种波形的显示结果。逻辑分析仪的验证结果相较于图3的波形图结果更为直观,从结果中可以直接看出B=224时的周期是B=226时周期的4倍,频率是对应的4分之1,与原理相符。

图8 逻辑分析仪图形显示

5 总结

基于LPM模块的DDS简易波形发生器较容易的实现了正弦波、方波、三角波、锯齿波四种波形的设计和仿真验证,原理简单、结构清晰、波形转换快、输出波形好、成本低。

同时FPGA芯片功能多,其性能基本上能适合绝大多数系统的要求[10],因此,DDS与FPGA的结合,使系统性价比大大提高。本设计目前测试阶段不需印刷电路板,省时省力,并且方便后续对此项目的优化和扩展。

[1]张林行,尚小虎,等.一种基于FPGA 的DDS 信号源实现[J].微型电脑应,2015,(31)12:16-18.

[2]谭会生,张昌凡.EDA技术及应用 (第二版)[M].西安:西安电子科技大学出版社,2006.

[3]郑亚民,董晓舟.可编程逻辑器件开发软件Quarter Ⅱ[M].北京:国防工业出版社,2006.

[4]宋寅.基于FPGA的DDS波形发生器的设计与实现[J] .合肥学院学报, 2017,17(2):63-66.

[5]Tierney, J., Rader, C., Gold, B. A digital frequency synthesizer[J]. Audio and Electroacoustics, IEEE Transactions on.1971, 19(1):48-57.

[6]潘松,黄继业.EDA技术实用教程——VHDL版(第五版)[M].北京:科学出版社,2014.

[7]杨海钢,孙嘉斌,王慰.FPGA 器件设计技术发展综述[J] .电子与信息学报,2010,(3):714-727.

[8]李雪梅,张宏财,王学伟.基于DDS 技术的信号源设计[J].电测与仪表,2012,(1):55-56,66.

[9]郝建卫.基于FPGA 的脉冲宽度调制信号发生器[J].计算机工程,2013,(2):260-264,269.

[10]余勇,郑小林.基于FPGA的DDS正弦信号发生器的设计和实现[J].电子器件,2005,(3):596-599.

Design of DDS Waveform Generator Based on LPM Module

YAO Ning

(College of Electrical and Information Engineering, Xuchang University, Xuchang Henan 461000, China)

Waveform generator has a wide range of applications in various experiments and tests. The design and simulation of the waveform generator are implemented using the DDS principle on QuartusII 9.0 software. The hardware validation was performed on an experimental development platform containing the Cyclone II FPGA chip, using the embedded logic analyzer (SignalTap II).The waveform generator designed by this method can easily realize the transformation of four waveforms - sine wave, square wave, triangle wave and sawtooth wave. It has great research significance and practical value with the characteristics of simple principle, clear result, good output waveform and convenient extension.

LPM; DDS; SignalTapII; waveform generator

TN710

A

1674-344X(2017)8-0034-04

2017-06-10

许昌学院校级科研项目(2017ZD010)

姚 宁(1980-),女,河南许昌人,副教授,硕士,研究方向为电子电路、电子设计自动化。