基于脉冲跨周期调制的DC-DC变换器自适应电压调节技术

王东俊 罗 萍 彭宣霖 甄少伟 贺雅娟

基于脉冲跨周期调制的DC-DC变换器自适应电压调节技术

王东俊 罗 萍*彭宣霖 甄少伟 贺雅娟

(电子科技大学电子薄膜与集成器件国家重点实验室 成都 610054)

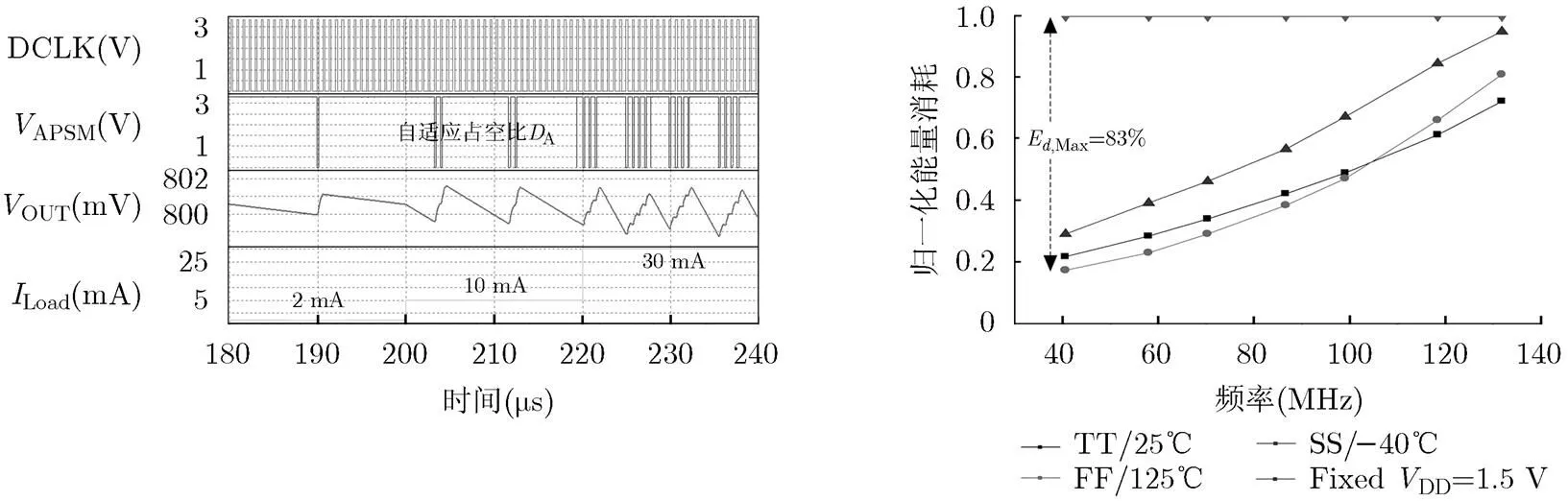

为实现减小数字电路的供电电压来降低其能量消耗的目的,该文提出基于脉冲跨周期调制(PSM)的DC- DC变换器自适应电压调节(AVS)技术。AVS技术通过追踪和探测关键路径复制(CPR)的延迟时间自适应地调节数字电路的供电电压。同时,具有自适应占空比的PSM调制模式(APSM)被用来改善轻负载下变换器输出电压的纹波和效率。实验结果显示,当负载工作频率在30~150 MHz范围内变化时,输出电压在0.6~1.5 V之间稳定输出。和传统的固定工作电压相比,该文设计的DC-DC变换器最大可节省83%的能耗。

DC-DC变换器;自适应电压调节;脉冲跨周期调制;关键路径复制;自适应占空比

1 引言

片上系统(SoC)受益于集成电路制造工艺的快速发展而经历了高速发展阶段。因此在单一芯片上集成了越来越多的功能,而芯片的尺寸却在持续减小,造成电子系统的能耗密度急剧增加。而能量消耗却是评估电子器件性能的重要指标之一。所以,能量消耗成了以电池作为供电系统的便携式、穿戴式和可移植医疗电子等新兴电子产品的重要问题[1,2]。动态电压调整(DVS)作为降低数字电路能耗和提高变换器效率一种非常有效的方式而被广泛用来约束数字电路的能耗。但是DVS是一种需要提前预置查找表(LUT),工作在开环状态的电压频率调节技术。因此,为了保证数字电路在最坏的工艺和环境下正常工作,预留了一定的供电电压裕度。然而过度保守的电压裕度导致了数字电路能耗和性能的损失,同时这种极端的工艺和工作环境也很少出现。所以,从能耗和应用的观点出发,过保守的电压裕度正变得不再被接受[6]。

为了减小一点最坏情况下的电压裕度,关键路径复制(CPR)技术被广泛用在具有闭环调节特性的自适应电压调节(AVS)技术中。由于在工作环境和频率的多种组合下,CPR能提供最接近数字电路实际性能的指标,因而数字电路的供电电压能够被自适应地调节到最小值。在现代深亚微米技术下,由反相器组成的简化了的复制关键路径变的越来越不可靠,因其在不同的工艺角或工作状态之间会发生较大变化[9]。事实上,在关键路径延时的测量中,由于CPR和关键路径之间结构的差异引起的误差十分微小,而在不同的工艺和工作环境下由片内互连引起的延迟误差却急剧增加。基于这些原因,一种能够复制任何产品的关键路径而无需定制的通用延迟线(UDL)结构被提出[10]。实验显示关键路径的延时主要由NMOS和PMOS组成的具有“2:2”双堆叠的电路结构引起,故UDL由具有双堆叠的电路结构组成。但是UDL的控制逻辑十分复杂,因此消耗了一部分因减小电压裕度而节约的能量,且在变换器的负载较轻时更加显著。

现在,随着低压低功耗技术的发展,数字电路的能耗在不断减小,因此DC-DC变换器的负载变的越来越轻,每个开关周期内变换器输出电压的调节和能量传递变的越来越细微和精确[11]。因此从应用和能量传递的角度不再接受较大的输出电压纹波[12]。当变换器工作在断续导通模式(DCM)或负载较轻时,脉冲跨周期调制(PSM)模式被用来改善变换器的效率。PSM是一种改善变换器转换效率的新奇的控制模式[13,14]。在PSM控制下,变换器具有较小的谐波和较快的响应速度,但是其输出电压纹波有点大。为了改善输出电压纹波和转换效率,本文提出了一种具有自适应占空比的PSM调制模式(APSM)。

基于PSM DC-DC变换器的AVS技术,通过AVS和CPR技术降低数字电路的工作电压并消除一定的电压裕度,最终实现降低数字电路能耗的目标。本文提出的APSM控制模式改善了变换器的电压纹波和转换效率。本文分析了DC-DC变换器的电路结构和APSM控制模式的工作原理,通过仿真验证了所提出的电路结构能显著降低数字电路能耗,实验结果显示了输出电压对频率变化的跟随和APSM控制模式对电压纹波的改善。

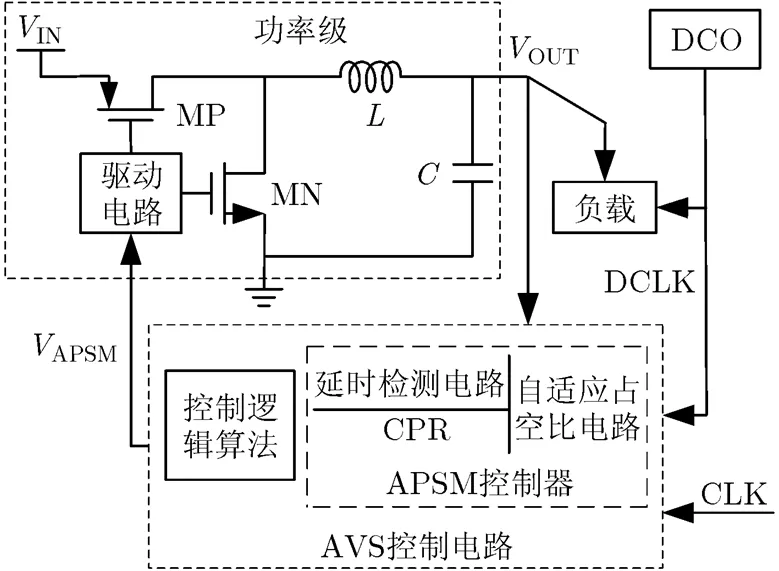

图1 DC-DC变换器的整体结构框图

2 DC-DC变换器整体电路结构和工作原理分析

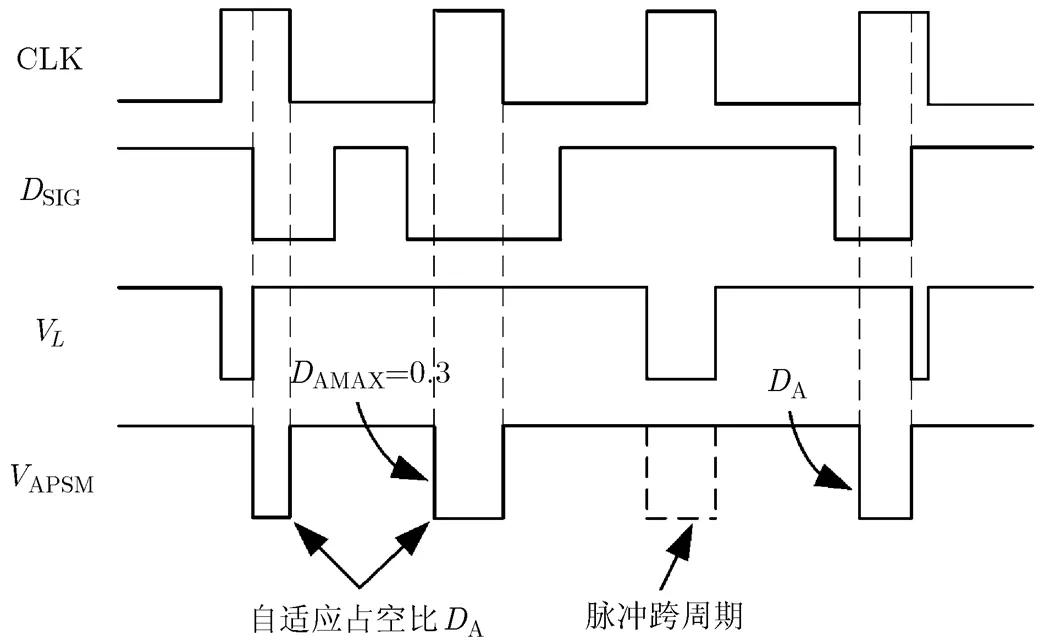

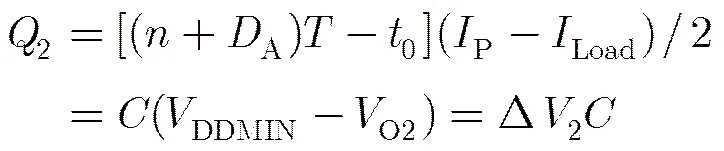

图1显示了本文提出的具有AVS功能的DC- DC变换器整体结构框图。由于变换器工作在DCM模式下,因此变换器的电路结构由于不需要环路补偿而变得简单且容易实现[18]。图1中主要包括功率级、驱动电路、负载、数控振荡器(DCO)和AVS控制电路。AVS控制电路主要由控制逻辑算法和APSM控制器组成,其中控制逻辑算法通过数字设计方法实现。负载可以是数字信号处理(DSP)、便携式产品和医疗电子等数字电路,其等效电阻为Load。DC-DC变换器的输出电压OUT作为负载的工作电压,DCO产生的时钟DCLK作为负载的工作时钟。APSM控制器中的延时检测电路能够检测时钟DCLK通过CPR的延时D和电压OUT之间的关系,并输出调压信号SIG。当负载以某一频率DCLK工作时,如果输出电压OUT小于使负载能正常工作的最小电压DDMIN,则延迟时间D大于时钟DCLK的周期DCLK,同时调压信号SIG为低电平。相反,当OUT>DDMIN时,则D 当OUT 2.1 APSM控制器工作原理 在数字电路各种能量消耗中,由开关电容充放电引起的动态功耗d是数字电路能量消耗的主要成分,有 其中,DD,eff和分别是供电电压,平均开关电容和活跃因子[19]。但是对于一个给定的任务,数字电路完成该任务需要的时钟周期个数是恒定不变的[9]。所以,如果数字电路完成该任务的时间OP=DCLK在式(1)中被考虑,有 (2) 其中,DCLK=1/DCLK。如式(2)所示,当数字电路的工作电压DD不变而工作频率DCLK发生变化时,其动态能耗保持不变。这也是在实现低功耗技术中改变工作电压DD而不是工作频率DCLK的原因。然而对于一个包含有级门电路的延迟链,例如对数字负载关键路径复制的CPR的工作电压为DD时,时钟DCLK穿过CPR的延迟时间D为 (4) 因此,供电电压DD有一个最小值DDMIN使式(4)成立。即当CPR的工作频率为DCLK时,使CPR能够正常工作的最小电压为DDMIN。由于CPR是对数字负载关键路的复制,为了提高CPR对关键路径的复制精度同时减小电压裕度,CPR由具有“2:2”双堆叠的NMOS和PMOS结构组成[10]。所以,CPR能够模拟负载在不同工作环境和频率下的实际工作状态,通过对CPR的紧密追踪和跟随可以得到负载即时的性能指标。同时,根据式(4)时钟频率DCLK和最小工作电压DDMIN之间有一对一的关系,即对于任意的工作频率DCLK,都有一个最小工作电压DDMIN与之对应。然而,当频率DCLK保持不变时,延迟时间D会随着负载工作环境和温度的变化而变化,因此根据式(4)最小工作电压DDMIN也会发生改变。同样地,当频率DCLK因系统或工作任务而改变时,最小工作电压DDMIN随着延迟时间D的变化而不同。 当数字负载的工作频率DCLK保持恒定而工作电压DD等于其最小工作电压DDMIN时,式(1)中数字负载的动态功耗d有最小值。但是,即使数字负载的工作频率DCLK保持不变,由于负载工作环境和温度的变化使得最小电压DDMIN不同,动态功耗d的最小值随着电压DDMIN的变化而变化。然而,如何检测延迟时间D和最小电压DDMIN的变化是一个十分关键的问题,而APSM控制器则能有效地解决该问题,APSM控制器可以敏感地检测到DDMIN和D的变化,同时输出调压信号SIG。 APSM控制器电路框图如图2所示,主要包括延迟检测电路,CPR和自适应占空比电路。其中延迟检测电路和CPR的工作原理如图3所示。当数字负载以某个频率DCLK工作时,如果其供电电压DD(即DC-DC变换器的输出电压OUT)大于最小电压DDMIN,则延迟时间D小于DCLK的时钟周期DCLK。所以DCLK的上升沿在一个周期DCLK内可以通过CPR。正如图2和图3所示,时钟DCLK的上升沿可以用信号F的上升沿代替。所以,如果OUT>DDMIN,在一个周期DCLK内F的上升沿能够通过CPR。与非门接收信号DT和F,同时输出低电平信号Xor。D触发器被信号F_n的上升沿触发,采样到Xor信号的低电平,同时输出高电平调压信号SIG。与此相反,如果OUT 图2 APSM控制器的电路结构框图 图3 延迟检测电路的工作原理 图4 延迟检测电路频率fDCLK和电压VDDMIN之间关系的仿真 在APSM控制器中,延时检测电路仅仅能够获得调压信号SIG,但是自适应占空比电路能够根据SIG信号生成具有自适应占空比的控制脉冲APSM。如图2所示,自适应占空比电路结构非常的简洁和易于实现,其工作原理如图5所示。工作时钟CLK的频率和占空比分别为2 MHz和0.3。在时钟CLK开关周期的高电平开始时,如果信号SIG为高电平,功率开关将不会开启,输出电压OUT因为负载消耗了滤波电容中的电荷而逐渐减小。同时,在该周期的高电平期间一旦SIG变为低电平(OUT 2.2 控制逻辑算法 在APSM控制器模块中,延迟检测电路可以对负载的实际工作性能进行检测,结果用SIG信号的高低电平表示。而自适应占空比电路根据SIG信号生成的控制脉冲APSM对电压OUT进行调节。然而,各个模块之间怎样协同高效工作却是一个问题。实际上,模块之间的相互配合对整个电路保持稳定、性能优化和效率改善是非常重要的。因此,为达到改善电路性能和实现自适应电压调节的目的,在DC-DC变换器中加入了控制逻辑算法。如图6给出了控制逻辑算法的工作原理。当环路开始时,通过DCO的控制码设定数字负载的工作频率DCLK。然后延迟检测电路开始对负载在电压OUT下的工作状态进行检测。如图3所示,如果OUT>DDMIN,则负载和CPR能够正常工作且SIG为高电平;如果OUT 图5 自适应占空比产生电路的工作原理 当整个环路开始时,设定好工作频率DCLK的初始值。如果OUT 然而,还有另外一种情况,即一旦频率DCLK发生改变,无论电压OUT正处于上升、下降或是稳定状态,根据此时OUT值控制逻辑算法将立刻重新开始。同时,延迟检测电路将对负载在新工作频率DCLK下的工作状态进行检测。APSM模块将根据调压信号SIG对输出电压OUT进行自适应调节。因此,控制逻辑算法使得DC-DC变换器模块之间的相互协调变的更加紧密,优化了变换器的性能,改善了能量转换的效率。 图6 DC-DC变换器控制逻辑算的工作原理 为了对DC-DC变换器的输出电压纹波进行分析和讨论,定义参数e为电压误差且e=DDMIN-OUT;参数A(非0和AMAX)为在一个开关周期内控制脉冲APSM的自适应占空比;参数Load为数字负载的等效电阻,而定义为DC-DC变换器输出电压OUT的电压纹波。当具有AVS功能的DC-DC变换器在DCM模式下稳定工作时,将详细分析在一个开关周期内参数A,Load,和e之间的密切关系。在一个开关周期内输出电压OUT和电感电流I的波形如图7所示,在开关周期开始时,假设变换器的输出电压O1小于最小工作电压DDMIN,则在到(+A)的时间内,有电感电流I: 其中,,为滤波电感值和控制脉冲APSM的时钟周期。在0时刻,有电感电流I: (6) 从到0的时间内从滤波电容中流出的电荷1为 其中,是滤波电容值。在(+A)时,有电感的峰值电流P: (8) 在0到(+A)的时间内,流入滤波电容的电荷2为 有电压误差e为 (10) 联立式(5)-式(9)代入式(10),有自适应占空比A 如式(11),当数字负载的等效电阻Load保持不变时,自适应占空比A将会随着电压误差e的增加而变大,但是A的最大值被限制为最大占空比AMAX。同样当电压误差e不变时,占空比A随着负载等效电阻Load的逐渐变大而越来越小,且其最小值为A=2OUT/[Load·(INOUT)]。 在时间(+A)到1之间,有I: 在1时刻,电感电流I等于负载电流Load,故 (13) 在(+A)到1时间内流入滤波电容的电荷3为 (15) 联立式(5)~式(9)和式(12)~式(14)代入式(15),有电压纹波 根据式(16)知,当负载等效电阻Load固定时,电压纹波随着占空比A的增加而变大。而当A保持不变时,负载越轻则越大。综合式(16)和式(11),占空比A随着电压误差e的变化而自适应变化,且正比于e的平方根。因此,如果电压误差e突然变大,即DC-DC变换器的输出电压OUT突然急剧下降,则占空比A也会立刻增加,这提升了变换器的响应速度但也导致电压纹波变大。因此负载越轻,占空比A越小,纹波电压越小。所以,当OUT>DDMIN,控制脉冲APSM的占空比A为零。否则A随着e的变化而自适应地改变。因此,本文提出的APSM技术改善了输出电压的纹波。DC-DC变换器在不同负载下的仿真结果如图8,变换器输出电压OUT的纹波随着负载的变轻而减小,同时可以明显看到控制脉冲APSM的跨周期和自适应占空比现象。 图7 一个开关周期内自适应占空比和电压误差之间的关系示意图 本文中基于PSM DC-DC变换器的AVS技术使用标准0.13 μm CMOS工艺制造,其中芯片版图面积为1.2 mm2。图1中显示的主要模块都被集成在芯片上,包括功率MOS和驱动电路。片外器件只有滤波电感和滤波电容,其值分别为3.3 μH和2.2 μF。当负载的工作频率在30~150 MHz范围内变换时,DC-DC变换器自适应的调节其输出电压OUT在0.6~1.5 V之间变化。根据式(2)对数字电路能量消耗的定义。图9给出了不同的温度和工艺角下,工作频率不同时数字负载的能量消耗。在使用本文提出的基于脉冲跨周期DC-DC变换器的自适应电压调节技术,相比于传统固定工作电压的电路最多能节约83%的能量。 图10给出了当数字负载的工作频率变化时,DC-DC变换器的输出电压OUT对频率变换的响应波形。如图10(a),当数字负载工作频率从50 MHz变到122 MHz时,电压OUT变化了大约0.6 V,建立时间大约为35 μs。如图10(b),负载工作频率从161 MHz变到32 MHz时,电压OUT变化了大约1.1 V时建立时间为65 μs。图11则给出了数字负载工作频率从50 MHz变到152 MHz或从152 MHz变到50 MHz时,输出电压OUT大约变化了0.9 V。 图12给出了DC-DC变换器稳定工作时,功率开关的控制脉冲APSM、调压信号SIG和输出电压OUT的测试波形。电压OUT的纹波大约为50 mV。同时能很明显的观察到控制脉冲APSM的自适应占空比及其脉冲跨周期现象。其中,控制脉冲APSM的自适应占空比现象是当输出电压OUT趋于稳定时,由于OUT 图8 不同负载下,DC-DC变换器的仿真结果 图9 不同温度、工艺角和频率下,数字负载的能耗示意图 图10 DC-DC变换器频率追踪测试波形 图11 DC-DC变换器上下调压时频率追踪测试波形 图12 DC-DC变换器稳定工作时,信号VOUT, VAPSM和DSIG的测试波形 表1性能比较 序号文献[3]文献[5]文献[6]文献[8]文献[9]文献[10]本文 输入电压(V)/2.6-3.6///1.13.3 输出电压(V)0.7-1.01.7-1.81.0-1.20.4-0.80.9-1.8/0.6-1.5 工艺90 nmCMOS0.13 μmCMOS65 nmCMOS22 nmCMOS0.18 μmCMOS40 nmCMOS0.13 μmCMOS 芯片面积(mm2)/5.29/4.0×5.80.9×0.96.51×6.51.2 工作频率(MHz)40-1452/80010-4553340-145 峰值性能节约87%能量@0.62 V最大效率95%节约13.5%能量节约14.5%能量@0.8 V节约39%能量节约27%能量@1 V节约83%能量 本文提出了基于脉冲跨周期DC-DC变换器的自适应电压调节技术,通过理论分析和仿真结果验证了APSM技术和自适应电压调压技术的工作原理。由于CPR技术在AVS中的使用,减小了数字电路的工作电压和能量消耗。通过使用APSM技术,控制脉冲的占空比随着变换器输出电压的变化而自适应地改变,进而改善了输出电压的纹波。仿真和测试结果显示DC-DC变换器根据数字负载工作环境、温度和频率的变化而自适应地调节输出电压,其在频率响应阶段能稳定工作,同时证实了关于电压纹波的理论分析。该电路结构在便携式、可穿戴电子产品和可植入医疗电子等低压低功耗电子产品中具有广泛的应用前景。 [1] KONIJNENBURGM, STANZIONE S, YAN L,. A battery-powered efficient multi-sensor acquisition system with simultaneous ECG, BIO-Z, GSR, and PPG[C]. IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, USA, 2016: 480-481. [2] DINI Michele, ROMANI Aldo, FILIPPI Mtteo,. A nanocurrent power management IC for low-voltage energy harvesting sources[J]., 2016, 31(6): 4292-4304. [3] JOSE Luis and NUNEZ Yanez. Adaptive voltage scaling with in-situ detectors in commercial FPGAs[J]., 2015, 64(1): 45-53. doi: 10.1109/ TC.2014.2365963. [4] DANCY A P, AMIRTHARAJAH R, and CHANDRAKASAN A P. High-efficiency multiple-output DC-DC conversion for low-voltage systems[J].(), 2000, 8(3): 252-263. doi: 10.1109/92.845892. [5] ZHEN Shaowei, LUO Ping, and ZHANG Bo. Design of highly integrated power management unit with dual DVS-enabled regulators[J]., 2014, 80: 209-220. doi: 10.1007/s10470-014-0313- 1. [6] WIRNSHOFER M, HEIβ L, GEORGAKOS G,. A variation-aware adaptive voltage scaling technique based on in-siut delay monitoring[C]. IEEE 14th International Symposium on Design and Diagnostics of Electronic Circuits & Systems (DDECS), Cottbus, Germany, 2011: 261-266. [7] LUO Ping, FU Songlin, ZHANG Xiang,. An adaptive voltage scaling circuits based on dominate pole compensation [C]. Processing 11th IEEE International Conference on ASIC, Chengdu, China, 2015: 1-4. [8] CHO M, KIM S, TOKUNAGA C,. Post-silicon voltage-guard-band reduction in a 22nm graphics execution core using adaptive voltage scaling and dynamic power gating [C]. IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, USA, 2016: 152-153. [9] ELGEBALY M and SACHDEV M. Variation-aware adaptive voltage scaling system[J].(), 2007, 15(5): 560-571. doi: 10.1109/TVLSI.2007.896909. [10] IKENAGA Y, NOMURA M, SUENAGA S,. A 27% active-power-reduced 40-nm CMOS multimedia SoC with adaptive voltage scaling using distributed universal delay lines[J]., 2012, 47(4): 832-840. doi: 10.1109/JSSC.2012.2185340. [11] KAPAT S, BANERJEE S, and PATRA A. Discontinuous map analysis of a DC-DC converter governed by pulse skipping modulation[J]., 2010, 57(7): 1793-1801. doi: 10.1109/TCSI.2009. 2034888. [12] LIOU W R, YEH M L, and KUO Y L. A high efficiency Dual-Mode buck converter IC for portable applications[J]., 2008, 23(2): 667-677. doi: 101109/TPEL.2007.915047. [13] LUO Ping, LI Zhaoji, and ZHANG Bo. A novel improved PSM model in DCDC converter based on energy balance[C]. 37th IEEE Power Electronics Specialists Conference, Jeju, South Korea, 2006: 1-4. [14] KAPAT S, MANDI B C, and PATRA A. Voltage-mode digital pulse skipping control of a DC-DC converter with stable periodic behavior and improved light-load efficiency[J]., 2016, 31(4): 3372-3379. doi: 10.1109/TPEL.2015.2455553. [15] 罗萍, 李肇基, 熊富贵, 等. 开关变换器的跨周期调制模式[J]. 电子与信息学报, 2004, 26(6): 984-988. LUO Ping, LI Zhaoji, XIONG Fugui,. Pulse-cycle skip modulation in switching converter[J].&, 2004, 26(6): 984-988. [16] 牛全民, 罗萍, 李肇基, 等. Boost 变换器跨周期调制(PSM)的状态空间平均模型[J]. 电子与信息学报, 2006, 28(10): 1955-1958. NIU Quanmin, LUO Ping, LI Zhaoji,. Space state average model of PSM in boost converter[J].&, 2006, 28(10): 1955-1958. [17] 李航标, 张波, 罗萍, 等. 开关DC-DC变换器的自适应占空比跨周期控制方法[J]. 电子与信息学报, 2014, 36(9): 2265-2271. doi: 10.3724/SP.J.1146.2013.01693. LI Hangbiao, ZHANG Bo, LUO Ping,. Pulse skip with adaptive duty ratio control technique for switching DC-DC converter[J].&, 2014, 36(9): 2265-2271. doi: 10.3724/SP.J.1146. 2013.01693. [18] LI Hangbiao, ZHANG Bo, LUO Ping,. Adaptive duty ratio modulation technique in switching DC-DC converter operating in discontinuous conduction mode[J]., 2014, 78(2): 361-371. doi: 10.1007/s10470-015-0603-2. [19] WEI G Y and HOROWITZ M. A fully digital energy-efficient adaptive power supply regulator[J]., 1999, 34(4): 520-528. doi: 10.1109/ 4.753685. [20] CALHOUN B H, WANG A, and CHANDRAKASAN A. Model and sizing for minimum energy operation in subthreshold circuits[J]., 2005, 40(9): 1778-1786. doi: 10.1109/JSSC.2005.852162. 王东俊: 男,1988年生,博士,研究方向为电源管理技术与功率集成电路. 罗 萍: 女,1968年生,教授,研究方向为电源管理技术与功率集成电路. 彭宣霖: 男,1989年生,硕士,研究方向为电源管理技术与功率集成电路. 甄少伟: 男,1982年生,副教授,研究方向为电源管理、传感器读出等模拟、混合信号集成电路设计. 贺雅娟: 女,1978年生,副教授,研究方向为低压低功耗数字电路设计. Adaptive Voltage Scaling Technique for DC-DC Converter Based on Pulse Skip Modulation WANG Dongjun LUO Ping PENG Xuanlin ZHEN Shaowei HE Yajuan (,,610054,) In order to decrease energy consumption of digital circuits by reducing the supply voltage, an Adaptive Voltage Scaling (AVS) for DC-DC converter based on Pulse Skip Modulation (PSM) is proposed. The AVS technique can scale supply voltage adaptively by probing and tracking the Critical Path Replica (CPR) delay time. To improve the output voltage ripple and efficiency of converter especially in light load, the PSM with Adaptive ratio duty (APSM) also is used. The experimental results show that the output voltage is well regulated from 0.6~ 1.5 V when the operation frequency of load varies within the range of 30~150 MHz. The maximum energy saving of 83% is obtained with the proposed converter compared to the traditional fixed voltage. DC-DC converter; Adaptive Voltage Scaling (AVS); Pulse Skip Modulation (PSM); Critical Path Replica (CPR); Adaptive duty ratio TN624 A 1009-5896(2017)01-0213-08 10.11999/JEIT160283 2016-03-28;改回日期:2016-08-30; 2016-10-17 罗萍 pingl@uestc.edu.cn 国家自然科学基金(61274027),国家自然科学基金青年基金(61404025) The National Natural Science Foundation of China (61274027), The National Natural Science Youth Foundation of China (61404025)

3 电压纹波分析

4 测试结果

5 结论