室温下溅射法制备高迁移率氧化锌薄膜晶体管

刘玉荣 , 黄 荷, 刘 杰

(1. 华南理工大学 电子与信息学院, 广东 广州 510640;2. 华南理工大学 广东省短距离无线探测与通信重点实验室, 广东 广州 510640)

室温下溅射法制备高迁移率氧化锌薄膜晶体管

刘玉荣1,2*, 黄 荷1, 刘 杰1

(1. 华南理工大学 电子与信息学院, 广东 广州 510640;2. 华南理工大学 广东省短距离无线探测与通信重点实验室, 广东 广州 510640)

为降低氧化锌薄膜晶体管(ZnO TFT)的工作电压,提高迁移率,采用磁控溅射法在氧化铟锡(ITO)导电玻璃基底上室温下依次沉积NbLaO栅介质层和ZnO半导体有源层,制备出ZnO TFT,对器件的电特性进行了表征。该ZnO TFT呈现出优异的器件性能:当栅电压为5 V、漏源电压为10 V时,器件的饱和漏电流高达2.2 mA;有效场效应饱和迁移率高达107 cm2/(V·s),是目前所报道的室温下溅射法制备ZnO TFT的最高值,亚阈值摆幅为0.28 V/decade,开关电流比大于107。利用原子力显微镜(AFM)对NbLaO和ZnO薄膜的表面形貌进行了分析,分析了器件的低频噪声特性,对器件呈现高迁移率、低亚阈值摆幅以及迟滞现象的机理进行了讨论。

薄膜晶体管; 氧化锌; 磁控溅射; 高迁移率

1 引 言

目前,用于有源驱动平板显示器的薄膜晶体管(TFT)的半导体材料普遍为多晶硅和氢化非晶硅[1-2]。多晶硅TFT虽具有相对高的载流子迁移率(50~100 cm2/(V·s))[3],但是其可见光不透明和晶粒分布的不均匀性限制了其在大面积显示器的应用。而氢化非晶硅TFT也具有可见光敏感性,且载流子迁移率通常小于1 cm2/(V·s)[4],使其难以制作高分辨率显示器。另外,多晶硅和氢化非晶硅薄膜的制备工艺往往需要相对高的温度,使得其难以应用于柔性显示及可穿戴电子产品。近年来,基于金属氧化物的TFT因具有相对高的迁移率、可见光透明、低温工艺等优势被认为是最有希望的TFT技术,在柔性显示和可穿戴电子等领域具有广阔的应用前景[5-6]。其中,ZnO基TFT因其高的载流子迁移率、宽能隙(~3.37 eV)导致可见光不敏感以及可以在室温下制备等特点而倍受关注。

对于ZnO TFT而言,选择合适的栅介质层对于优化器件性能至关重要。Wang等[7]利用ALD制备出Al2O3栅介质层和ZnO有源层,ZnO TFT的迁移率达到21.9 cm2/(V·s),开关电流比为4×108,亚阈值摆幅为0.244 V/decade。Esro等[8]采用溶液法制备HfO2和ZnO薄膜,分别充当栅介质层和有源层,获得高性能的ZnO TFT,迁移率高达40 cm2/(V·s),开关电流比达107,工作电压低至6 V。Fortunato等[9]采用RF溅射法制备SiOxNy作为ZnO TFT的栅介质层,迁移率可达70 cm2/(V·s)。Zhang等[10]则采用射频(RF)溅射法在室温下制备出以Ta2O5作为栅介质层的ZnO TFT,其迁移率高达60.4 cm2/(V·s),开关电流比为1.22×107,阈值电压为1.1 V,亚阈值摆幅为0.23 V/decade。Beox-Nilsen等[11]同样地采用射频(RF)溅射法在室温下制备出以Ta2O5作为栅介质层的ZnO TFT,并通过调节ZnO溅射沉积时的氩氧比,使器件的迁移率最高值超过100 cm2/(V·s),开关电流比大于105,亚阈值摆幅约为0.3 V/decade。

然而,目前报道的ZnO薄膜的霍尔迁移率最高达440 cm2/(V·s)[12],远远高于所报道的ZnO-TFT的场效应迁移率,说明通过选择恰当的栅介质材料及制备工艺的优化,ZnO TFT的场效应迁移率仍可能得到进一步的提高。本文面向ZnO-TFT在未来基于塑料基底的柔性显示器及可穿戴电子产品的应用需求,室温下采用RF溅射法沉积NbLaO栅介质层和ZnO半导体有源层,制备出高迁移率的ZnO TFT,并对器件的电特性进行了测试与讨论。

2 实 验

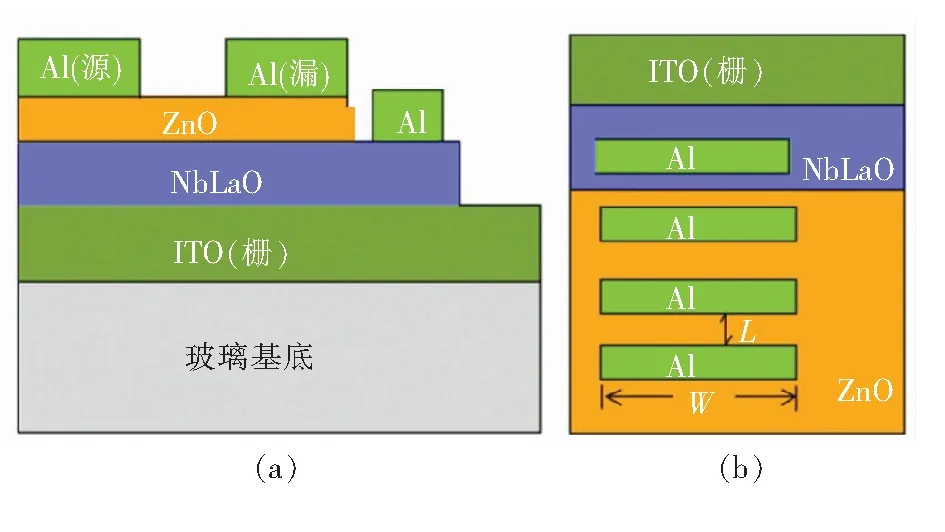

实验样品以氧化铟锡(ITO)导电膜玻璃作为衬底,且ITO为栅(G)电极,依次用高纯水、丙酮、乙醇超声清冼ITO玻璃基片。接着,采用磁控溅射法在ITO上沉积一层NbLaO薄膜作为栅介质层。NbLaO薄膜通过Nb靶和La2O3靶双靶共溅法得到。其中Nb靶采用直流溅射, 直流电流为0.02 A;La2O3靶采用RF溅射,RF功率为45 W,Ar与O2的流量(cm3/min)为24∶6,溅射时间为350 min。随后,采用RF溅射在NbLaO薄膜上沉积ZnO薄膜半导体有源层,RF功率为50 W,Ar与O2的流量(cm3/min)为24∶1,溅射时间为50 min。最后,采用真空镀膜技术通过掩膜版在本底真空度为2×10-4Pa条件下蒸发Al形成源(S)、漏(D)电极,制备出底栅顶接触型ZnO TFT。在相同ITO基片上制备ZnO-TFT的同时,在沉积NbLaO和ZnO薄膜的过程中通过掩膜版暴露部分ITO和NbLaO薄膜,以便在制备S、D电极时形成Al/NbLaO/ITO结构电容器。ZnO TFT和Al/NbLaO/ITO电容的器件结构剖面图和俯视图如图1所示。ZnO-TFT样品的沟道长度与宽度由所用掩膜版图形来确定,器件的沟道长度(L)为80 μm,沟道宽度(W)为400 μm。值得一提的是,在溅射沉积NbLaO和ZnO薄膜过程中基底温度均为室温,且样品制备全过程没有进行退火处理。

图1 ZnO TFT和Al/NbLaO/ITO电容的器件结构。(a)剖面图;(b)俯视图。

Fig.1 Schematic diagrams of ZnO TFT and the capacitance with Al/NbLaO/ITO structure. (a) Cross-sectional view. (b) Top view.

NbLaO和ZnO薄膜的厚度采用德国Ocean Optics公司的光反射薄膜测厚仪测量得到,其厚度分别为75 nm和70 nm。NbLaO和ZnO薄膜的表面形貌采用原子力显微镜(AFM)测试。单位面积栅介质电容(Cox)利用Agilent 4284A通过测试Al/NbLaO/ITO结构的电容-频率特性和采用金相显微镜测定电极面积确定,1 MHz下Cox为126 nF/cm2。ZnO TFT样品的电特性和低频噪声(LFN)特性利用Agilent 4156C半导体精密参数测试仪、Proplus 9812B噪声分析仪及CASCAD RF-1探针台等仪器组成的测试系统,在室温无光照的普通空气环境下测试。

3 结果与讨论

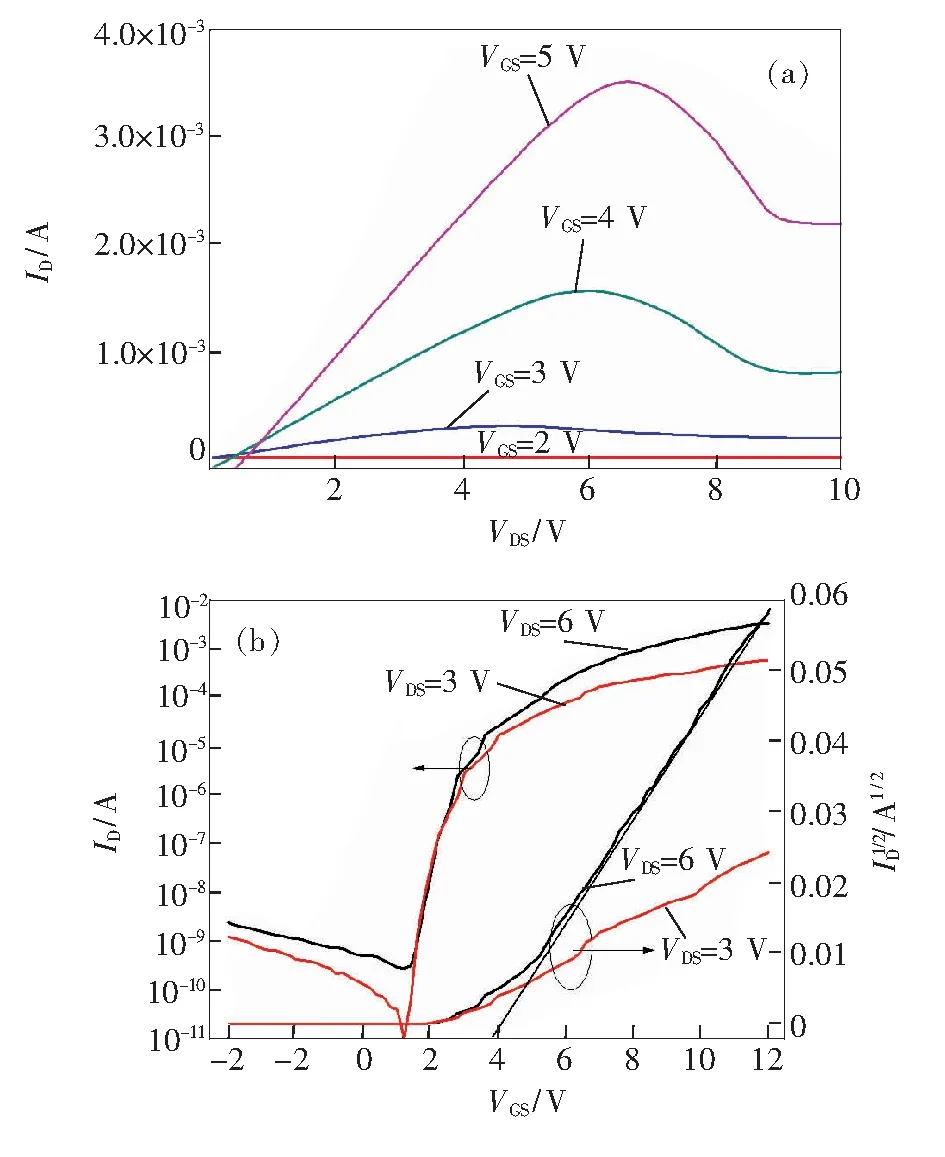

图2给出了典型的ZnO TFT器件的输出和转移特性曲线。由图2(a)可知,输出特性曲线饱和区不平坦,在进入饱和区附近呈现出明显峰值,且随着栅电压(VGS)增大,该峰值位置向右移动。当漏源电压(VDS)较小时,漏极电流(ID)随VDS的增加呈线性增大;当VDS继续增加到一定值后,ID随VDS的增加反而减小,最后趋于平坦。当VGS=5 V、VDS=10 V时,平坦区饱和漏电流高达2.2 mA。饱和区不平坦现象可以解释为:对于某一高于阈值电压的VGS,当VDS较小时,整个沟道处于强积累状态,沟道内类施主陷阱态被电子填满,此时ID随VDS呈线性增加。当VDS增加并使漏极附近沟道被夹断时,漏端半导体有源层处于耗尽状态,费米能级远离导带底,大量的类施主陷阱位于费米能级之上未被电子填充而呈正电性,具有俘获电子的能力。此时从源端注入的电子在沟道电场作用下输运至漏极耗尽区边缘,并由耗尽区强电场拉向漏极形成漏极电流过程中部分被带正电的类施主缺陷态所俘获,使得达到漏极的电子减小,从而导致ID随VDS增大反而有所减小。当VDS增加到一定值后,由于费米能级钉扎现象,此时VDS的增加并不引起漏端耗尽区带正电的类施主陷阱态增加,因此ID维持平坦。由图2(b)可知,该薄膜晶体管具有较明显的开关特性。当栅偏压加负向电压并且不断增加时,晶体管进入关断状态,最小关态电流为2.75×10-10A,且随着负栅偏压的增大,关态电流有所增加。这是由于栅偏压增大引起栅泄漏电流增加所致。当栅偏压加正向电压并不断增加时,晶体管进入开通状态,且随着栅偏压的增大,ID快速增加。对于薄膜晶体管而言,晶体管处于饱和状态时的饱和漏电流ID,sat通常可表示为

(1)

(2)

(3)

图2 ZnO TFT的输出和转移特性曲线。(a)输出特性曲线;(b) 转移特性曲线。

Fig.2 Output and transfer characteristics of ZnO TFT. (a) Output characteristics. (b) Transfer characteristics.

对于VDS=6 V的器件,SS为0.28 V/decade。

根据式(4),由SS可以提取出ZnO/NbLaO界面处界面陷阱态密度Nit为3.01×1012cm-2。

(4)

式中,k为玻耳兹曼常数,T为绝对温度,q为电子电量。

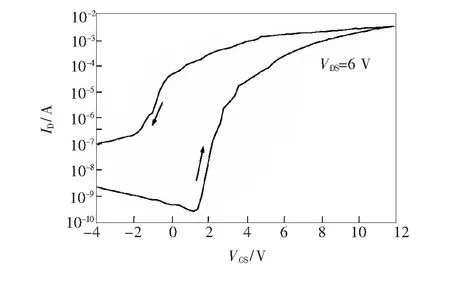

图3给出了VDS=6 V时的ZnO TFT转移特性的滞回曲线。由图3可知,转移特性存在较为明显的迟滞现象,迟滞电压约为3.6 V。在栅电压VGS从-4 V扫描至12 V(正向扫描)的过程中,转移特性曲线呈现明显的开关特性,开关电流比为1.23×107,关态电流相对较小(~3×10-10A),亚阈值摆幅较小(~0.28 V/decade);而在栅偏压再从12 V回扫至-4 V(反向扫描)的过程中,阈值电压向负方向漂移,开关特性明显退化,主要表现为关态电流比正向扫描时增加近3个数量级,从而导致开关电流比下降了近3个数量级,仅为3.35×104。这与器件内部(包括有源层体内、栅介质内部及界面)存在丰富的陷阱态相关。在正扫描过程中,有源层体内、栅介质体内及界面的陷阱态会陷阱大量的沟道电子;当反向扫描时,特别是进入关态后,被陷阱的电子会再次释放出来进入沟道而形成沟道载流子,引起关态电流显著增加,导致开关电流比明显下降。

图3 ZnO TFT转移特性的滞回曲线

Fig.3 Hysteresis curves of transfer characteristics of ZnO TFT

通常,栅介质表面粗糙度对TFT器件性能有较大影响,且随着粗糙度的增加,载流子迁移率会明显下降[14-15]。栅介质表面粗糙度对迁移率的影响主要包括3种机制:一是粗糙的栅介质与有源层界面引起陷阱态增加[16];二是粗糙度的增加易形成更大的晶粒间界[17];三是粗糙度增加会引起栅介质的表面散射增加[18]。为了进一步解释我们的ZnO TFT器件呈现出高迁移率的原因,实验中测试了NbLaO栅介质的表面形貌AFM图,如图4(a) 所示。

图4 NbLaO栅介质薄膜(a)和沉积在NbLaO栅介质上ZnO 薄膜(b)的AFM图

Fig.4 AFM images of NbLaO gate-dielectric surface (a) and ZnO active-layer surface (b)

由图4(a)可以看出,NbLaO表面非常光滑,由AFM测试系统分析可得,NbLaO薄膜表面粗糙度(rms)仅为0.216 nm,远小于Beox-Nilsen报道的具有高迁移率(>50 cm2/(V·s))ZnO TFT中Ta2O5栅介质表面粗糙度(~0.7 nm)[11],这说明光滑的NbLaO表面是导致我们的样品具有更高迁移率的重要原因。首先,光滑的栅介质表面可以减小界面陷阱,获得更高质量的沟道/栅介质界面,从而获得更高的迁移率和更小的亚阈值摆幅[17]。其次,光滑平整的栅介质表面有助于生长高质量的ZnO有源层薄膜,特别是栅介质表面的初始薄层。对于我们的顶栅底接触型器件结构,这一初始ZnO薄层是场诱导沟道的重要部分。图4(b)给出了NbLaO栅介质上沉积ZnO薄膜的AFM图,分析可得ZnO薄膜的rms为2.06 nm,平均晶粒大小为78 nm,说明这一高质量的ZnO也是导致器件具有高迁移率的原因之一。为了减小ZnO薄膜沉积过程高能粒子对栅介质与有源层界面的碰撞损伤,以获得更好的沟道/栅介质界面,我们采用较低功率(50 W)的RF溅射工艺[19]。另外,由于NbLaO薄膜制备后未从溅射反应室取出进行退火工艺,而是接着沉积ZnO有源层,因此在ZnO薄膜沉积前NbLaO表面未暴露于自然环境,避免了NbLaO表面杂质污染及水分子吸附,也有利于减小界面杂质缺陷,从而有利于提高器件的性能。

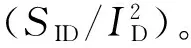

图5 ZnO TFT归一化噪声功率谱密度

(5)

4 结 论

采用磁控溅射法在室温下制备以NbLaO薄膜为栅介质的ZnO TFT。在栅电压为5 V、漏源电压为10 V时,器件的饱和漏电流高达2.2 mA,器件的有效场效应饱和迁移率高达107 cm2/(V·s),亚阈值摆幅为0.28 V/decade,开关电流比大于107。器件具有高迁移率和低亚阈值摆幅主要是因为NbLaO薄膜呈现出较低的表面粗糙度以及栅介质与ZnO有源层之间存在较低的界面陷阱态,而器件的电特性呈现较大的迟滞现象主要与室温下制备的NbLaO栅介质内部存在较高的陷阱态有关。特别值得一提的是,器件制备全过程皆在室温下进行,有望在基于塑料基底的柔性显示及可穿戴电子领域得到实际应用。

[1] HU Z J, LIAO C W, LI W J,etal.. Integrated a-Si∶H gate driver with low-level holding TFTs biased under bipolar pulses [J].IEEETrans.ElectronDev., 2015, 62(12):4044-4050.

[2] ZHENG G T, LIU P T, WU M C. Design of dual-outputs-single-stage a-Si∶H TFT gate driver for high resolution TFT-LCD application [J].J.Soc.Inform.Disp., 2016, 24(5):330-337.

[3] PARK J H, JANG G S, KIM H Y,etal.. High-performance poly-Si thin-film transistor with high-kZrTiO4gate dielectric [J].IEEEElectronDev.Lett., 2015, 36(9):920-922.

[4] 于遥, 张晶思, 陈黛黛, 等. PECVD分层结构对提高氢化非晶硅TFT迁移率的影响 [J]. 物理学报, 2013, 62(13):138501. YU Y, ZHANG J S, CHEN D D,etal.. Improving the mobility of the amorphous silicon TFT with the new stratified structure by PECVD [J].ActaPhys.Sinica, 2013, 62(13):138501. (in Chinese)

[5] ZHANG J, WU G D. Ultralow-voltage electric-double-layer oxide-based thin-film transistors with faster switching response on flexible substrates [J].Chin.Phys.Lett., 2014, 31(7):078502.

[6] 张丽, 许玲, 董承远. 非晶InGaZnO 薄膜晶体管驱动OLED 像素电路的仿真研究 [J]. 发光学报, 2014, 35(10):1264-1268. ZHANG L, XU L, DONG C Y. Simulation of amorphous-InGaZnO thin film transistors driven OLED pixel circuit [J].Chin.J.Lumin., 2014, 35(10):1264-1268. (in Chinese)

[7] WANG Y H, MA Q, ZHENG L L,etal.. Performance improvement of atomic layer-deposited ZnO/Al2O3thin-film transistors by low-temperature annealing in air [J].IEEETrans.ElectronDev., 2016, 23(5):1893-1898.

[8] ESRO M, VOURLIAS G, SOMERTON C,etal.. High-mobility ZnO thin film transistors based on solution-processed hafnium oxide gate dielectrics [J].Adv.Funct.Mater., 2015, 25(1):134-141.

[9] FORTUNATO E, PIMENTELl A, PEREIRA L,etal.. High field-effect mobility zinc oxide thin film transistors produced at room temperature [J].J.Non-Cryst.Solids, 2004, 338-340:806-809.

[10] ZHANG L, LI J, ZHANG X W,etal.. High performance ZnO-thin-film transistor with Ta2O5dielectrics fabricated at room temperature [J].Appl.Phys.Lett., 2009, 95(7):072112.

[11] BROX-NILSEN C, JIN J, LUO Y,etal.. Sputtered ZnO thin-film transistors with carrier mobility over 50 cm2/(V·s) [J].IEEETrans.ElectronDev., 2013, 60(10):3424-3428.

[12] TSUKAZAKI A, OHTOMO A, KAWASAKI M. High-mobility electronic transport in ZnO thin films [J].Appl.Phys.Lett., 2006, 88(15):152106.

[13] OKAMURA K, NIKOLOVA D, MECHAU N,etal.. Appropriate choice of channel ratio in thin-film transistors for the exact etermination of field-effect mobility [J].Appl.Phys.Lett., 2009, 94(18):183503.

[14] STEUDEL S, DE VUSSER S, DE JONGE S. Influence of the dielectric roughness on the performance of pentacene transistors [J].Appl.Phys.Lett., 2004, 85(19):4400-4402.

[15] KHAN T, VASILESKA D, THOMTON T J. Effect of interface roughness on silicon-on-insulator-metal-semiconductor field-effect transistor mobility and the device low-power high-frequency operation [J].J.Vac.Sci.Technol. B, 2005, 23(4):1782-1784.

[16] VOLKEL A R, STREET R A, KNIPP D. Carrier transport and density of state distributions in pentacene transistors [J].Phys.Rev. B, 2002, 66(19):195336.

[17] VERLAAK S, ARKHIPOV W, HEREMANS P. Modeling of transport in polycrystalline organic semiconductor films [J].Appl.Phys.Lett., 2003, 82(5):745-747.

[18] VALLETA A, MARIUCCI L, FORTUNATO G. Surface-scattering effects in polycrystalline silicon thin-film transistors [J].Appl.Phys.Lett., 2003, 82(18):3119-3121.

[19] TVAROZEK V, NOVOTNY I, SUTTA P,etal.. Influence of sputtering parameters on crystalline structure of ZnO thin films [J].ThinSolidFilms, 2007, 515(24):8756-8760.

[20] RUMYANTSEV S L, JIANG C, SAMNAKAY R,etal.. 1/fnoise characteristics of MoS2thin-film transistors: comparison of single and multilayer structures [J].IEEEElectronDev.Lett., 2015, 36(5):517-519.

刘玉荣(1968-),男,江西吉安人,博士,教授,2007年于华南理工大学获得博士学位,主要从事有机/氧化物薄膜晶体管、超声传感器等方面的研究。

E-mail: phlyr@scut.edu.cn

High Mobility ZnO Thin-film Transistor Fabricated by Sputtering at Room Temperature

LIU Yu-rong1,2*, HUANG He1, LIU Jie1

(1. School of Electronic and Information Engineering, South China University of Technology, Guangzhou 510640, China;2. National Engineering Technology Research Center for Mobile Ultrasonic Detection, South China University of Technology, Guangzhou 510640, China)

In order to reduce the operating voltage and increase the carrier mobility in zinc oxide thin-film transistor (ZnO TFT), ZnO TFTs with high-kNbLaO as gate dielectric layer were fabricated on indium tin oxide/glass substrate by radio-frequency magnetron sputtering at room temperature, and the electrical properties of the device were characterized. The fabricated ZnO TFTs exhibit excellent device performances. The saturation drain current can reach to 2.2 mA at gate voltage of 5 V and drain voltage of 10 V. The saturation mobility increases drastically up to 107 cm2/(V·s), which is one of the highest field-effect mobility values achieved in ZnO-based TFTs by room-temperature sputtering. The subthreshold swing and on-off current ratio are 0.28 V/decade and higher than 107, respectively. The relative mechanisms of high mobility, small subthreshold voltage swing and hysteresis phenomenon are discussed by analyzing the atom force microscope images of the NbLaO dielectric and ZnO active-layer film, and the low frequency noise behavior of the device.

thin-film transistor; zinc oxide; radio frequency sputtering; high mobility

1000-7032(2017)07-0917-06

2016-12-07;

2017-02-02

广东省自然科学基金(2016A030313474)资助项目 Supported by Natural Science Foundation of Guangdong Province(2016A030313474)

TN321+.5; O472+.4

A

10.3788/fgxb20173807.0917

*Corresponding Author, E-mail: phlyr@scut.edu.cn