高速电路系统设计中的端接匹配分析与选择

黄世瑜

(四川职业技术学院电子电气工程系,四川遂宁629000)

高速电路系统设计中的端接匹配分析与选择

黄世瑜

(四川职业技术学院电子电气工程系,四川遂宁629000)

端接匹配是影响电磁兼容性的一个非常重要的因素.本文就电磁环境的组成、常见的端接匹配电路模型进行测试、分析比较,在不同系统电路结构中通过合理的选择端接匹配方式,达到整机系统线路的阻抗匹配,提高高速电路系统抗干扰能力.

端接;电磁兼容性;印刷线路板;匹配

在高速电子系统电路设计中,电子线路系统的电气特性设计重点为正时、信号质量与电磁干扰(El ect ro M a g net i c I nter ference,简称E M I)的控制.当前,电子系统技术向高集成度、高密度、小型化、低功耗方向发展,就要求电子线路印刷板(P r i nte d C i rcu i t B o a r d,简称PC B)的密度越来越高、线路板层数越来越多,因此电子线路印刷板的相关技术的水平也越来越高,电子线路印刷板设计的好坏将直接影响高速电子系统的抗干扰能力.为实现高速电路系统性能稳定性与可靠性达到最佳的目的,在线路板系统设计中,在要求线路板合理的布局、布线以及选用优化选用合适的元器件选择之外,极间信号的端接匹配也是影响电磁兼容性(El ect ro ma g net i c C o mpa t i b i l i t y,简称E M C)的一个重要因素.合理的选用端接匹配电路及元器件参数达到高速电子系统电路的极间阻抗匹配,是减轻反射信号影响,提高电路系统抗干扰能力的一种有效可行的手段.

1 电磁环境的组成

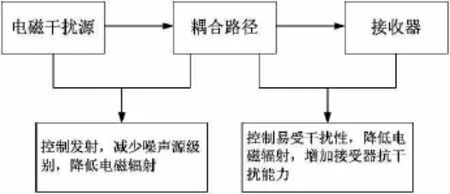

电磁环境是指给定场所存在的电磁现象的总和,是环境中普遍存在的一种电磁感应干扰现象.电磁环境包含空间、时间和频谱三个要素.在电子系统电路中,一个简单的电磁环境结构主要由电磁干扰源、耦合路径、接收器三个部分组成,如图1所示.

电磁干扰源种类繁多,在高速电子系统中干扰来源可分为自然干扰源和人为干扰源.自然干扰源主要包含:大气噪声干扰,如太阳黑子活动期产生的黑子爆发;如雷电等自然现象产生的火花放电;静电放电,在静电放电过程中形成强大的瞬间电流和电磁脉冲形成干扰.人为干扰源指而电子电气系统设备产生的电磁干扰,人为干扰源主要包含:无线电发射设备,如广播系统、通信系统、电视系统、雷达系统等;工业、医疗(I S M)设备等,如高频电焊机、感应加热设备;机电控制设备,如继电器、伺服电机;电网干扰,如工频电网的电磁场和大地漏电流产生的干扰.这些干扰源在高速系统电路中通过电源线路、寄生参数和杂散的电磁场耦合,会产生大量的电磁干扰,将影响电子系统设备的正常工作.

图1 电磁环境模型的组成

耦合路径是指在电路系统中部分或全部电磁能量从规定源电路传输到另一接收电路或装置所经由的路径.在电路系统中耦合路径主要为传导耦合、磁场耦合、电场耦合、辐射耦合、静电放电等多种形式.电子系统中极间信号传导常见的耦合路径方式是辐射耦合路径与传导耦合路径.其中,在高速系统电路辐射耦合路径是一种最为普遍耦合路径,在高频、高速系统中应尽量的克服;低速系统电路中传导耦合路径为主要的一种表现形式,在低频、低速系统电路中电路优化设计时主要应主要考虑的对象.当然,在高速系统电路综合设计时,信号也能够通过导体传导耦合在电路系统级间建立传导耦合路径,由于导线、元器件引脚、焊点、过孔等处存在分布电容、电感及直流损耗电阻分布参量,在低速系统中这些分布参量可以忽略不计,而在高速系统中分布参量将影响电路的稳定性与可靠性,导致系统工作不正常,形成R L C串并联网络回路,将接受环境噪声并将它传递到电路的其余部分,产生信号干扰.

由于有传导、磁场、电场、辐射等耦合现象存在,在高速电路系统中所有功能电路、器件或模块电路都可以接收到电磁干扰信号,成为电磁干扰接收器.例如在数字系统电路中模拟信号处理电路、系统输入输出控制电路和公共电源、逻辑时钟信号、系统总线等处容易受到电磁干扰的影响.为满足电磁兼容性标准,需将电路系统中辐射的能量减到最小,提高系统抗干扰能力,增强其对辐射的易感性.

2 端接匹配

当信号在传输线中传播时,电场就随之建立,信号的传输速度取决于其在信号路径与返回路径周围材料中的交变电场和磁场的建立速度和传播速度,电路在高速运行时,减小因端接不当形成的信号反馈,使电路产生阻尼振荡,影响电路的稳定性,引起E M I问题,要求在电路模块前后级间进行阻抗匹配,减少这些非预期的结果.

2.1 串行端接匹配

串行端接(S er i es/S ource T er mi n a t i on)是在低速系统电路中最为常见的一种端接阻抗匹配方式.串行端接匹配方法是在系统电路中串联插入一只阻抗匹配电阻RS来实现匹配源极驱动器(信号源)输出阻抗与负载(本级)输入阻抗的阻抗,使源极驱动器与负载实现阻抗匹配,电路模型如图2所示.

为达到最佳串行端接匹配效果,在使用串行端接匹配方式时,在高速PC B线路板布线过程中,要求匹配电阻RS应尽量靠近源极驱动器端,匹配电阻阻值一般为10Ω到75Ω;匹配电阻阻值加上前级信号源的输出阻抗应大于等于传输线阻抗,使电路工作在微过阻尼状态,可以防止电路形成自激振荡.

在图2中,源极驱动器输出阻抗ZS、PC B线路板布线的轨迹阻抗Z0、阻抗匹配电阻RS形成串行端接匹配方式.为实现最佳串行端接匹配效果,输出阻抗ZS、轨迹阻抗Z0与阻抗匹配电阻RS的关系为:RS+ZS>Z0.

RS的值计算公式为RS=(Z0-ZS),取值为实数值.在工程应用中RS一般取值为15Ω~75Ω.

图2 串行端接匹配模型

串行端接匹配电路的优点是电路结构简单,插入电阻阻值较小,系统整机损耗较低.由于串联电阻RS,在高速状态时,信号波形上升趋势将趋于平缓,上升或下降时间增长,传输中降低信号的过冲量,信号极间反馈量减少,切断了辐射耦合路径使电路系统电磁辐射干扰降低,增加了信号的传输质量,同时当驱动高容性负载时可提供限流作用,较小了信号的冲击响应,起到了减小噪声的目的.

串行端接匹配方式的缺点是信号的上升或下降增长了,由于RS的分压作用,在极间匹配的前级(源极驱动器)出现半波幅度的分压,该信号会沿传输路径延迟一个时间量传递到负载端,持续时间为2上升或下降时间,信号源端到终端的传输延迟,在高速系统电路中,此传输延迟时间内会导致系统呈现竞争冒险现象,使输出逻辑混乱.因而串行端接匹配方式只适合用于低速系统电路中.

在使用串行端接匹配时需要根据电路的工作形态合理的选择,例如在串行端接匹配对于TT L或C M OS驱动电路系统,由于数字逻辑信号在高电平与及低电平状态时,其输出阻抗是不一致的,不能简单的得知输入输出阻抗,插入串行端接匹配电阻RS值不能有效的量化,很难起到端接匹配的目的;而对于在低速系统电路或总线型负载时,串行端接匹配由于电路结构简单,是一种最佳端接匹配方式.

2.2 并行端接匹配

并行端接匹配又称为直流(D C)端接匹配方式,在系统极间匹配电路系统连接中,当负载端模块电路的输入阻抗较大时,在负载模块的输入端并联一只匹配电阻RP(交流通路并联,即RP可接电源或接地)形成并行端接匹配方式,如图3所示.

并行端接匹配电路中,要求匹配电阻RP的阻值等于PC B线路板信号传输导线的特征阻抗;同时,并行端接电阻要尽量靠近负载端的位置加上拉和/或下拉阻抗,电路模型如图3所示.

图3 并行端接模型

在并行端接匹配电路中由于附加一个并联端接匹配电阻RP,这样RP∥ZL与轨迹阻抗Z0相匹配.为满足极间前后级门限电压要求,源极驱动器的输出端必须能够提供足够高的高电平.如果并联端接电阻RP的值太小了,在输出为高电平状态时,端接电路消耗的功率过大,导致后级输入电压过低,电路工作不可靠,因此在C M OS与TT L设计中这种设计一般不采用并行端接.

并行匹配的优点可用于分布负载,并联端接电阻RP接电源作上拉连接方式时,可提高源极驱动器的驱动能力;当并联端接电阻RP接地作下拉连接方式时,能提高对电流的吸收能力,并能够吸收传输波以消除反射;并联匹配的缺点是需连接电源或地,在信号传输中额外增加电路的功耗,同时降低系统的噪声容限.

2.3 RC端接匹配

R C端接匹配又称交流(AC)端接匹配,R C端接匹配是在并行端接匹配的基础上降级电路损耗,提升系统电路的噪声容限,使RP不直接接地,串联一颗电容后接地.同时由于电容的存在隔离了直流,减小了直流功耗,同时具有并行端接的优点,电路模型如图4所示.

R C端接匹配在并行端接匹配上增加了1只隔直电容元件C1,R C端接匹配和并行端接匹配方法中一样,R用于提供匹配传输线的阻抗Z0,C1为R提供驱动电流并实现隔直滤波.R和C1的值由轨迹阻抗Z0、环路传输延迟Tpd和负载的输入分流电容(或等效电容)Cd确定.时间常数τ=R C=3×Tpd,其中,Z0=R∥ZL,C=C1∥Cd.

图4 端接电路模型

通过上述分析,R C端接匹配中R应等于轨迹阻抗Z0,同时时间常数τ为传输延时时间的2倍,在工程应用中而串接隔直电容C1容量一般取值为20p F~600p F.

R C端接匹配结合了并行端接匹配的优点,同时也克服了并行端接匹配噪声容限低、功耗大的缺点,可在分布负载及总线布线中使用;R C端接匹配的缺点是在高速系统电路中降低了信号的传输速率.

2.4 戴维宁并行端接匹配

戴维宁型并行端接匹配方式又称为电阻分压器端接匹配,在并行端接匹配方式的基础上增加1只电阻,其中,电阻R1结电源构成上拉形式,电阻R2接地,构成下拉形式,电路模型如图5所示.通过上拉电阻和下拉电阻吸收反射,这样就使逻辑高电平和逻辑低电平与目标负载相符.在戴维宁并行端接匹配结构中,R1和R2的值由轨迹阻抗Z0=R1∥R2决定.要求R1+R2+ZL的值要保证最大电流不能超过源驱动电路容量.此端接通常是为了获得最快的电路性能和驱动分布而采用的.

图5 戴维宁并行端接模型

戴维宁匹配的优点能够全部吸收传输波以消除反射,在驱动多扇出时,负载可经分支短线沿线分布,尤其适合用于总线使用;戴维宁匹配的缺点是此端接方案降低了对源端器件驱动能力的要求,直流功耗较大,同时会降低系统噪声容限.

2.5 二极管端接匹配

二极管端接匹配与戴维宁并行端接匹配类似,将戴维宁并行端接匹配中的电阻更换为二极管,电路模型如图6所示,在二极管端接电路中用二极管D1和D2替换了戴维宁并行端接电路中的R1和R2以降低损耗.D1和D2用来限制来自负载的过多信号反射量.

图6 二极管端接电路模型

对这种端接方法而言,选择快速开关二极管和肖特基二极管等高频特性响应好,管压降低的二极管.这种端接方法的优点在于不用考虑轨迹阻抗的Z0值,而且还可以和其他类型的端接方法结合混合使用.

3 结语

在上述中分别就串行端接、并行端接、端接、戴维宁并行端接、二极管端接5中常见端接方法进行了相应的分析,每种端接方法都有各自的优缺点,如表1所示.在表中给出了一些信号端接方法的概要.在实际的电路中,我们要根据电路的不同的电路结构特点及电路应用范围选用合适的端接匹配方式.在工程中应该具体问题具体分析,灵活的运用各种设计规则和技巧,提升电路的稳定性与可靠性,提高高速电路系统抗干扰能力.

表1 常见信号端接方法比较

参考文献:

[1]杨洪军,刘永亮.信号完整性设计中的端接匹配技术[J].四川理工学院学报(自然科学版),2008,21(2).

[2]李朝辉.高速电路中的阻抗匹配与端接技术[J].微处理机,2007,(3):99-101.

[3]陈思思.信号完整性中的串扰分析[J].武汉理工大学学报(信息与管理工程版),2005,(05).

[4]杨华,陈少昌.高速数字电路PC B中串扰问题的研究与仿真[J].电光与控制,2012,(03).

责任编辑:张隆辉

TN41

A

1672-2094(2017)01-0157-05

2016-10-10

黄世瑜(1978-),男,四川广安人,四川职业技术学院副教授,工程硕士.研究方向:电子设计自动化.