大规模数字电路系统可测性设计技术研究

张 昊

(西南电子技术研究所,四川 成都 610000)

大规模数字电路系统可测性设计技术研究

张 昊

(西南电子技术研究所,四川 成都 610000)

为满足大规模数字电路系统测试、故障诊断的需要,可测性(DFT)设计已成为大规模数字电路系统设计中不可或缺的重要组成部分。结合边界扫描测试原理和大规模数字电路系统的主要特点,研究DFT实现的技术途径,并将其用于某大规模数字电路系统的设计中。实现了该大规模数字电路系统的一键式互连故障诊断及可扫描网络准确定位,有效简化了测试复杂度。

大规模数字电路测试;边界扫描;故障诊断

0 引言

随着微电子、计算机领域新技术和新工艺的迅猛发展,数字电路系统处理能力越来越强,其电路规模越来越大,系统中采用的DSP、PPC、FPGA等大规模数字芯片越来越多[1-3]。这类芯片大多采用BGA封装、引脚数量多且间距小,使得数字系统上可供测试的节点间距越来越小。传统示波器、逻辑分析仪等物理探针能够接触到的管脚越来越少,造成系统可测性急剧下降,测试复杂度急剧上升,为系统调试、故障检测带来巨大困难,尤其不利于大批量生产及检测。

因此,提高系统的可测试性、简化测试步骤是这类大规模数字电路设计过程中需要考虑的重要问题。而可测试性的提高必须在系统硬件电路设计阶段就将测试性问题考虑进去。文献[4]、[5]中采用的设计方法均是直接利用单个器件的边界扫描链进行可测性设计和测试,没有对整个系统的扫描链路进行统一管理和规划,对于提供系统的可测性和故障覆盖率的提高具有一定局限性。本文结合大规模数字电路系统的特点,重点研究基于边界扫描原理的结构性可测性设计(DFT)在大规模数字系统硬件设计中的实现方法。

1 边界扫描测试原理

1.1 边界扫描标准

IEEE1149.1[6]边界扫描标准是IEEE组织和JTAG组织于1990年共同推出的,目前该标准已成为数字集成电路与系统的主流测试技术。

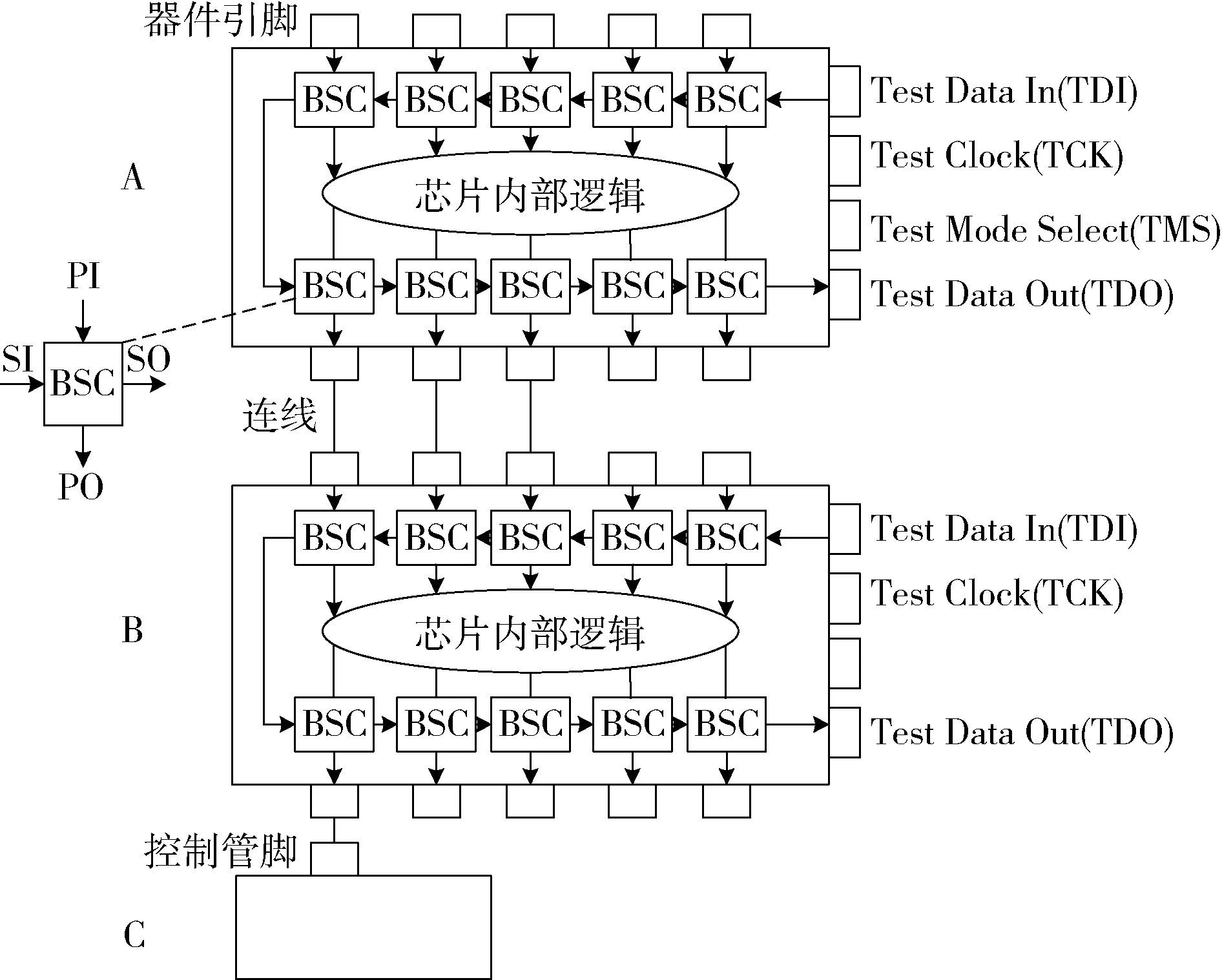

边界扫描标准仅使用4根或5根边界扫描测试总线(TMS、TCK、TRST、TDI、TDO)而不必借助针床、示波器等其他设备即可以实现对电路的测试。它不仅能测试符合IEEE1149.1标准的数字芯片的输入/输出管脚状态,还能测试这类芯片内部工作情况及芯片相关引脚的开路和断路故障,从而实现高精度的故障定位。其原理图如图1所示。

图1 数字芯片边界扫描测试原理图

边界扫描测试标准在数字芯片管脚和芯片内部逻辑之间(即集成电路的边缘)增加了附加的扫描单元(BSC),通过边界扫描单元控制和观察芯片引脚的状态。符合IEEE1149.1标准的数字芯片均可以在普通工作模式和边界扫描模式之间自由切换。如图1所示,在边界扫描模式下各BSC以串行方式连接成扫描链,可实现测试向量的加载、采集以及其他数字芯片引脚的控制。可以通过输入端(TDI)将测试向量以串行移位方式输入(由SI移位到SO),设定芯片A的管脚状态,并从与之相连的芯片B管脚采集该响应;也可以通过设定芯片B的管脚状态,间接对芯片C的管脚进行控制,最后从输出端(TDO)将系统的测试响应串行输出到主控计算机,进行数据分析与处理,从而形成电路故障判据。在正常工作期间,这些附加的移位寄存器单元会直接被旁通(PI与PO直连),达到不影响数字芯片正常工作的目的。

1.2 测试原理

利用上述原理,就可以通过边界扫描单元,将指定的状态从测试数据输入端口(TDI)串行移位到某个器件的输出引脚,这时可在与之相连器件的输入引脚上采集到响应,再通过输出端口(TDO)将该响应与理论值进行对比,从而实现芯片之间的互连诊断;还可通过扫描路径串行移位将测试向量施加到某芯片的核心逻辑输入端(PO),在输出单元(PI)捕获其核心逻辑的响应向量,以检测芯片的内部故障。所有测试方法均围绕边界扫描单元,因此,这种测试方法又被称为边界扫描测试技术(Boundary-Scan Test,BST)。

边界扫描测试技术虽然大多用于对纯数字电路进行故障诊断,但在部分情况下还可用于混合数字电路的测试。主要通过边界扫描技术控制数字芯片管脚状态,对混合型芯片施加激励或采集响应实现。

大规模数字电路系统大量采用了符合IEEE1149.1边界扫描测试规范的数字芯片,如PPC、DSP、FPGA、TSI等,并且这类数字芯片大多采用BGA封装使得物理探针无法直接接触到管脚。这一特点为边界扫描测试技术在大规模数字电路故障诊断中的应用提供了前提条件。然而,在大规模数字电路系统的硬件电路设计过程中,如果不考虑结构性DFT设计,就难以完全发挥边界扫描测试技术在这类系统故障诊断中的作用而达到最终简化测试步骤的目的。

2 可测性设计的实现

所谓可测试性(DFT)设计,就是在进行电路和系统设计的同时,考虑系统的测试问题。这里讨论的可测性设计问题主要针对结构性测试。结构性边界扫描测试是指通过大规模数字系统提供的IEEE1149.1测试总线实现数字芯片的互连故障诊断测试。

基于边界扫描测试的可测性设计,首先必须考虑的是边界扫描链路的连接方式、管理方法;其次,满足IEEE1149.1标准的边界扫描器件,如PPC、DSP、FPGA等,可工作于正常模式和边界扫描模式,但某些芯片的边界扫描测试引脚并没有完全按照IEEE1149.1进行设计,所以,在电路设计阶段还应当考虑工作模式的切换方法,避免影响电路正常工作。此外,为进一步提高电路故障测试覆盖率,还应当考虑非边界扫描器件的引脚测试问题,如BUFFER、TRANCEIVER、RAM等。

2.1 边界扫描链组织方式

扫描链路是边界扫描测试的基础,边界扫描链器件连接方式有三种:串行方式、并行方式和独立路径方式。串行方式是所有器件的TMS管脚和TCK管脚并联在一起,前一级的TDO输出管脚接到下一级的TDI输入管脚的测试总线连接方式;并行方式是两个或多个串行方式连接的JTAG扫描链并行连接,串行扫描链的TMS信号各自独立,确保只有一个串行扫描链在指定的时间内有扫描数据输出;独立路径方式是所有器件的TMS和TCK连在一起,而每个器件的TDI和TDO相互独立的测试总线连接方式。

2.1.1 串行边界扫描链

串行方式只需要一个JTAG接口即可连接到边界扫描控制器上,并且不需要在模块上增加额外电路,适合于边界扫描器件、功能模块较少且器件之间连接关系较简单的系统。在系统级测试中,所有兼容IEEE1149.1数字芯片的边界扫描链是构造一条完整的测试通路的最好的链。采用这种串联方式可实现最简单的系统级边界扫描测试环路,如图2所示。

图2 串行方式连接的边界扫描链

串行连接方式主要缺点是系统如果有空槽或链路中有芯片损坏,整个边界扫描链路就会断开,导致扫描链路瘫痪,系统级边界扫描测试也随之瘫痪。此外,当某些边界扫描器件需要反复访问时,边界扫描单元串行移位操作特别繁琐。比如,对较长扫描链上的某个可编程器件进行编程时,比通常情况下需要执行更多次的边界扫描操作。有时串行移位所需要的额外数据位边界扫描软件无法自动产生,而手动修改特别耗时也容易出错。因此,这种方式难以用在边界扫描器件较多、系统较复杂的场合。

2.1.2 并行边界扫描链

当模块上边界扫描器件较多时,将所有边界扫描器件串联到一起的方法虽然有助于简化电路设计,但正如前文所述,较长的链路不便于边界扫描测试软件管理以及器件编程。更好的方法是将链路分割分组管理,采用并联的连接方式。这种连接方式通过路由芯片间接对分支链路进行管理,极大地简化了串行移位操作,增加了扫描链路的灵活性。

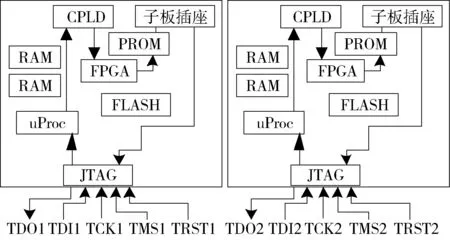

并行边界扫描链具有较强健壮性,各个模块既可独立进行模块级边界扫描测试,也可互相配合进行系统级边界扫描测试。如图3所示,每个通用处理模块的扫描链路并联在测试总线上的,即使某个模块损坏,也不会影响到其余模块的测试工作。实现方法是在每个通用处理模块上增加一片边界扫描路由芯片,把模块内边界扫描链分成多个区段,每个区段都按照规则分配独立的边界扫描链。测试系统通过每个模块上的边界扫描路由芯片,管理通用处理模块上的多个扫描链进行边界扫描测试。

图3 并联方式的连接的边界扫描链

2.1.3 独立的边界扫描链

独立的边界扫描链路组织方式为每个模块提供单独的边界扫描测试接口和测试总线,如图4所示。这种连接方式通过各个模块的边界扫描测试接口即可实现模块级边界扫描测试。但是,由于各个模块的边界扫描链路相互隔开,相互配合实现系统级边界扫描测试难度较高,操作较复杂,并且随着模块数量的增加,背板需要更多的空间用于测试总线,因此这种连接方式不适合规模较大的复杂系统。

图4 独立的边界扫描链

2.2 兼容性设计

通过一定的方法如边界扫描使能管脚,支持边界扫描测试的数字芯片能实现边界扫描测试和正常工作模式的切换。为不影响模块正常工作,在通用处理模块设计阶段,应根据不同的数字芯片,进行模块正常工作模式和边界扫描模式的兼容性设计。

2.2.1 JTAG引脚的兼容性设计

某些数字芯片在传统的5个JTAG引脚的基础上增加了额外的引脚,对边界扫描进行控制。这时需要对这些数字芯片的JTAG引脚进行兼容性设计,其实质就是对额外的引脚进行处理。例如,TI公司DSP的JTAG引脚在IEEE1149.1标准的基础上增加了EMU0和EMU1脚。EMU0和EMU1在上拉时为正常工作和仿真调试状态,下拉时为JTAG边界扫描状态。在DSP正常工作和仿真调试时,两个信号需做上拉处理,使JTAG接口无效,而在JTAG测试时则需要驱动其为低电平。部分边界扫描器件还有边界扫描功能使能管脚,如PEB20320的65脚(TEST),AMD的ELANSC400的Y11(BNDSCNEN),该管脚为高时,方可使能边界扫描功能。对于此类芯片,要按照芯片手册,并根据实际需要进行上拉电阻或者下拉电阻处理。

如果器件的BSDL文件中要求器件的某些管脚在进行JTAG接口测试时处于特定的逻辑电平,则这些管脚必须按照BSDL文件中的要求设置成特定的逻辑电平。这些要求一般都包含在BSDL文件实体部分(Entity)的兼容使能描述中。按照IEEE 1149.1标准的规定,兼容使能描述格式如下:

attribute COMPLIANCE_PATTERNS of

例如在xc3s200an_ft256的BSDL文件中有这样的描述:

-- Compliance-Enable Description

attribute COMPLIANCE_PATTERNS of

XC3S200AN_FT256 : entity is

"(PROG_B, PUDC_B) (10)";

则PROG_B、PUDC_B两个管脚在进行边界扫描测试时必须使能为"10"。

2.2.2 BSDL文件的兼容性设计

如果要在FPGA配置完成后对其进行边界扫描测试,则需要按照芯片引脚实际状态修改其默认的BSDL文件。对于XILINX公司的XC4000E/EX/XL/XLA、XC5200、Spartan、SpartanXL等系列的FPGA,还需要在逻辑设计中加入边界扫描功能模块,否则芯片只在配置之前可进行边界扫描测试。

3 簇测试设计

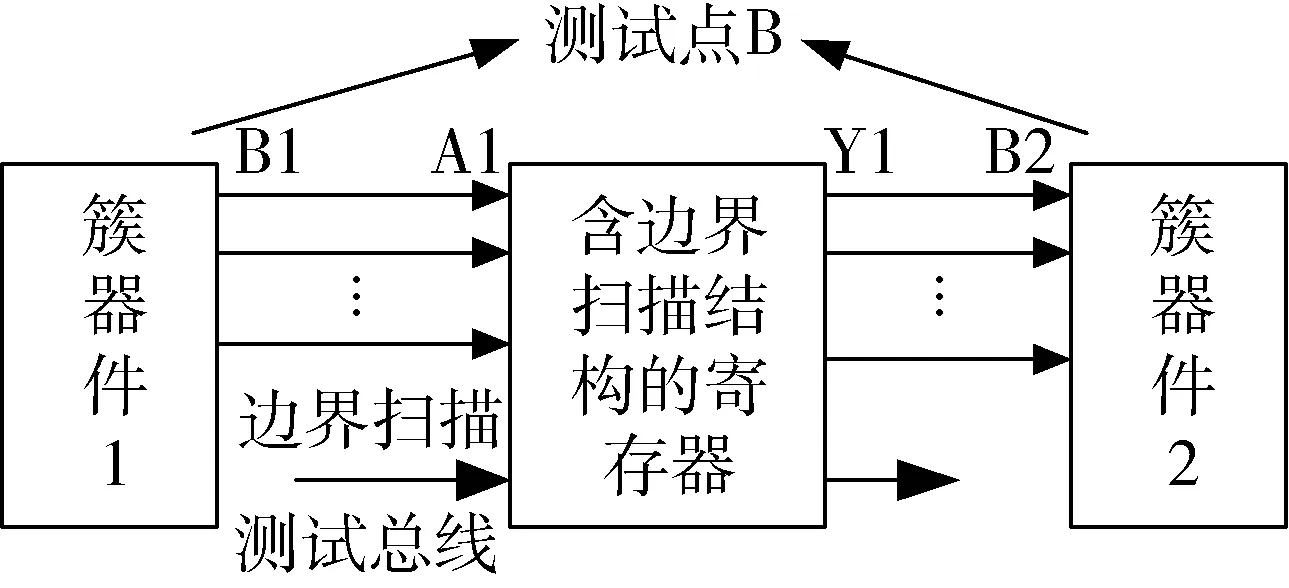

除了兼容于IEEE1149.1标准的边界扫描数字芯片,通用处理模块还包括缓冲器、传输器、电平转换器等数字芯片,这类非边界扫描器件被统称为“簇(Cluster)”。簇测试一般采用“虚拟测试通道”的方法,其基本思想是:利用具有边界扫描机制的器件为不具有边界扫描机制的器件提供测试通道,实现测试向量的加载和测试响应的读取,测试原理如图5所示。

图5 簇测试原理

图5中边界扫描器件与簇器件1、2相连,通过边界扫描测试总线可间接在测试点B处读取簇器件1的输出,对簇器件2施加激励,并在其余电路配合下实现簇器件1和2的簇测试。

由于边界扫描软件无法获得与边界扫描控制器或被观测网表相连的簇器件性质,因此,还必须为软件提供这些器件的模型,即簇模型。簇模型提供了非边界扫描器件的一些基本信息。例如,非边界扫描器件的某个引脚是输入、输出、三态还是双向的。对于具有三态和双向性质的引脚,在簇模型中应该提供控制引脚状态的方法,便于边界扫描控制器在必要的时候改变器件的引脚状态来避免总线竞争。

簇模型的引入还可间接增加电路故障测试覆盖率。某些特别的非边界扫描器件,如串联电阻或驱动器,具有直通特性,因此器件的输入逻辑值可以不变地输出。根据这个特点,可利用簇模型将两个分开的网表合并为一个连续的网表,达到降低网表规模、增加测试覆盖率的目的。

4 实验结果

将上述可测性设计方法用于某大规模数字系统的设计中,该系统由多个数字模块构成,各个模块通过背板总线互联,模块内部大量采用了FPGA、DSP、PPC等满足边界扫描标准的数字芯片,边界扫描链路拓扑结构采用并行扫描链,各个模块的边界扫描链路并联到背板的边界扫描测试总线上。

利用边界扫描测试系统对该系统进行互联故障诊断测试。边界扫描测试系统由图6所示三个部分构成,分别为运行在主控计算机上的边界扫描测试软件、边界扫描控制器以及待测系统。

图6 边界扫描测试系统

表1是采用DFT前后,故障覆盖率、定位精度等指标的对比。由表1可知,采用该技术后,系统可测试性大幅提高。采用该技术前,系统内部的边界扫描链路没有进行一定的组织,使得各个支持边界扫描的数字芯片之间无法进行协同扫描,导致某些管脚无法进行读写对比。由于DDR等存储芯片均被当做普通器件,通过控制与之相连的数字芯片的边界扫描寄存器,产生测试序列,选取地址并进行读写内容校验即可,所以采用通用测试程序即可完成存储器测试。采用该技术前,每个模块必须取下对每个链路进行单独测量,而改进过后无需取下模块,通过背板的测试总线即可实现所有模块的诊断。

表1 测量结果对比

为验证采用DFT技术后的待测系统可利用边界扫描测试系统实现管脚级故障定位的精度,将DFT设计后的待测系统中某个模块的DSP与FPGA之间的某条互连线通过跳线设置为短路,利用边界扫描系统进行测试,故障定位图如图7所示,图7中十字标注出来的位置即为短路管脚,与实际情况相符。

5 结论

大规模数字电路结构复杂、集成度高。其采用的数字芯片间距小、物理探针测试点少,调试、故障诊断难度大、复杂度高。得益于IEEE1149.1兼容的这类数字芯片,边界扫描测试技术在提高系统可测性、简化系统测试方面具有较大优势。该技术与系统可测性设计(DFT)技术配合,可搭建结构简单、诊断精度高的故障测试系统。本文分别从扫描链路结构选择、器件建模方法、模块兼容性设计几

图7 模块管脚故障定位图

个方面研究了超大规模数字电路的结构性可测性(DFT)设计实现方法,并在某大规模数字系统中成功应用了该技术,实现了一键式互连故障诊断及可扫描网络故障精确定位。该技术对边界扫描测试技术在大规模数字电路故障测试中应用具有一定的指导作用。

[1] 邵龙,刘金山. 基于TMS320C6455的大尺寸非连续代码加载方法[J].电子技术应用,2012,38(11):26-27.

[2] 钟瑜,陈颖,卢建川.新一代航空数据链端机的SCA架构设计[J].电讯技术,2012,52(4):447-451.

[3] 陈颖.从复杂系统观点看模块级综合集成航空电子结构[J].电讯技术,2009,49(4):98-102.

[4] 苏波.基于边界扫描的混合信号电路可测性结构设计[J].电子技术应用,2012,38(10):68-71.

[5] 陈圣俭,徐磊,陈健.基于FPGA的嵌入式边界扫描总线控制系统设计[J].计算机测量与控制,2008,16(2): 159-162.

[6] IEEE Std 1149.1-1990.Test access port and boundary-scan architecture[S].2001.

Research of the design for test technology in large scale digital system

Zhang Hao

(Electronic Technology Research Institute of Southwest, Chengdu 610000, China)

To satisfy the needs of large scale digital system test and fault diagnose, the design for test (DFT) technology has become an indispensable and important part of digital system design. Based on the boundary scan principle and the main characteristic of large scale digital system, the implementation of DFT in the actual system was researched. Finally, it proved that the interconnect faults diagnose can be implemented by one key after the DFT was applied, and the interconnect faults can be located exactly. The test complexity is reduced effectively.

large scale digital system test; boundary scan; fault diagnose

TP216

A

10.19358/j.issn.1674- 7720.2017.02.010

张昊.大规模数字电路系统可测性设计技术研究[J].微型机与应用,2017,36(2):28-31,36.

2016-07-27)

张昊(1981-),男,博士研究生,工程师,主要研究方向:大规模数字电路系统测试、大规模数字系统综合化设计、高速AD采样。